当前位置:网站首页>Principles of microcomputer Chapter 6 notes arrangement

Principles of microcomputer Chapter 6 notes arrangement

2022-06-23 18:57:00 【Bachuan Xiaoxiaosheng】

Command system

Machine instruction set

Command word

A string of bits representing a particular instruction

contain

- opcode

- Operands ( There may be more than one )

- Operand address

Need to point out that

- Operation type

- Operand type

- Addressing mode

T32

And then there is 16 Bit instructions have 32 Bit instruction , Half word alignment ,32 Bit instruction two and a half words ,16 One place , Pass the half word maximum 5 Bit discrimination

Assembly syntax

< o p c o d e > [ c o n d ] [ q ] [ S ] < R d > < R n > [ , O p r a n d 2 ] <opcode>[cond][q][S]<Rd><Rn>[,Oprand2] <opcode>[cond][q][S]<Rd><Rn>[,Oprand2]

among <> Mandatory [] Optional

- opcode: Mnemonic , Describe the type of operation

- cond: Condition code

- q: Width selection

- N-16

- W-32

- S: Automatically update after adding APSR Flag bit value

- Rd, Target operands , register

- Rn, First source operand , register

- Oprand2: Second source operand , Register or immediate

Condition execution

APSR

- N negative

- Z zero

- C carry

- V overflow

- Q saturated

- GE be used for DSP Expand

Condition code

- EQ be equal to

- NE It's not equal to

- CS carry

- CC Carry to zero

- MI negative

- PL Integer or zero

- VS overflow

- VC No overflow

- HI No sign greater than

- LS Unsigned less than or equal to

- GE Signed greater than or equal to

- LT Signed less than

- LT Signed less than

- GT There is a sign greater than

- LE Unsigned less than or equal to

- AL Unconditional

Mnemonic symbol

- ADD

- LDM Store multiple... Into multiple registers 32 Bit value

- LDR take 32 The bit value is stored in the register

- MOV

- STM Store multiple register values into memory

- STR The of a register 32 The number of bits is stored in memory

- SUB

IT Instructions

Yes

- IT

- ITT

- ITE

- ITTE

- ITTEE

Addressing mode

Operand addressing

Data addressing

Used to determine the address of the operand in the current instruction

Command addressing

Determine the next instruction address

Can be divided into

| Operand position | Addressing mode |

|---|---|

| In the instruction | Count now |

| register | register |

| Register displacement | |

| Memory data area | Register indirect |

| Register Offset | |

| Front index | |

| Post indexing | |

| Multiple registers | |

| Stack | |

| Memory code area | PC Relative addressing |

Immediate addressing

The operand is contained in the instruction , Fetching an instruction fetches the operand

Register addressing

Register direct addressing , Make the value in the register an operand

Register indirection

The register value is the operand address , The operand itself is in memory

Register shift addressing

ARM specific , The register is addressed to the operand and shifted to the real operand

Register offset addressing

The operand address is obtained by adding the value stored in the register and the address offset given by the instruction

This register is the base register , The given offset has

- Count now

- register

- Register shift

Pre indexed addressing

Automatically add the base address and offset to form the operand address and write it back to the register , Occurs before addressing , So it is called pre indexing

It is good for looping statements

Post indexing

Occurs after addressing

Multi register addressing

Some instructions can load contiguous storage areas into multiple registers

- LDM{addr_mode}{!},

Rn Is the base register ,{!} Indicates that the modified address needs to be written back to the base address register ,{addr_mode} Optional I( Increasing )/D( Decline ) and A( After taking the value )/B( Before value )

- STM Write registers to memory

Stack addressing

Replace the base address in multi register addressing with stack pointer register SP, And add {!}

Note that it is full decreasing

PC Relative addressing

Short for relative addressing

With PC Value is base address , The address label in the instruction is offset , Add the two together

Cortex-M3/M4 Instruction set

Data transfer instructions in the processor

Register to register

General registers and special registers

Count to register immediately

Memory access instructions

This special exam will be given , There are too many instructions , skip

ah , sorry , The following is all about how to use instructions , skip , Next chapter

边栏推荐

猜你喜欢

What does logistics service and management mainly learn

Know Chuangyu: content oriented, ai+ artificial empowerment

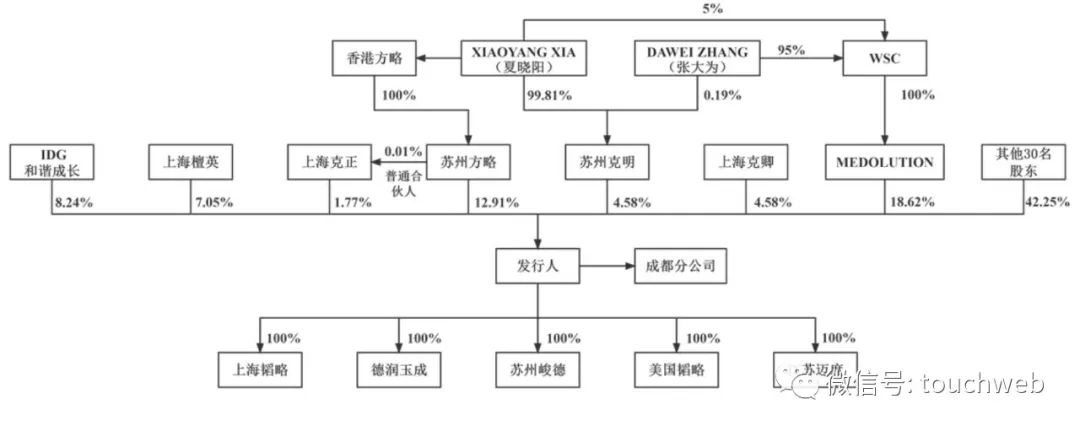

韬略生物冲刺科创板:年亏损过亿 实控人张大为夫妇为美国籍

![Jerry's broadcast MP3 prompt sound function [chapter]](/img/25/58c0f15a6fb2449ac505a06bb15887.png)

Jerry's broadcast MP3 prompt sound function [chapter]

杰理之串口设置好以后打印乱码,内部晶振没有校准【篇】

Leetcode question brushing: hash table 05 (adding four numbers II)

Product design - Requirements Analysis

![When Jerry's serial port is set up, it prints garbled code, and the internal crystal oscillator is not calibrated [chapter]](/img/6d/96b3326a201bf17d436c1af7834232.png)

When Jerry's serial port is set up, it prints garbled code, and the internal crystal oscillator is not calibrated [chapter]

Shunted Self-Attention | 源于 PvT又高于PvT,解决小目标问题的ViT方法

杰理之播 MP3 提示音功能【篇】

随机推荐

南芯半导体冲刺科创板:年营收9.8亿 顺为红杉小米OPPO是股东

Tutorial on installing SSL certificates in Microsoft Exchange Server 2007

Nanxin semiconductor rushes to the scientific innovation board: its annual revenue is RMB 980 million. Sequoia Xiaomi oppo is the shareholder

GES图计算引擎HyG揭秘之图切分

Comparison and evaluation of digicert and globalsign single domain ov SSL certificates

杰理之进入 soft off 后插拔 sd 卡会复位【篇】

Jerry's adding timer interrupt [chapter]

杰理之播 MP3 提示音功能【篇】

机器学习工作岗位

亚香香料深交所上市:市值40亿 鼎龙博晖与涌耀投资是股东

Halcon knowledge: contour operator on region (1)

涂鸦智能通过聆讯:拟回归香港上市 腾讯是重要股东

又一家破产清算:那些在时代和资本裹挟下风雨飘摇的游戏公司

【Qt】选择题

【One by One系列】IdentityServer4(六)授权码流程原理之SPA

Heavyweight: the domestic ide was released, developed by Alibaba, and is completely open source! (high performance + high customization)

学习编程只需要这三条建议!

微机原理第五章笔记整理

高级计网笔记(九)

NLP 论文领读|改善意图识别的语义表示:有监督预训练中的各向同性正则化方法