当前位置:网站首页>FPGA入门学习(一) - 第一个FPGA工程

FPGA入门学习(一) - 第一个FPGA工程

2022-07-26 11:52:00 【TARS_90%Honesty】

Verilog代码书写及相关语法

test.v

// 模块名和文件名一致

module test(

input port_a , // 只有wire,没有reg,默认wire

input port_b ,

input port_c ,

output wire port_d , // 默认wire(导线),也有reg(寄存器)

output wire port_e ,

output wire port_f ,

output wire port_g ,

output wire port_h

);

// assign :对wire型进行赋值

// always :对reg 型进行赋值

assign port_d = port_a & port_b; // 按位与

assign port_e = port_a | port_c; // 按位或

assign port_f = ~port_a; // 按位非

assign port_g = port_b ^ port_c; // 异或

assign port_h = port_a ^~ port_c; // 同或

endmodule

tb_test.v

// `timescale 1ns/1ps // 时间单位 / 时间精度(类似于刻度尺,单位cm,精度ms)

`timescale 1ns / 1ns // 时间精度也可以等于时间单位

module tb_test; // 测试模块没有输入输出端口

// 信号源的三根线

reg test_a;

reg test_b;

reg test_c;

// 接示波器的五根线

wire rslt_d;

wire rslt_e;

wire rslt_f;

wire rslt_g;

wire rslt_h;

// initial 赋值的信号,必须定义成reg型

initial begin

test_a = 1; // 在0时刻赋初值

test_b = 0;

test_c = 1;

#5 // 延时5ns

test_a = 0;

test_b = 1;

test_c = 1;

#5

test_a = 0;

test_b = 0;

test_c = 0;

end

// 模块例化(类似于函数调用)

test test_inst(

.port_a (test_a),

.port_b (test_b),

.port_c (test_c),

.port_d (rslt_d),

.port_e (rslt_e),

.port_f (rslt_f),

.port_g (rslt_g),

.port_h (rslt_h)

);

endmodule

Modelsim仿真步骤

- 第一步:新建工程。

- 第二步:指定工程名和保存路径,其余默认不动。

- Project Name:aaa

- Project Location:./sim

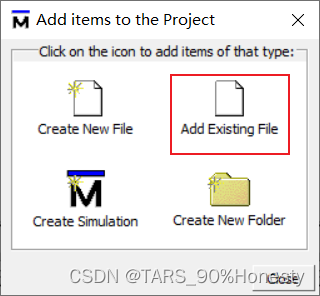

- 第三步:添加已存在的文件test.v和tb_test.v。

- 第四步:编译添加后的文件。

- 编译成功后,可以看到文件的status变为绿色对号。

提示信息显示成功。

- 编译成功后,可以看到文件的status变为绿色对号。

- 第五步:切换到Library下,找到work文件,点击+号,发现test和tb_test文件。

- 第六步:对tb_test文件启动仿真,文件上右键,

Simulate without Optimization

- 第七步:弹出的sim窗口中,可以看到例化模块名

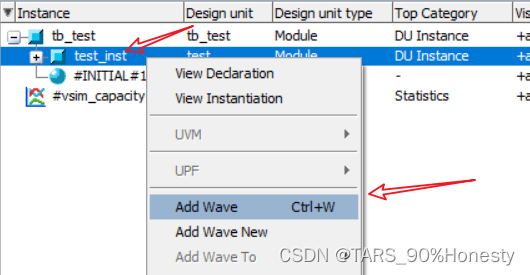

- 第八步:在tb_test上右键添加Wave,在test_inst上右键添加Wave。

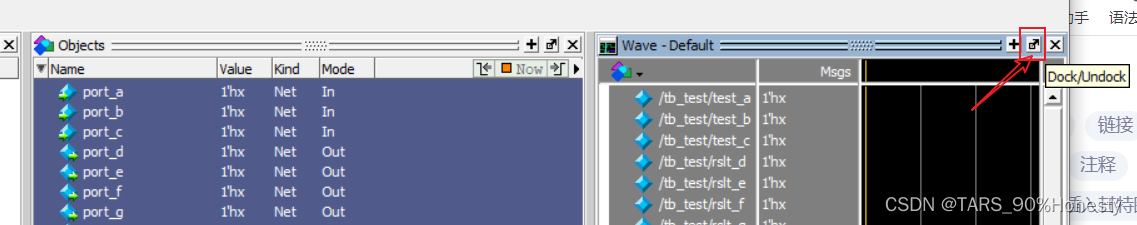

- 第九步:将Wave窗口独立显示出来,默认布局中点击如下图标。

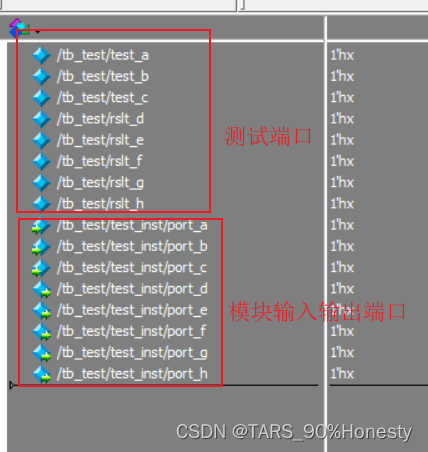

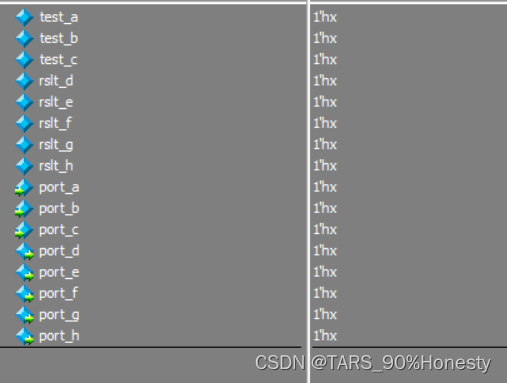

- 第十步:Wave窗口左侧,测试端口和模块端口都已列表形式展现出来。

- 点击左下角图标,不显示路径,更为简洁

- 点击左下角图标,不显示路径,更为简洁

- 第十一步:智能分组,Ctrl + A,Ctrl + G。

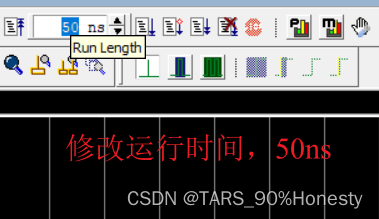

- 第十二步:修改运行时间,点击Run

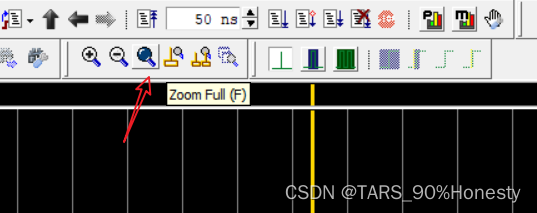

- 第十三步:点击Run后,波形不明显,点击全局预览

- 光标处放大

- 光标处放大

- 第十四步:检验波形是否正确,从而检验代码逻辑是否正确。

边栏推荐

- 虚拟偶像代言产品出问题谁负责? 且听律师分析

- FPGA入门学习(三)- 38译码器

- JVM内存溢出和内存泄漏的区别

- 浅谈低代码技术在物流运输平台中的搭建与管理

- 【安徽大学】考研初试复试资料分享

- Mongodn database is connected in the form of URL

- 大佬们,cdc oracle 怎么设置从指定scn号开始读取,或是怎么设置只读全量的归档,不去读取快

- Yuancosmos daily | yuancosmos social app "Party Island" product off the shelves; Guangzhou Nansha yuanuniverse industrial agglomeration zone was unveiled; The inter ministerial joint conference system

- The latest heart-shaped puzzle applet source code + with flow master

- Transactional事务传播行为?

猜你喜欢

浅谈Web Vitals

Harbor2.2 quick check of user role permissions

Cohere博客:在生产环境中运行大型语言模型-推理框架概览

Understand the string class

开放原子开源基金会OpenHarmony工作委员会主席侯培新寄语OpenAtom OpenHarmony分论坛

Pytest interface automated testing framework | common plug-ins of pytest

Some practical, commonly used and increasingly efficient kubernetes aliases

元宇宙日报|元宇宙社交 App“派对岛”产品下架;广州南沙元宇宙产业集聚区揭牌;数字经济发展部际联席会议制度推出

音视频+

Network protocol: tcp/ip protocol

随机推荐

MATLAB中strjoin函数使用

国内11所“袖珍”大学!在校园跑步,还没加速就出校门了...

Cohere博客:在生产环境中运行大型语言模型-推理框架概览

pytest接口自动化测试框架 | conftest.py

.....

PyCharm是真的强

Yuancosmos daily | yuancosmos social app "Party Island" product off the shelves; Guangzhou Nansha yuanuniverse industrial agglomeration zone was unveiled; The inter ministerial joint conference system

Metauniverse gamefi chain game system development NFT Technology

Question and answer No. 48: geek appointment - construction path of observable system

系统调用捕获和分析—修改内核方法添加系统调用

以太网驱动详解之RMII、SMII、GMII、RGMII接口

System call capture and segmentation - RING3 layer LD_ Preload mechanism for library function hijacking

Mongodn database is connected in the form of URL

大佬们,请教一下,我按照文档配了cdc连接oracle,总是运行报错找不到类 ValidstionE

10 reduce common "tricks"

系统调用捕获和分析完结篇制作系统调用日志收集系统

CVPR 2022 单目深度估计新SOTA—NeW CRFs:Neural Window Fullyconnected CRFs

pytest接口自动化测试框架 | pytest配置文件

什么是OOM,为什么会OOM及一些解决方法

向日葵资深产品总监技术分享:如何在AD域环境下应用