当前位置:网站首页>Physical verification LVS process and Technology (Part I)

Physical verification LVS process and Technology (Part I)

2022-06-29 19:20:00 【Aisi chip design】

*【 Editor's note 】 Prior to Calibre Calibre Bit by bit of physical verification technology There is one right LV Explanation of the overall overview , But for LV It's a little picky inside (fu) war (za) Of LVS for , Here is a series of special books to explain , I hope you can get some inspiration and harvest from it . *

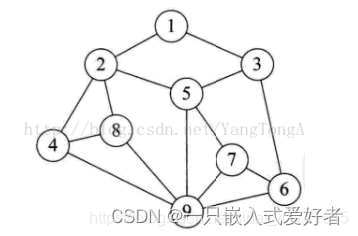

At the end of a chip tape-out When , An important inspection item of physical verification is LVS Perhaps judge of particulars, . Let's start with a handsome picture . ^_^

LVS Purpose

Comparison of consistency with functional classes formal Relatively speaking , Inside the chip LVS It can be regarded as a physical layout (GDS) And schematic diagram (Schematic) Has been compared to the rule file (LVS) Consistency comparison completed . therefore LVS The full name of is :Layout Versus Schematic.

Territory (Layout) Refer to : Tools (Calibre) For binary files (GDS) Proceed to spice Net list conversion ,

Schematic diagram (Schematic) Refer to : Tools (v2lvs) take verilog Conduct spice Net list conversion ,

Rules file (RSF): It's right GDS The operation of , as well as LVS Comparison is the normal configuration of

therefore , Use the following table to check LVS and formal(LEC/formality) Make a comparison

| category / Tools | Golden | Revised |

|---|---|---|

| formal RTL | RTL | syn-netlist |

| formal gate | syn-netlist | layout-netlist |

| LVS | layout-netlist | GDS |

You can see , The end user will get such a functional side identity

RTL = syn-netlsit = layout-nelist = GDS

The ultimate goal is to make the GDS Function is equal to RTL, To ensure that the function , The version is correct .

PS: The equation here indicates the functional side , This is because GDS It contains other components except the functional side ( These components do not affect the RTL Function comparison ), Including but not limited to :

- std-cell edition

- compliance RSF edition :TO Of GDS, Must be included in a compliance RSF Check the passed data .

- IP/phy Version of

- PG/UPF/PD/MV Information

- physical-only cell: Clamp,process-cell,marker-cell etc.

LVS Input file and use

in summary , Start a LVS Comparison of , The following three files are usually required , Namely :

- GDS

- PG netlist

- RSF

The data requirements and usage distribution of these input files are described below .

GDS Export and processing techniques

GDS Export and integration (merge)

there GDS The source of , It's from APR Of layout The database spits it out directly GDS, But usually this GDS It is impossible to directly give LVS To use , There may be factors including but not limited to the following :

- GDS Incomplete

- S Home process :ICC/ICC2 Of MW/NDM, The data source of is LEF,instance Of GDS Only the border information

- C Home process :enconter/innovus The data source of is LEF,instance Of GDS Only the border information

- GDS Of merge And version problems

- adopt APR merge GDS

- S Family ICC: Not at all GDS When exporting GDS merge

- S Family ICC2: Use command

write_gds -merge_files $GDS_FILE LISTConduct GDS When exporting GDS merge. This is mandatory replication , No matter what NDM Whether the actual instance Of GDS Information , adopt-merge_filesOptions , Exporting GDS When forced merge-in designated GDS Information - C home enconter/innovus: Use command

streamOut -merge $GDS_FILE LISTConduct GDS When exporting GDS merge. adopt-mergeOptions , Exporting GDS When merge-in designated GDS Information .

- adopt Calibre Command to GDS merge:

layout filemerge -in $TOP_GDS -in $LIB1_GDS -in $LIB2_GDS [-mode append|overwrite|rename|forcerename] -out $FULL_GDS - Recommendations and reasons

- Of the above methods merge The result is the same , It's still here recommend Calibre, For the following reasons :

- In terms of convenience and version control : first Calibre. Because the chip is APR Repair inside the tool , Usually and IP/LIB Of GDS Not directly related , In addition, before the chip is streamed :ROM_code/IP_update/parition_update Equal demand , In the hands of top-level personnel , Just control the versions , Without opening APR Tools , It can complete the final lamination , therefore , Use Calibre Its advantages are obvious .

- calibre Of GDS merge, For control ( Pattern / Plate layer / depth / The zoom /cell_name Mapping, etc. ) and rename Your report is quite friendly , For large chips GDS merge Quality control has certain advantages

- adopt APR merge GDS

PS:Calibre There's another one inside layout merge, The function of this command will be two GDS Content merged into a new GDS, I won't elaborate here

GDS port Information preparation

because LVS The comparison method of is very similar formal, Treat the actual goal as a black box , So whether it's flatten(nmLVS) still hierarchy(nmLVS-H: This is basically modern LV In a common way ) Of LVS, Both targets need to be black boxed (GDS/netlist) Of port Compare first . therefore GDS Inside port Information , When users export GDS It needs to be handled carefully before , however calibre DRC Usually not sensitive to this information , This is also LVS What's special about .

Calibre Usually use text(label) On the chip port For identification , By looking up DRM manual , You can see GDS Inside text Layer definition

therefore , User exporting GDS Before , Need to be in all of port To define what is right port text(label), for example :port:“A” For the terminal stay M5, Then the user needs to M5 terminal Of shape Create a text on the scope :“A”. It is usually recommended to put it in this terminal In the center of , And to Keep in mind that port and terminal layer You can't stagger , This is for the later stage bump Coordinates can also be shared . For example, the signal here port:P11

For all signals port, It's usually easier , Because the conventional method is a signal port Usually there is only one terminal, many terminal It is usually forbidden , It's not good for extraction And the top layer .

PG Of port There will be some special , This is because PG Usually multi-terminal, This will be easy to connect PG, By looking at IP Of PG pin You can feel this phenomenon

It can effectively improve the quality of power supply .

So for PG Of text, Here we need to emphasize the following points :

- It needs to conform to the original design intention : In spite of the PG It's a network , Users need to strictly define PG text The location of , Only for the real PG The input points are defined , Not every PG terminal All define one text, Here is divided into block and top Two kinds of situations

- For example, such a block, There are two layers PG Routing

Many projects now give more winding resources to block, Usually only the top layer is connected PG The Internet , Like here M5, So if users need to use it locally M4 As internal route, There is still room for operation , So in creating PG text You can only create M5 Of text, This is done in the later stage block LVS ( It will be expanded in detail later ) as well as IR It can be regarded as respecting the design . - about top Design ,PG Of text Especially important : Users can only use bump/bonding out Of PG terminal Definition text, Otherwise, the chip will be LVS Bring real hole

In this case , upper part (upper) Of PG shape And the lower part (lower) Of PG shape It is isolated inside the chip , In this evil time, the chip will only be in the lower part VDD bump point An external connection point , This is the time , If the user mistakenly defines another

- For example, such a block, There are two layers PG Routing

about port There's another interesting thing , be-all IP All have their own port text, It will also be placed at a higher level , for example IO Upper port,VDD IO Usually in M5 The hierarchy creates a text It happens to be called VDD, however top-level For this evil VDD IO The top-level application is in VDD_MAIN net On , For example, the picture below

therefore , The final GDS In the same M5 shape There will be two. text:VDD and VDD_MAIN, In this case , It is usually necessary to LVS The following commands are declared in the configuration of , To force the tool to recognize only top-level Of text, To avoid this conflict :TEXT DEPTH PRIMARY

As the process complexity increases ,layer:datatype The application of is becoming more and more popular ,APR The tool is exporting GDS When , Will apply some similar map file By GDS stream-out Micro control of , Can be controlled port/text Output . Even if the user creates port text, It also needs to be mapfile inside , Make the corresponding configuration , Otherwise, there will be text Not exported , This can also lead to LVS The failure of the . Specific operation details , Please refer to each EDA Configuration manual of tools

PS: because C Jiahe S Some strategic differences of home ,prboundary There are also some differences in the treatment of :S Home needs to be specified in the process prboundary Layer based on die boundary establish user_shape , Can be exported ;C Home needs to be in mapfile Inside definition layerObjName/layerObjType Not for DIEAREA/ALL, And layer number and data type (layer and datatype), You can export .

To be continued (To Be Continued )…

【 Knock on the blackboard and make a point 】

LVS It can be simply understood as physical level formal, Focus on goals , Be sure to start by focusing on the details .

Reference material

Cadence Innovus user guide

Synopsys ICC/ICC2 user guide

Mentor Standard Verification Rule Format(SVRF) Manual

Mentor Calibre DESIGNrev Reference Manual

Mentor Calibre Verification User’s Manual

边栏推荐

- 创作者基金会 6 月份亮点

- ChainSafe跨链桥部署教程

- powershell命令仅输出目录列表

- PHP Laravel 使用 aws 负载均衡器的 ip 错误问题

- 数据安全解决方案的大时代

- [笔记]再笔记--边干边学Verilog HDL –008

- Escape and March, the "two-sided Jianghu" of temporary food

- 开发者任务中心上线!千元豪礼送不停!

- 习题8 #第8章 Verilog有限状态机设计-4 #Verilog #Quartus #modelsim

- Have you mastered all the testing methods of technology to ensure quality and software testing?

猜你喜欢

逻辑结构与物理结构

建立自己的网站(12)

软件工程专业大二,之前的学习情况不太好该怎么规划后续发展路线

为什么信息化 ≠ 数字化?终于有人讲明白了

创作者基金会 6 月份亮点

KDD 2022 | 协同过滤中考虑表征对齐和均匀性

Technical methodology of new AI engine under the data infrastructure upgrade window

What about frequent network disconnection of win11 system? Solution to win11 network instability

【️爬虫必备->Scrapy框架从黑铁到王者️】初篇——万字博文详解(建议收藏)

QC protocol + Huawei fcp+ Samsung AFC fast charging 5v9v chip fs2601 application

随机推荐

微信推出图片大爆炸功能;苹果自研 5G 芯片或已失败;微软解决导致 Edge 停止响应的 bug|极客头条

JS judge whether the array key name exists

TP5 where queries whether a field in the database contains a value. Fuzzy queries are performed without the like method

Game Maker 基金会呈献:归属之谷

4-1端口扫描技术

IP error problem of PHP laravel using AWS load balancer

自动获取本地连接及网络地址修改

Element waiting mechanism

PHP outputs all dates between two specified dates

细说GaussDB(DWS)复杂多样的资源负载管理手段

Docker compose deploy the flask project and build the redis service

Cantata 9.5版本已正式通过SGS-TÜV认证,符合所有主要软件安全标准

Win11 system component cannot be opened? Win11 system widget cannot be opened solution

七牛图片访问参数(缩略图小尺寸啥的,避免浪费流量)

虎符限币种提现 用户曲线出金即亏损

php实现 提取不重复的整数(编程题目能够最快的熟悉函数)

【观察】软通动力刘天文:拥抱变化“顺势而为”,做中国数字经济“使能者”...

终于,进亚马逊了~

How is the combination of convolution and transformer optimal?

Technical methodology of new AI engine under the data infrastructure upgrade window