当前位置:网站首页>按键消抖的Verilog实现

按键消抖的Verilog实现

2022-07-26 03:48:00 【FPGA硅农】

按键消抖

当按键被按下时,由于机械开关的局限性,其对应的电平不会马上稳定,而是会在一段时间内发生抖动。为了正确的识别按键信息,我们必须进行按键消抖的处理。

代码实现

用两个寄存器对输入进行打拍,当这两个寄存器的值不同时(抖动),对计数器进行复位。否则,计数器每个周期加1,当计数器的值达到某个给定的值时,若寄存器的值有效,则说明检测到按键被按下。

若按键被按下后值为1,则代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/22 16:43:50

// Design Name:

// Module Name: bit_count

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module debounce(

input logic clk,

input logic rst,

input logic key_in,

output logic key_flag);

parameter CNT=1000;

logic key_d1;

logic key_d2;

logic [31:0] cnt;

//key_d2,1

[email protected](posedge clk,posedge rst)

if(rst)

{

key_d2,key_d1}<=2'b00;

else

{

key_d2,key_d1}<={

key_d1,key_in};

//cnt

[email protected](posedge clk,posedge rst)

if(rst)

cnt<=0;

else if(key_d1^key_d2) //还在抖动

cnt<=0;

else if(cnt==CNT)

cnt<=cnt;

else

cnt<=cnt+1;

//key_flag

[email protected](posedge clk,posedge rst)

if(rst)

key_flag<=0;

else if(cnt==CNT-1&&key_d2==1'b1) //持续时间足够长且为按下

key_flag<=1;

else

key_flag<=0;

endmodule

测试代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/23 21:03:12

// Design Name:

// Module Name: key_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module key_tb(

);

reg clk;

reg rst;

reg key_in;

wire key_flag;

//clk

initial

begin

clk=0;

forever

#5 clk=~clk;

end

//rst

initial

begin

rst=1;

#100

rst=0;

end

//key_in

initial

begin

key_in=0;

wait(rst==1'b0);

@(posedge clk);

//

key_in<=1;

@(posedge clk);

repeat(100)

begin

key_in<=$random;

@(posedge clk);

end

//

key_in<=1;

repeat(1000)

@(posedge clk);

//

key_in<=0;

repeat(100)

begin

key_in<=$random;

@(posedge clk);

end

@(posedge clk);

key_in<=0;

end

//inst

debounce U(

.*

/* input logic clk, input logic rst, input logic key_in, output logic key_flag */

);

endmodule

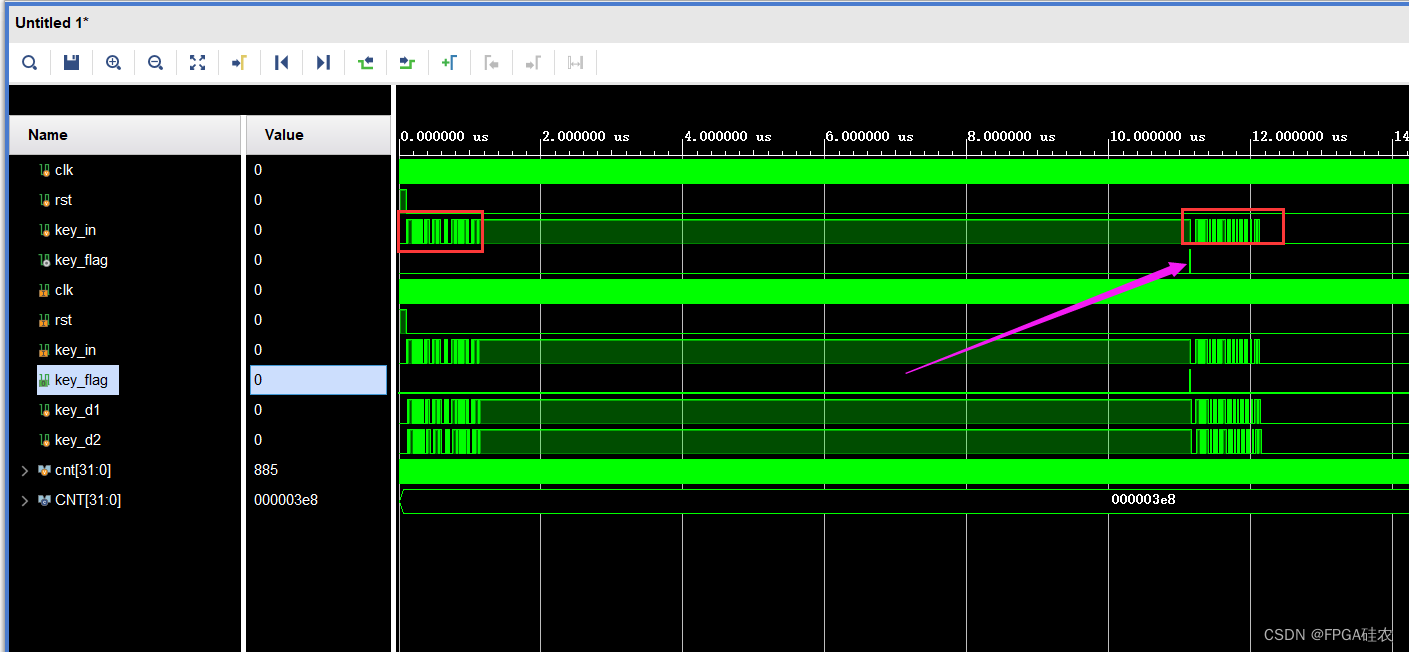

仿真结果

边栏推荐

- How Lora wireless gateway can quickly realize end-to-cloud transmission

- leetcode: 102. 二叉树的层序遍历

- Booking.com binke Shanghai noodles

- Data elements

- Course selection information management system based on SSM

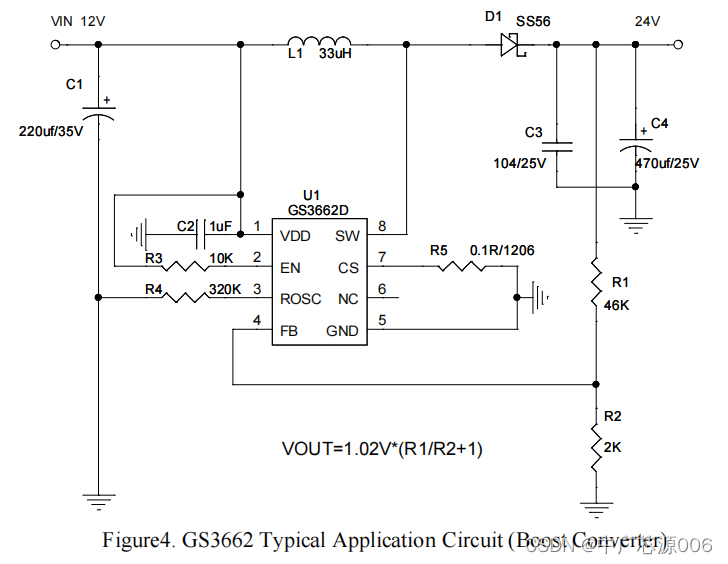

- Portable power fast charging scheme 30W automatic pressure rise and fall PD fast charging

- 5-20v input peak charging current 3.5A single lithium battery switching charging chip sc7101

- CPU and GPU are out of date, and the era of NPU and APU begins

- tf.truncated_ Normal() usage

- 用GaussDB(for Redis)存画像,推荐业务轻松降本60%

猜你喜欢

IDEA2020.3.1不能打开(双击不能打开),但可以通过idea.bat打开。

Analysis on the infectious problem of open source license

基本折线图:最直观呈现数据的趋势和变化

Portable power fast charging scheme 30W automatic pressure rise and fall PD fast charging

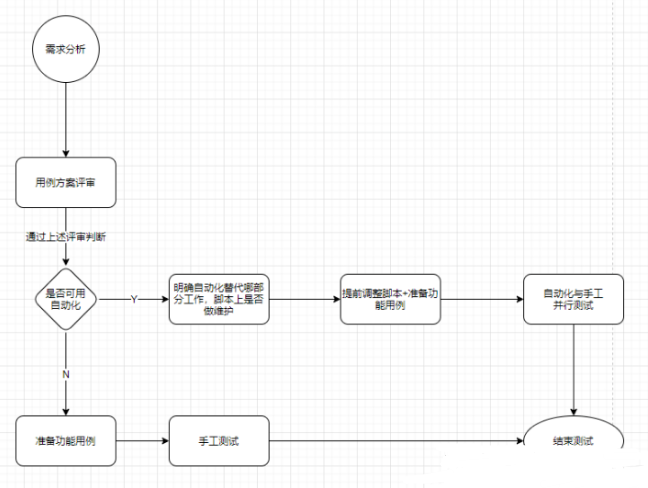

6年从零开始的自动化测试之路,开发转测试我不后悔...

cpu和gpu已过时,npu和apu的时代开始

Course selection information management system based on SSM

php 查找 session 存储文件位置的方法

Save the image with gaussdb (for redis), and the recommended business can easily reduce the cost by 60%

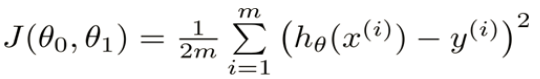

Derivation of linear regression principle

随机推荐

Kbpc1510-asemi large chip 15A rectifier bridge kbpc1510

leetcode-169.多数元素

《opencv学习笔记》-- 重映射

Booking.com binke Shanghai noodles

ASEMI整流桥GBU1510参数,GBU1510规格,GBU1510封装

redis集群的三种方式

Analysis on the infectious problem of open source license

全校软硬件基础设施一站式监控 ,苏州大学以时序数据库替换 PostgreSQL

触觉智能分享-RK3568在景区导览机器人中的应用

How Lora wireless gateway can quickly realize end-to-cloud transmission

bond网络模式配置

Leetcode-202. happy number

Hcip day 14

Bond network mode configuration

[MCU simulation project] external interrupt 0 and 1 control two digit nixie tube to count

Failed to install the hcmon driver

Derivation of linear regression principle

Experimental reproduction of image classification (reasoning only) based on caffe resnet-50 network

Visio:甘特图如何合并单元格?解决方案:覆盖单元格

Three solutions: when clicking the user to exit the login, press the back button of the browser, and you can still see the previous login page.