当前位置:网站首页>[In-depth and easy-to-follow FPGA learning 14----------Test case design 2]

[In-depth and easy-to-follow FPGA learning 14----------Test case design 2]

2022-07-31 00:15:00 【ape】

In-depth and simple FPGA learning 13----------Test case design 2

Reusable MCU Read/Write Design

This test script simulates the timing of MCU read/write external extended RAM.It will act as a separate test module that can be called as long as the interface is instantiated in the main test file.Figure 3.6 and Figure 3.7 show the timing of common MCU read/write external extended RAM.

The script for this test module is as follows:

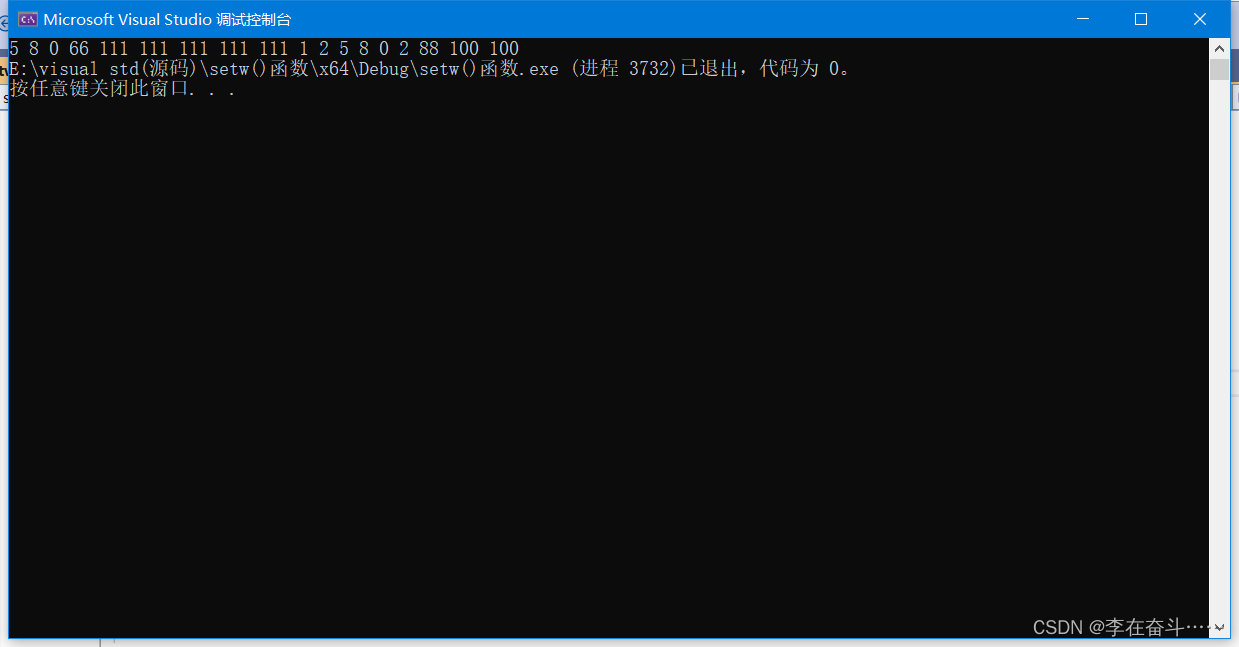

`timescale 1ns/1psmodule mcuram_rdwr(mcu_ale,mcu_wr_n,mcu_rd_n,mcu_p1,mcu_p0);output reg mcu_ale; //MCU read and write external RAM chip select signal, active lowoutput reg mcu_wr_n; //MCU read and write external RAM write strobe signal, active lowoutput reg mcu_rd_n; //MCU read and write external RAM read strobe signal, active lowoutput reg [7:0] mcu_p1; //MCU's p1 port, high 8-bit address businout [7:0] mcu_p0; //The P0 port of the MCU, the lower 8-bit address bus is multiplexed with the 8-bit data bus//----------------------------------------------------------------------------------------------------//reg[7:0] mcu_p0_out; //MCU's p0 port data bus output registerreg mcu_p0_link; /MCU's p0 port data direction control register, 1----output, 0-------inputassign mcu_p0 = mcu_p0_link ? mcu_p0_out : 8'hzz;//---------------------------------initial begin----------------------------------------------//MCU signal resetmcu_ale = 1;mcu_wr_n = 1;mcu_rd_n = 1;mcu_p0_out = 8'hff;mcu_p0_link =1;mcu_p1 = 8'hff;//------------------------------------------------------------------------------------------------task mcu_wr_task; //Simulate the timing of MCU writing to external RAMinput[15:0] wraddr;input[7:0] wrdata;begin#(127-43);mcu_p0_link =1; //MCU's p0 port is outputmcu_p0_out = wraddr[7:0]; //Send lower 8-bit addressmcu_p1= wraddr[15:8]; //Send high 8-bit address#43mcu_ale = 0; //chip select signal#48;mcu_p0_out = wrdata; //Send write data#twenty three;mcu_wr_n =0; //MCU read strobe# 400;mcu_wr_n = 1;#33;mcu_p0_out = { $random};mcu_p1 = {$random};#(100-33);mcu_ale =1;endendtasktask mcu_rd_task; //Simulate the timing of MCU reading external RAMinput[15:0] rdaddr;output[7:0] rddata;begin#(127-43);mcu_p0_link = 1; //The P0 port of MCU is outputmcu_p0_out = rdaddr[7:0]; //Send lower 8-bit addressmcu_p1 rdaddr[15:8]; //Send high 8-bit address#43;mcu_ale = 0; // chip select valid#48;mcu_p0_out {$random};#(250-48);mcu_rd_n = 0; //MCU write strobe#25;mcu_p0_link = 0; //The p0 port of MCU is input#(400-25-20);rddata = mcu_p0; //read data#20;mcu_rd_n = 1;mcu_p0_link = 1; //The p0 port of MCU is outputmcu_p0_out = {$random};mcu_p1 = {$random};#100;mcu_ale = 1;endendtaskendmoduleThe read/write timing waveforms simulated according to the test script are shown in Figures 3.8 and 3.9, respectively.

insert image description here](https://img-blog.csdnimg.cn/fe319f94b18b400ab2462a83ccb0c3c4.png)

For this design, although it has achieved the purpose of reuse, it is not enough to automate judgment.For example, as can be seen from Figure 3.6, when the MCU reads the external memory, within 25ns after the read strobe signal RDn is pulled low, the data on the P0 data bus must remain valid and stable, and this state must be maintained until RDn is pulled highuntil.

边栏推荐

猜你喜欢

随机推荐

45. [Application of list linked list]

uniapp folding box secondary loop

flex布局父项常见属性flex-wrap

从笔试包装类型的11个常见判断是否相等的例子理解:包装类型、自动装箱与拆箱的原理、装箱拆箱的发生时机、包装类型的常量池技术

asser利用蚁剑登录

宽客必备神器-AKShare

ctfshow 文件包含

HCIP第十五天笔记

xss的绕过

xss绕过:prompt(1)

对象集合去重的方法

【深入浅出玩转FPGA学习15----------时序分析基础】

软考学习计划

oracle数据库版本问题咨询(就是对比从数据库查询出来的版本,和docker里面的oracle版本)?

Android安全性优化——APP加固

乌克兰外交部:乌已完成恢复粮食安全出口的必要准备

C# VSCode & Rider引用命名空间快捷键

MySQL面试题

(五)fastai应用

.NET Cross-Platform Application Development Hands-on Tutorial | Build a Kanban-style Todo App with Uno Platform