当前位置:网站首页>使用SystemVerilog门模型描述的组合逻辑

使用SystemVerilog门模型描述的组合逻辑

2022-06-22 05:33:00 【傻童:CPU】

使用SystemVerilog门模型描述的组合逻辑

模块和文件

组合逻辑是无状态的,换言之,输人的变化立即反映在输出的改变上。

SystemVerilog的基本构造单元是模块(module)。

module And2 (input wire x,y,output wire z);

assign z = x & y;

endmodule

模块描述从关键字module开始,接着是模块名和括号中的输入和输出列表。模块以关键字endmodule结束 请注意,在模块的第一句后有分 号“;”,但是在关键字endmodule后面没有分号。

在上述例子中,该模型只有一条声明语句。用关键字 assign来表明所谓的连续赋值 (continuous assignment)语句(这将在后面解释)。x和y 的按位相与得到的值被赋给z。SystemVerilog的算术和逻辑操作符是基于C语言的。

建议读者在组织设计工作中遵循下列指导原则:

- 每个模块都有自己独自的文件。

- 文件名与模块名应该完全一致。

- Verilog和SystemVerilog文件名通常分别用“.v”和“sv”作为其文件名的后缀,而本书中所有的例子都用“.v”作为文件名的后缀。

- 在文件名、文件夹和目录名中不要使用空格,即使操作系统允许这样命名,但是有些 EDA工具还是不能处理带空格的文件名)。

延迟

为了验证时序仿真模型必须包括时序信息。包括时序信息的最简单方法是为每个门建立延迟模型。例如,10ps延迟的与非门可以写成如下形式:

nand #10ps g1(y,a,b);

在上面这个例子中,只有一个延迟参数。在与非门的场

边栏推荐

- Development planning and investment strategy analysis report of global and Chinese microwave ablation industry during the 14th Five Year Plan period 2022-2027

- Machine learning Note 6: number recognition of multiple classification problems in logistic regression

- Go语言使用zap日志库

- 服务器php相关网页开发环境搭建

- Cookie setting and reading in C #

- Throw away electron and embrace Tauri based on Rust

- MinGW download and installation

- redis连接错误:ERR Client sent AUTH, but no password is set解决方案2个

- From "platform transformation" to "DTC brand going to sea", what is the trend of 2021?

- Market development trend forecast and investment risk outlook report of China's silicon carbide industry 2022-2027

猜你喜欢

总有人问我:独立站该怎么玩?3个案例,你看完就懂了

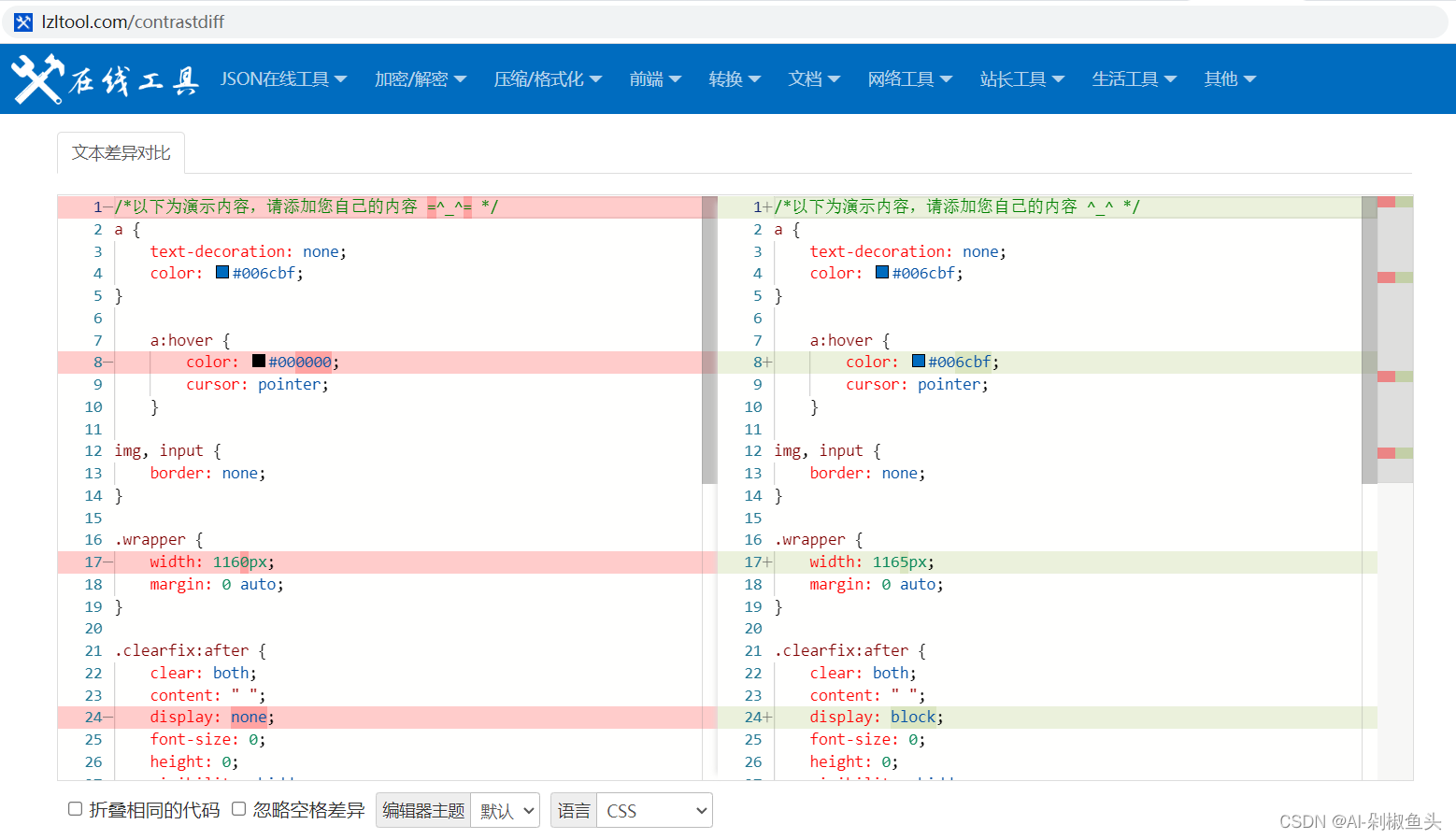

Online text code comparison tool

vscode 远程连接错误:Server status check failed - waiting and retrying

数据的存储(进阶)

Data storage (Advanced)

Remove then add string from variable of Makefile

Clion installation Download

SCM future employment development direction, learn SCM must know some entry-level knowledge and industry prospects, read the benefit

Stockage des données (avancé)

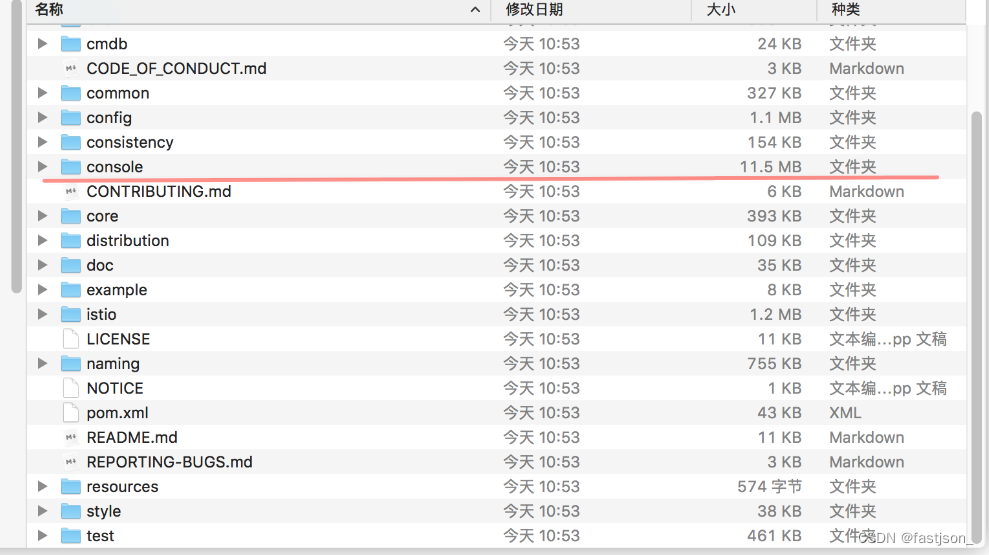

nacos server 源码运行实现

随机推荐

C语言指针(进阶)

Delete the packaging use of pop-up components

Development prospect and investment potential prediction report of China's rare earth permanent magnet industry during the "14th five year plan" period 2022-2027

Analysis of annual average temperature based on TMP data in cru

Development prospect forecast and investment strategy analysis report of global and Chinese manganese oxide nano powder industry 2022-2028

电脑卡顿怎么办?

\[\e]0; \[email protected]\h: \w\a\]\[\033[01;32m\]\[email protected]\h\[\033[

Global and Chinese silicon carbide barrier Schottky diode market demand and future prospect report 2022-2027

Analysis of 43 cases of MATLAB neural network: Chapter 29 research on the application of limit learning machine in regression fitting and classification -- Comparative Experiment

北峰助力南昌市应急管理局打造公专融合应急通信保障网

CMAKE notes

线性回归:最小二乘、泰尔森估计、RANSAC

为Cortex-M4编写优化的DSP代码

移动端布局适配

Air conditioning (daily question 50 in spring)

open source hypervisor

大厂晋升学习方法四:Play 学习法

Golang Viper库入门教学

Talk about MySQL's locking rule "hard hitting MySQL series 15"

An unordered array of N integers. Find the first number after each element that is larger than it. The time complexity is O (n)