当前位置:网站首页>FPGA systematic learning notes serialization_ Day10 [sequential logic, competitive adventure, synchronous reset, asynchronous reset]

FPGA systematic learning notes serialization_ Day10 [sequential logic, competitive adventure, synchronous reset, asynchronous reset]

2022-06-24 17:04:00 【FPGA technology Jianghu】

FPGA Systematic study notes serial _Day10 【 Sequential logic 、 Competition and adventure 、 Synchronous reset 、 Asynchronous reset 】 And 【 Counter design 、verilog Grammatical supplement 】

This series is FPGA Systematic learning students' learning notes are sorted out and shared , If you have the intention to study or purchase the development board , You can add communication group to contact group leader .

Serial 《 Three core smart fpga Design and development - The first 10 God 》 【 Sequential logic 、 Competition and adventure 、 Synchronous reset 、 Asynchronous reset 】 And 【 Counter design 、verilog Grammatical supplement 】

Original author : Zifeng River Please contact the group owner for authorization , Otherwise, we will be held responsible

This article introduces the design of temporal logic , To design a counter to explain sequential logic , At the same time expand verilog Grammatical knowledge .

One 、 Sequential logic

Temporal logic is Verilog HDL Another important application in design . From the characteristics of the circuit , Its characteristic is that the output at any time not only depends on the input at that time , It's also related to the original state of the circuit .

In terms of circuit behavior , No matter how the input changes , Only if the edge of the clock ( A rising or falling edge ) On arrival , It's possible to change the output .

1、 In the description of sequential circuits always In the block reg All type signals are synthesized into registers , This is different from combinational logic circuits .

2、 Nonblocking assignment is recommended in temporal logic “<=”.

3、 The sensitive signal list of sequential logic only needs to add the trigger edge of the clock , All other input and condition judgment signals need not be added , This is because the timing logic is controlled by the jump edge of the clock signal .

Two 、 Temporal logic in FPGA in RTL Realization

Let's write a simple register , have a look fpga How to realize temporal logic

module counter(

input a,

input clk,

output reg q

);

[email protected](posedge clk)begin

q <= a;

end

endmoduleLet's see fpga Chip planner for

From the chip Planner , You can see a few details .

1、 We used a look-up table 、 A register . Yes FPGA Come on , This register is there even if you don't use it

2、 Our output signal is related to clk synchronous , Must wait until clk The rising edge of , The output will be updated , So the function of register is realized

3、 ... and 、 Synchronous reset 、 Asynchronous reset

1、 Synchronous reset : In fact, your operation is synchronized with the rising edge of the clock

for instance , You will q Set to 0, The following code is synchronous reset ,q <= 0, It is executed when the rising edge of the clock arrives , So it's a synchronous reset

module counter(

input a,

input clk,

output reg q

);

[email protected](posedge clk)begin

q <= 0;

end

endmodule2、 Asynchronous reset : In fact, your operation has nothing to do with the clock

for instance , You will q Set to 0, The following code is asynchronous reset ,q <= 0, Whatever the state of the clock , Only rst_n Clear when you come

module counter(

input a,

input clk,

input rst_n,

output reg [7:0] q

);

[email protected](posedge clk,negedge rst_n)begin

if(!rst_n)

q <= 0;

else

q <= q + 1'b1;

end

endmoduleFour 、 Competition and adventure

Competition and adventure : intend , When I sample on the rising edge of my clock , The input signal is unstable , This will bring metastable problems to the circuit

To solve the problem of competition and risk , We only need to meet the signal set-up time and hold time

5、 ... and 、verilog Grammatical supplement

1、parameter Define global variables

parameter T = 26'd49_000_000;

2、defparam Redefine parameters , This is mainly to modify the internal parameters of the instantiated module in the simulation script

defparam counter_inst.T = 26'd49; counter counter_inst( .clk (clk), .rst_n (rst_n), .flag (flag)

6、 ... and 、 Counter design

To design a 1 Second counter , When the time is one second, give a flag The signal

1、 Code implementation verilog.v

module counter(

input clk,

input rst_n,

output reg flag

);

reg [25:0] count;

parameter T = 26'd49_000_000;

[email protected](posedge clk,negedge rst_n)begin

if(!rst_n)begin

flag <= 1'b0;

count <= 0;

end

else if(count == T)begin

flag <= 1'b1;

count <= 0;

end

else

begin

count <= count + 1'b1;

flag <= 1'b0;

end

end

endmodule2、 Simulation script

I changed the time parameter to T Change it to T=26‘d49; Convenient simulation

`timescale 1ns/1ps

module counter_tb;

reg clk;

reg rst_n;

wire flag;

defparam counter_inst.T = 26'd49;

counter counter_inst(

.clk (clk),

.rst_n (rst_n),

.flag (flag)

);

always #10 clk = ~clk;

initial begin

clk = 0;

rst_n = 0;

#20;

rst_n = 1;

#5000000;

$stop;

end

endmodule3、 Simulation results

3.1、 You can see the pulse flag It only lasted one cycle

3.2、 It can be seen that the trigger of the pulse is 50 A count

7、 ... and 、 The adder problem hidden in the counter

The counter we designed , It actually uses an adder , Adders are combinational logic ( Because combinatorial logic only depends on input )

When we give the adder an initial value 0 When , The output of the adder immediately outputs 1, That's when it comes to simulation , After starting to reset and pull up ,count At the first clk The rising edge is 1 Why

边栏推荐

- Following the previous SYSTEMd pit

- TVP experts talk about geese factory middleware: innovating forward and meeting the future

- About with admin option and with grant option

- What is the reason for the worse website SEO ranking?

- Introduction to koa (III) koa routing

- Ramda 鲜为人知的一面

- Page scrolling effect library, a little skinny

- Nonholonomic constrained robot

- After the collective breakthrough, where is the next step of China's public cloud?

- Can yangjianyun's new media operation in 2021 bear all the expectations of the enterprise's private domain traffic demand?

猜你喜欢

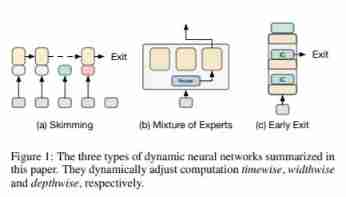

A survey on dynamic neural networks for natural language processing, University of California

MySQL learning -- table structure of SQL test questions

A survey on model compression for natural language processing (NLP model compression overview)

A survey of training on graphs: taxonomy, methods, and Applications

![[leetcode108] convert an ordered array into a binary search tree (medium order traversal)](/img/e1/0fac59a531040d74fd7531e2840eb5.jpg)

[leetcode108] convert an ordered array into a binary search tree (medium order traversal)

Daily algorithm & interview questions, 28 days of special training in large factories - the 15th day (string)

随机推荐

5g brings opportunities and challenges. Are you ready to defend against DDoS?

Tensor and tensor network background and significance - basic knowledge

How to customize the log output format of zap?

IBM:以现代化架构支撑AI与多云时代的企业数字化重塑

liver failure! My friend made a programming navigation website!

A survey on dynamic neural networks for natural language processing, University of California

Abstract factory pattern

Today, Tencent safety and SAIC Group officially announced!

What is a reptile

Contributed code to famous projects for the first time, a little nervous

[play with Tencent cloud] my operation strategy from domain name application to website filing in Tencent cloud

2021-04-02: given a square or rectangular matrix, zigzag printing can be realized.

Recent progress of ffmpeg go

区块哈希游戏竞猜系统开发(成熟代码)

New MySQL 8.0 feature - enhanced logical backup recovery

6 things all engineers should know before FEA

[log service CLS] Tencent cloud game battle engine mgobe accesses CLS

GB gb28181 video cascading intelligent analysis platform easygbs broadcast video console error 401

Principle analysis of robot hardware in the loop system

Hook graphics kernel subsystem