当前位置:网站首页>Quartus call & Design d Trigger - simulation & time sequence Wave Verification

Quartus call & Design d Trigger - simulation & time sequence Wave Verification

2022-06-23 13:36:00 【Petit monstre.】

quartusAppelez&ConceptionDDéclencheur——Simulation&Vérification des ondes chronologiques

- Table des matières

- Un.、- Oui.DDéclencheur

- 2.、ConceptionDVérification de la séquence de déclenchement en temps opportun

- Trois、AppelezDVérification de la séquence de déclenchement en temps opportun

- Quatre、verilogMise en œuvre linguistiqueDVérification de la séquence de déclenchement en temps opportun

- Cinq、Résumé et références

Table des matières

1、 In Quartus-II Nous avons conçu un circuit de porteDDéclencheur,Et faire des simulations,Vérification de la forme d'onde séquentielle;

2、In Quartus-II Appelle directement unDCircuit de déclenchement,Effectuer une simulation,Vérification de la forme d'onde séquentielle,Avec2Comparer;

3、In Quartus-IIAvecVerilogÉcrivez une langueDDéclencheur,Effectuer une vérification de simulation

Un.、- Oui.DDéclencheur

DLe déclencheur est une fonction de mémoire,Dispositif de stockage de l'information à deux états stables, Est composé de plusieurs

Unit é logique de base du circuit séquentiel,C'est aussi un circuit d'Unit é important dans le circuit logique numérique.

DDéclencheur àHorloge pulséeCPLa frontière de(Saut positif0→1)Un renversement s'est produit,L'état secondaire du déclencheur dépend deCPAvant l'arrivée du bord ascendant de l'impulsionDÉtat des extrémités,C'est - à - dire:Sous - état=D.Donc,,Il a un0、Position1Deux fonctions.Parce queCP=1Le circuit a un effet de blocage de maintien pendant,Donc, dansCP=1Période,DChangement d'état des données à la fin,N'affecte pas l'état de sortie du déclencheur.

DLes déclencheurs sont largement utilisés, Peut être utilisé comme enregistrement de signaux numériques , Déplacer le dépôt , Diviseur de fréquence et générateur de forme d'onde, etc. .

1、Structure

DDéclencheur(data flip-flopOudelay flip-flop)Par4 Composition des portes ,Parmi euxG1EtG2 Composition de base RSDéclencheur. Lorsque le déclencheur maître - esclave déclenché par le niveau fonctionne , Le signal d'entrée doit être ajouté avant le bord de saut positif .Si dansCP Signal d'interférence à l'entrée pendant les niveaux élevés , Il est donc possible que l'état du déclencheur soit erroné . Et les déclencheurs de bord permettent CP Le signal d'entrée est ajouté immédiatement avant l'arrivée du bord de déclenchement. .Voilà., Le temps d'interférence de l'entrée est considérablement réduit , La probabilité d'interférence est réduite .BordureD Les déclencheurs sont également appelés Maintenance - Bordure de blocage DDéclencheur.BordureD Les déclencheurs peuvent être composés de deux D Déclenchement en série ,Mais le premierDTriggerCP Non - door Reverse required .

2、Caractéristiques

Menu

Diagramme chronologique

C'est ça.D Une brève introduction aux déclencheurs ,Pour en savoir plusD Connaissance des déclencheurs , Vous pouvez consulter le lien ci - dessous ;

DDéclencheur.

2.、ConceptionDVérification de la séquence de déclenchement en temps opportun

1、Créer un projet

file—>new project wizard

Modifier le nom du projet ,Cliquez aprèsnext

Choisir la puce appropriée et sa famille

Directnext

Création du projet terminée,Cliquez surfinish

2、Créer un fichier de boîte

Cliquez surnew

Sélectionnez la signature de la case rouge

Sélectionnez comme indiqué

Sélectionnernand2, Deux entrées et non - portes ,Ajouter à tour de rôle4- Oui.nand2Et une portenot

Après l'ajout, comme le montre la figure

Sélectionnez l'outil de connexion

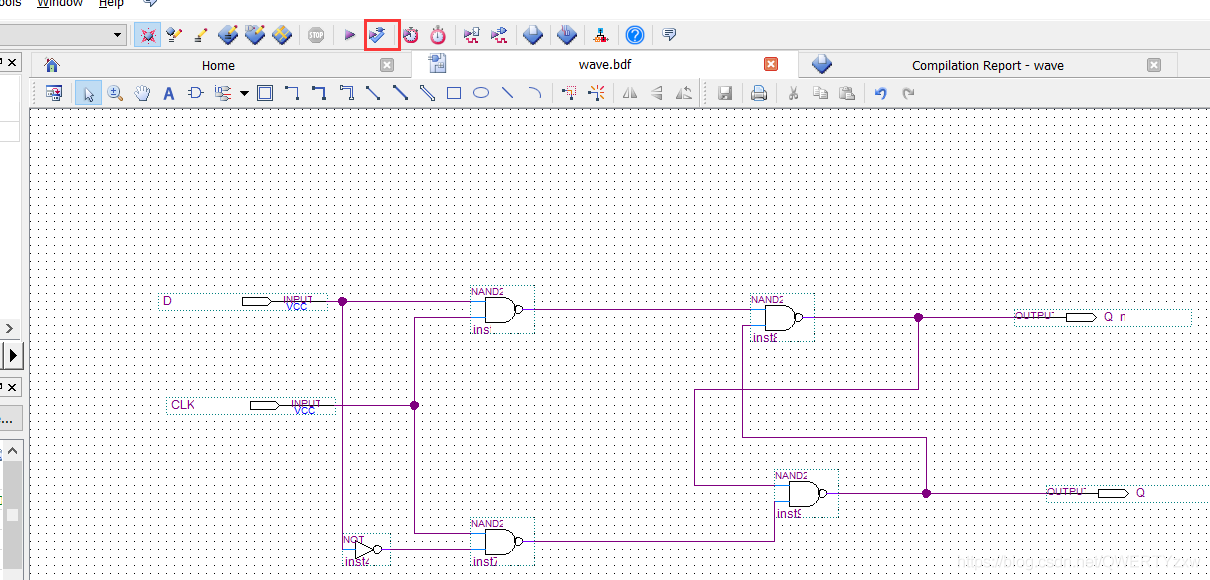

L'effet de connexion est comme indiqué dans la figure ( Double - cliquez pour changer le nom de la goupille )

Enregistrer le schéma de circuit

3、Compiler un fichier schématique

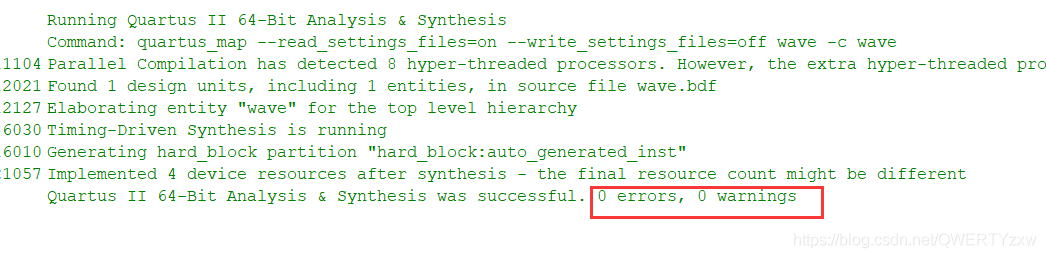

Compiler les diagrammes de circuits

Compiler l'interface

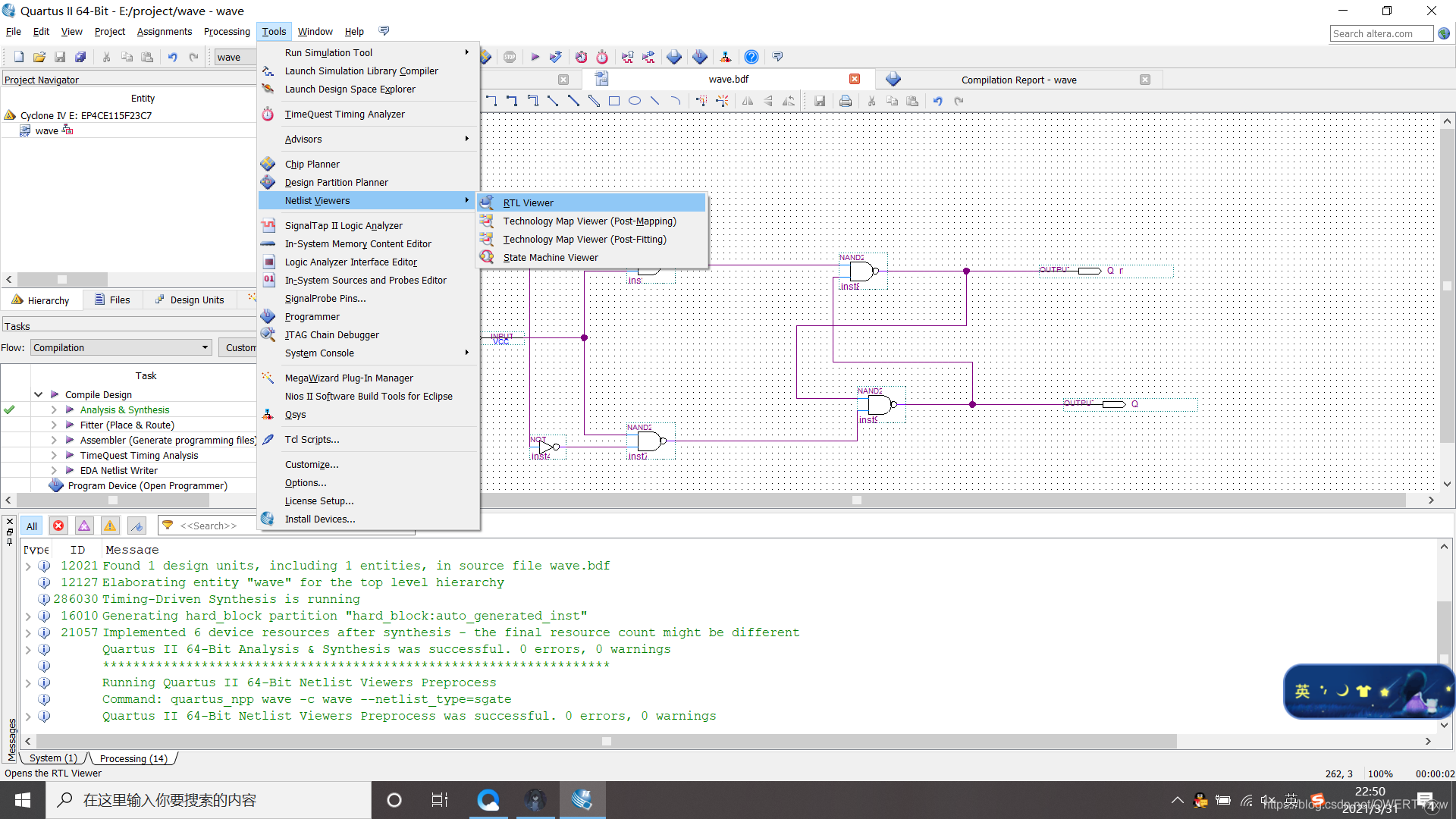

rtl viewer, Voir les diagrammes de circuits matériels

Diagrammes de circuits

4、CréationvwmFichier Waveform

Sélectionner l'icônevwm

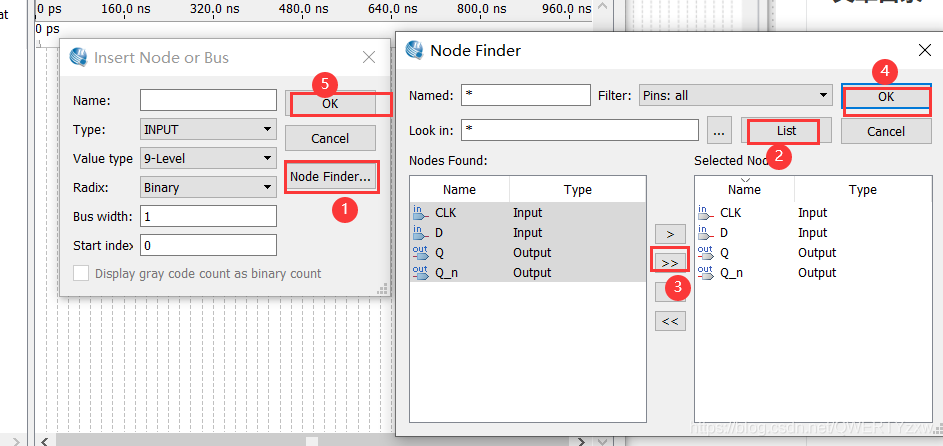

Fonctionnement comme indiqué dans la figure

Ajouternode or bus

Affichage des effets

Modifier le signal d'entrée clk,Générer un signal d'horloge

Sélection de la sourisD,QSignalQ_n,Modifier(Clic gauche de la souris sélectionné Double - cliquez sur modifier la valeur )

5、Simulation de forme d'onde séquentielle

Compiler

Erreur signalée

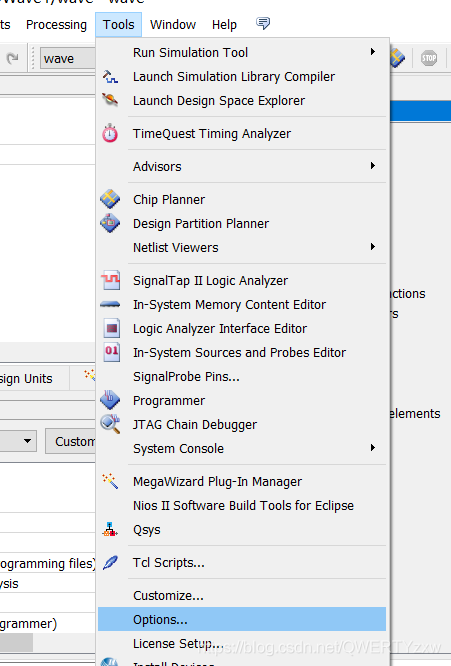

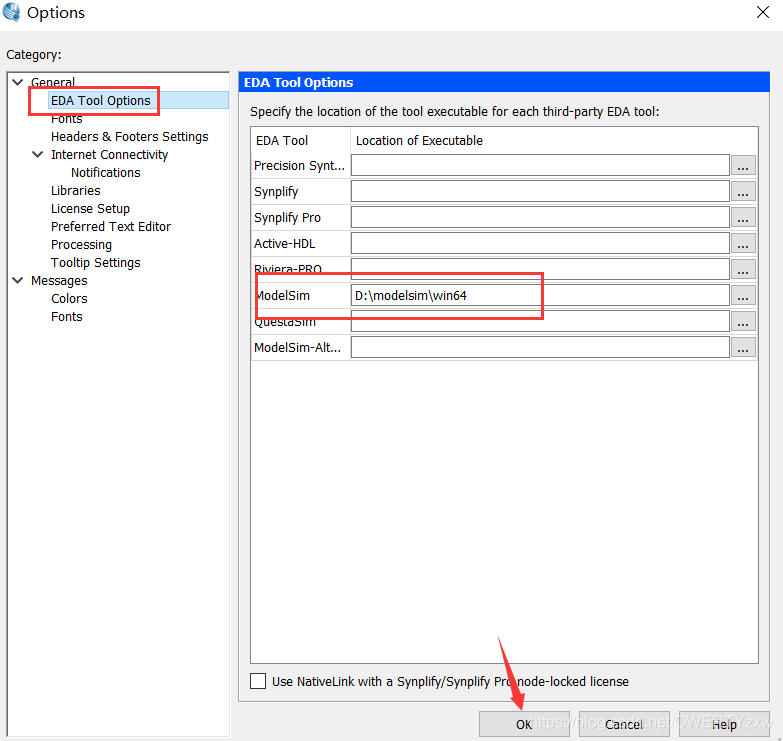

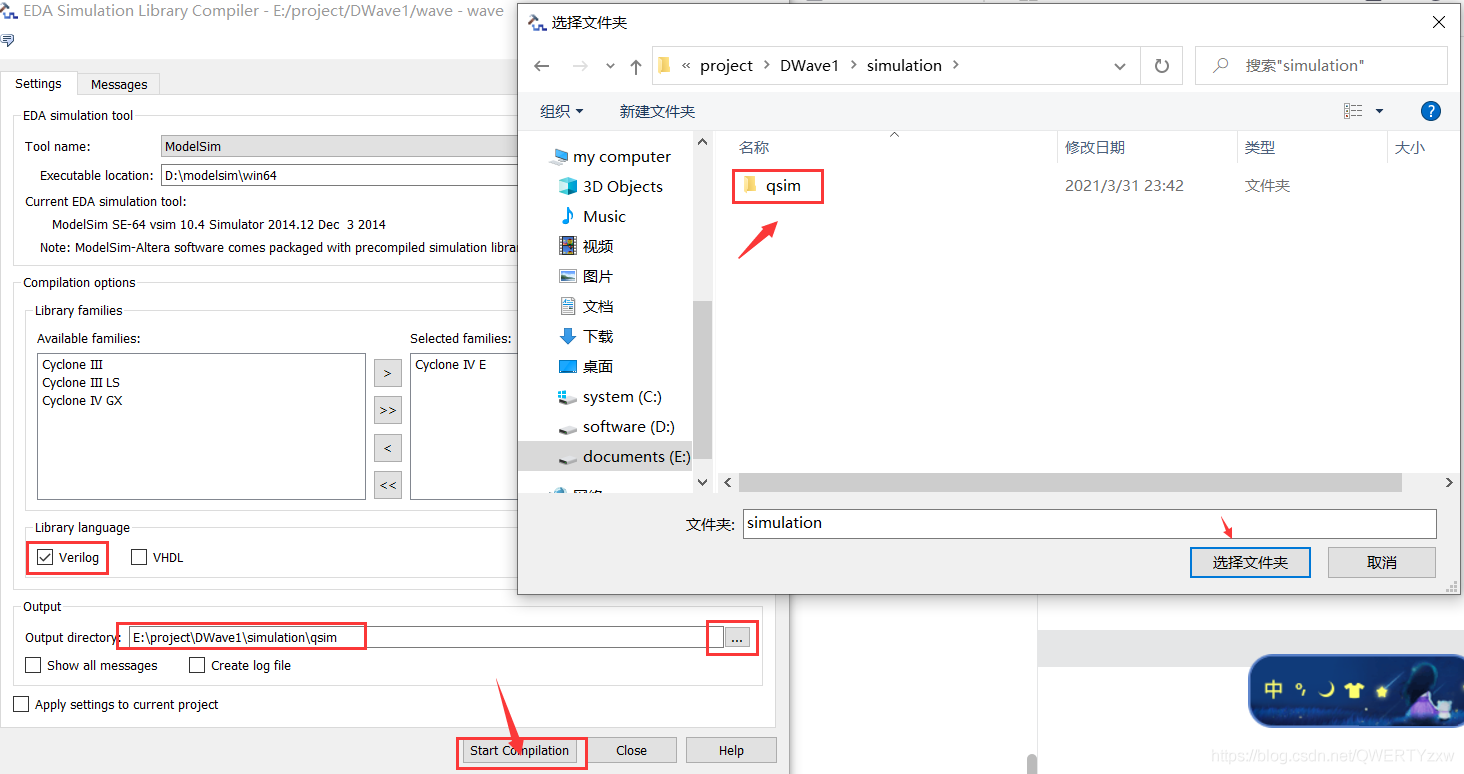

Connexionmodelsim

Résolution des erreurs

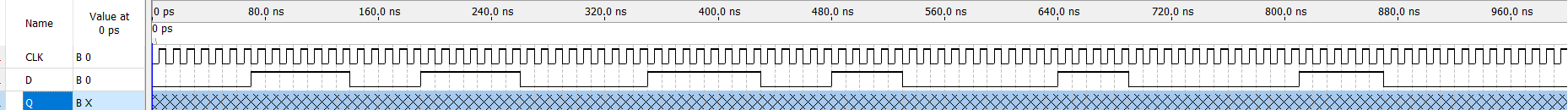

Les résultats sont présentés dans la figure

Résultats de la simulation

Trois、AppelezDVérification de la séquence de déclenchement en temps opportun

1、Créer un fichier de boîte

Créer une méthode d'ingénierie comme ci - dessus

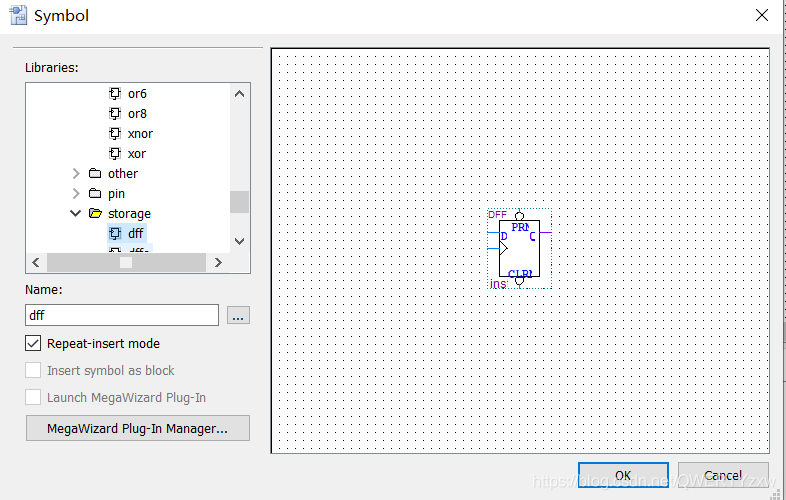

AppelezDDéclencheur

Broche de patch de fil ,L'effet est montré dans la figure(Ctrl+ La roue de la souris peut zoomer sur la goupille de déclenchement, etc. )

2、Compiler des schémas

Voir le diagramme matériel

Compiler

3、CréationvwmFichier Waveform et simulation

Forme d'onde

Résultats de la simulation séquentielle

Quatre、verilogMise en œuvre linguistiqueDVérification de la séquence de déclenchement en temps opportun

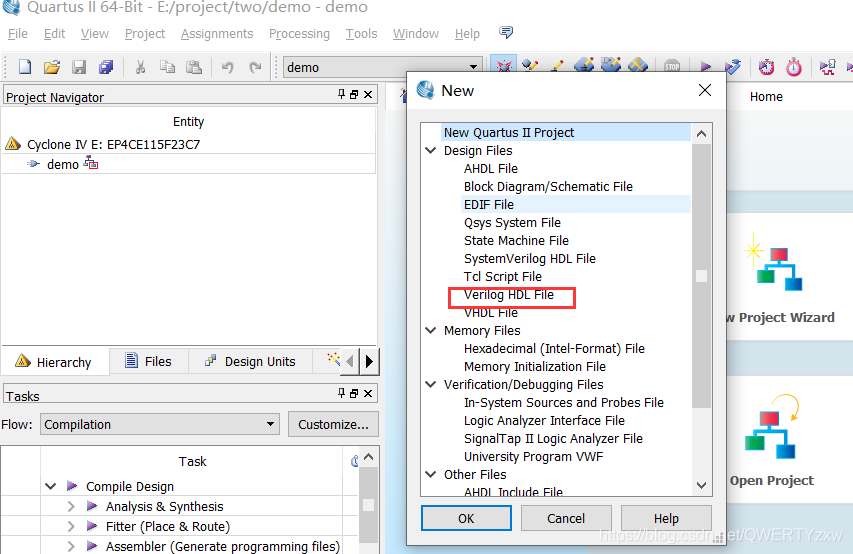

1、CompilationverilogDocumentation

Créer d'abord le projet,La méthode est la même que ci - dessus.

CréationVerilogDocumentation,Cliquez surfile—new

Collez le code suivant

//demoEst le nom du fichier

module demo(d,clk,q);

input d;

input clk;

output q;

reg q;

always @ (posedge clk)//Nous utilisons le bord positif de l'horloge pour son signal sensible

begin

q <= d;//Quand le bord ascendant est actif,Prends ça.dCaptureq

end

endmodule

Enregistrer et compiler

2、Voir le diagramme de circuit généré

3、Simulation de séries chronologiques d'essai

Les codes sont les suivants:

//Code d'essai

`timescale 1ns / 1ns

module demo_tb;

reg clk,d;

wire q;

demo u1(.d(d),.clk(clk),.q(q));

initial

begin

clk = 1;

d <= 0;

forever

begin

#60 d <= 1;// Burr artificiel

#22 d <= 0;

#2 d <= 1;

#2 d <= 0;

#16 d <= 0;//Maintien16nsFaible niveau de, Et le faire tourner périodiquement

end

end

always #20 clk <= ~clk;// La demi - période est 20ns, Le cycle complet est 40nsUn signal de

endmodule

Enregistrer et compiler

Diagramme de simulation

Cinq、Résumé et références

1、Résumé

D Processus de simulation de séquence de déclenchement en temps opportun ,On peut le découvrir.D La fonction de base du déclencheur est de réinitialiser le signal 1Quand,CLK Le bord ascendant de QChangement de valeur.Par conséquent,, L'équation de l'état secondaire peut être obtenue comme suit: Q n + 1 = D

2、Références

Quartus II Utilisation d'outils de simulation autonomes .

Quartus-II Schéma d'entrée et procédure de simulation .docx.

Quartus-II13.1Trois façons de le faireDSimulation de Séquence temporelle de déclenchement.

边栏推荐

- First exposure! The only Alibaba cloud native security panorama behind the highest level in the whole domain

- Scope of groovy

- MIT 6.031 Reading5 : Version Control学习心得

- What is the version of version 1.54 when connecting to Oracle?

- 互联网技术发展内卷后的出路——iVX的诞生

- Have you ever encountered incompatibility between flink1.15.0 and Flink CDC MySQL 2.2.1? f

- Capacity limited facility location problem

- How did Tencent's technology bulls complete the overall cloud launch?

- Restcloud ETL resolves shell script parameterization

- Digraph D and e

猜你喜欢

LM05丨曾经的VIX(二代产品)

How to write vite plug-ins

First exposure! The only Alibaba cloud native security panorama behind the highest level in the whole domain

AssetBundle resource management

Has aaig really awakened its AI personality after reading the global June issue (Part 1)? Which segment of NLP has the most social value? Get new ideas and inspiration ~

How to enable the SMS function of alicloud for crmeb knowledge payment

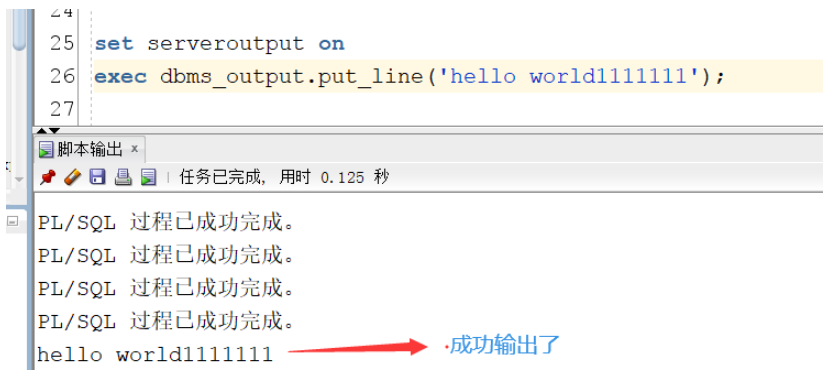

Oracle中dbms_output.put_line怎么使用

After the uncommitted transactions in the redo log buffer of MySQL InnoDB are persisted to the redo log, what happens if the transaction rollback occurs?

支持HomeKit、NFC:智汀智能门锁SL1仅需要149元

Qunhui 10 Gigabit network configuration and test

随机推荐

Modelsim 安装步骤详解

The R language inputs the distance matrix to the hclust function for hierarchical clustering analysis, uses the cutree function to divide the hierarchical clustering clusters, specifies the number of

.Net怎么使用日志框架NLog

你管这破玩意儿叫 MQ?

R language dplyr package arrange function sorts dataframe data and sorts dataframe data through multiple data columns (ascending sort by default)

实战监听Eureka client的缓存更新

Gradle Build Cache引发的Task缓存编译问题怎么解决

Quarkus+saas multi tenant dynamic data source switching is simple and perfect

Tt-slam: dense monocular slam for flat environment (IEEE 2021)

kubernetes日志监控系统架构详解

Js: get the maximum zindex (Z-index) value of the page

Groovy map operation

The two 985 universities share the same president! School: true

同花顺网上开户安全吗,需要注意什么

1 channel 100m optical fiber transceiver 1 100m optical 1 100m electric desktop Ethernet optical fiber transceiver built-in power supply

理解ADT与OOP

理财产品长期是几年?新手最好买长期还是短期?

ExpressionChangedAfterItHasBeenCheckedError: Expression has changed after it was checked.

Hanyuan hi tech 8-way telephone +1-way 100M Ethernet RJ11 telephone optical transceiver 8-way PCM telephone optical transceiver

Windows install MySQL