当前位置:网站首页>ARM processor mode and register

ARM processor mode and register

2022-06-12 11:49:00 【fanxiaoyu321】

List of articles

Pattern

Different architectures define different patterns , But they are backward compatible , Here is ARM920T CPU Supported processor modes .

| Schema name | Code | describe |

|---|---|---|

| User(USR) | 10000 | The user mode in which most applications run , Also called non privileged mode |

| FIQ | 10001 | FIQ Abnormal interruption |

| IRQ | 10010 | IRQ Abnormal interruption |

| Supervisor(SVC) | 10011 | The management call instruction is executed or reset When |

| Monitor(MON) | 10110 | Security extension mode , For safety purposes only |

| Abort(ABT) | 10111 | Storage access mode |

| Hyp(HYP) | 11010 | Virtualization extension |

| Undef(UND) | 10011 | When the instruction execution is not defined |

| System(SYS) | 11111 | System mode , The pattern is related to USR Mode shared register |

The above modes are in addition to USR Out of mode , Other modes belong to privileged mode .

register

General registers

R0—R12 this 13 This is called a general purpose register , Generally speaking, they can be used for any purpose .

R13: Also called sp, Usually used as a stack pointer , Note that each pattern has its own R13 Register copy .

R14: Also called lr( Connection register ). This register serves two purposes : One is when subroutines are called ,lr Used to save the return address ; Second, when an abnormal interrupt occurs , The specific physics of the exception pattern lr The register is set to the address to be returned by the exception mode ( This step is done automatically by hardware ).

R15: Also called pc, Program counter , Always save the current address ( Pay attention to assembly line technology ) The address of the instruction . stay ARM State, , It differs from the address of the instruction currently being executed 8 Bytes (3 Class assembly line ).

Status register

CPSR( Current program status register ) Can be accessed in any processor mode , It contains conditional flag bits 、 Interrupt inhibit bit 、 The current processor mode flag and other control and status bits , The format is shown in the figure . Besides , There is also a dedicated physical status register for each exception mode , be called SPSR( Backup program status register ), When a particular exception occurs , This register is used to store CPSR The content of , When the exception mode returns , It can be used SPSR To restore CPSR.

- M: Processor mode bit , By modifying this section , You can switch the operating mode of the processor ;

- T: Identify whether you are currently using Thumb Instructions ,0 by ARM Command mode ,1 by Thumb Command mode ;

- F:FIQ Disable flag bit , If 1, Then disable FIQ,0 To open ;

- I: Allied , This is a IRQ Disable flag bit ;

- V:ALU Operation overflow flag ;

- C:ALU Carry mark ;

- Z:ALU Zero mark ;

- N:ALU negative ;

Instruction set

ARM The following commands are supported .

Instruction condition code

Almost all ARM Instructions can carry condition codes , Make the instruction execute only when the condition is satisfied , The supported condition codes are as follows :

边栏推荐

- Who moved my package lock

- K53. Chapter 2 installing kubernetes v1.22 based on binary packages -- cluster deployment

- 淘宝新改版商家如何操作,需要注意的点有哪些

- [database] SQLite version upgrade and downgrade

- Logrotate log rotation method create and copyruncate principles

- C# 37. Textbox scroll bar and multiline

- Doris records service interface calls

- Channel Shuffle类

- UML series articles (31) architecture modeling - deployment diagram

- MySQL45讲 01 | 基础架构:一条SQL查询语句是如何执行的?

猜你喜欢

Inter class and intra class relations in video classification -- regularization

创建Servlet项目

Basic principle of Doppler effect

UML系列文章(30)体系结构建模---制品图

PIP install in the CONDA environment cannot be installed into the specified CONDA environment (the default PIP installation location of the CONDA environment)

TinyMCE series (I) TinyMCE environment construction

conda环境下pip install 无法安装到指定conda环境中(conda环境的默认pip安装位置)

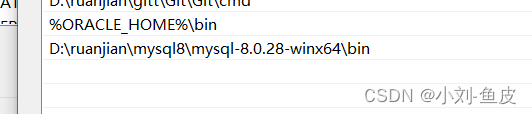

Windows10安装mysql-8.0.28-winx64

C# 37. textbox滚动条与多行

异步路径处理

随机推荐

Google Earth Engine(GEE)——Kmeans聚类快速进行土地分类(双for循环快速调参)

QT based travel query and simulation system

The evil 203 in systemctl

When you have a server

Design of tablewithpage

【QNX Hypervisor 2.2 用户手册】4 构建QNX Hypervisor系统

ARM处理器模式与寄存器

为什么新品发布上架之后会没有流量,新品应该怎么发布?

影响店铺权重的三十一条,快来看看中招了吗

K52. Chapter 1: installing kubernetes v1.22 based on kubeadm -- cluster deployment

6.6 RL:MDP及奖励函数

ARM指令集之数据处理指令寻址方式

Unlimited growth, we will all go to the future | the 15th anniversary of the founding of InfoQ China

Face recognition PIP failed to install Dlib Library

Design of TTable

Doris records service interface calls

Byte order (network / host) conversion

Doris记录服务接口调用情况

Index in MySQL show index from XXX the meaning of each parameter

Unit test case framework --unittest