当前位置:网站首页>Aurora8B10B IP使用 -02- IP功能设计技巧

Aurora8B10B IP使用 -02- IP功能设计技巧

2022-06-21 05:57:00 【Vuko-wxh】

前言

承接上文,本文主要介绍了关于IP核中一些功能的配置的方法和技巧使用的示例,主要参考了IP手册的第三章内容。

复位和断电

复位

复位信号用于将 Aurora 8B/10B 内核设置为已知的启动状态。 复位时,内核停止任何当前操作并重新初始化一个新通道。

在全双工模块上,复位信号复位通道的 TX 和 RX 端。在单工模块上,tx_system_reset 复位 TX 通道,而 rx_system_reset 复位 RX 通道。 gt_reset 信号复位收发器,最终复位内核。tx_system_reset 与单工边带接口上使用的 tx_reset 和 rx_reset 信号是分开的。

示例

双工内核中的复位断言

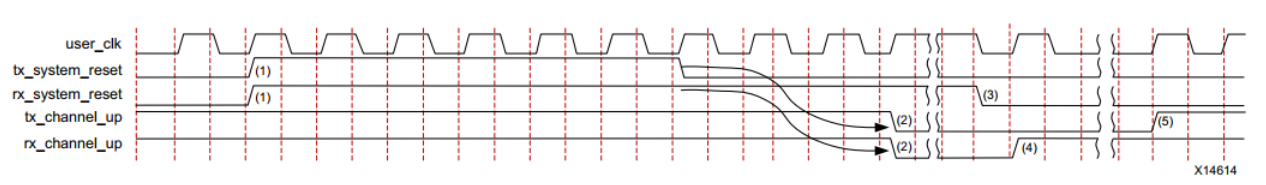

双工内核中的复位断言应至少有六个 user_clk 时间段。 因此,channel_up 在三个 user_clk 周期后被置低,如下图所示。

双工内核中的 gt_reset 断言

下图显示了双工内核中的 gt_reset 断言,应该至少有六个 init_clk_in 时间段。 因此,user_clk 在几个时钟周期后停止,因为没有来自收发器的 txoutclk 并且 channel_up 随后被置低。

单工内核中的 tx_system_reset 和 rx_system_reset 断言

下图显示了系统中连接的单工 TX 内核和单工 RX 内核。TX_IP 和 RX_IP 可以在同一个或多个设备中。

下图显示了单工内核中 tx_system_reset 和 rx_system_reset 断言的推荐过程。

- tx_system_reset 和 rx_system_reset 被置位至少六个时钟 user_clk 时间段。

- tx_channel_up 和 rx_channel_up 在三个 user_clk 周期后被置低。

- rx_system_reset 被置低(或)在 tx_system_reset 被置低后释放。这确保了单工 TX 内核中的收发器更早地开始传输初始化数据,并提高了单工 RX 内核与正确数据序列对齐的可能性。

- rx_channel_up 在 tx_channel_up 断言之前被断言。 单工 RX 内核必须满足此条件,单工 TX 内核中的单工定时器参数(C_ALIGNED_TIMER、C_BONDED_TIMER 和 C_VERIFY_TIMER)需要调整以满足此标准。

- 当 simplex-TX 内核在配置的时间内完成 Aurora 8B/10B 协议通道初始化序列传输时,tx_channel_up 被置位。 tx_channel_up last 的断言确保 simplex-TX 内核在 simplex-RX 内核准备好时发送 Aurora 初始化序列。

Aurora 8B/10B Duplex Power On Sequence(双工上电序列)

在板子上电序列期间,gt_reset 和 reset 信号都必须为高电平。收发器参考时钟 (GT_REFCLK) 和内核自由运行时钟 (INIT_CLK) 预计在上电期间保持稳定,以便 Aurora 8B/10B 内核正常运行。

Aurora 8B/10B Duplex Normal Operation Reset Sequence(双工正常操作复位序列)

在正常操作期间,复位信号预计在 gt_reset 信号置位之前至少置位 128 个 user_clk 时间段,以确保可编程逻辑中的内核部分达到已知复位状态 在gt_reset 的断言而抑制 user_clk 信号之前,如下所示。

Aurora 8B/10B Simplex Power On Sequence(单工上电顺序)

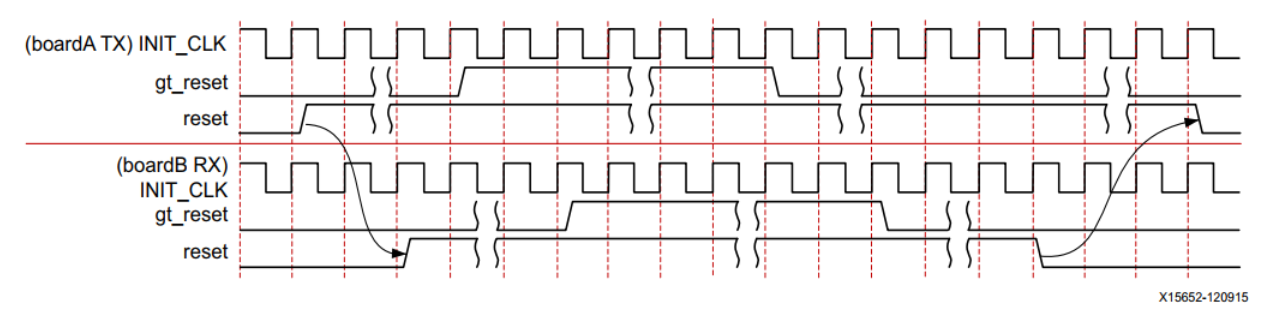

在上电期间,TX simplex 和 RX simplex 内核的 gt_reset 和 reset 信号预计为高电平。 预计 INIT_CLK 和 GT_REFCLK 在上电期间是稳定的。 必须先将TX板上的gt_reset信号置低,然后再将RX端的gt_reset置低; 这可确保在 RX 侧正确锁定 CDR,如下图所示。

单工上电序列:

解除 TX 端 gt_reset (A)

解除 RX 端 gt_reset

解除 RX 端同步到 user_clk (D)

解除 TX 端同步到 user_clk (B)

注意:必须注意确保 (D) 到 (B) 的时间差尽可能小。

Aurora 8B/10B Simplex Normal Operation Reset Sequence(单工正常操作复位序列)

对于单工配置,建议 TX 侧复位序列与 RX 侧复位序列紧密耦合,因为 TX 和 RX 链路没有通信反馈路径。 请注意,如果 RX 端被复位,则没有直接的机制来通知 TX 端复位。 因此,对于 Aurora 8B/10B 单工内核,需要在系统级别处理复位耦合。 每次 TX 侧复位之后必须跟随 RX 侧,如下图所示,RX 侧复位无效和 TX 侧复位无效之间的时间必须尽可能短。 在置位 gt_reset 之前,至少需要 128 个时钟周期,以确保在 gt_reset 的置位抑制 user_clk 之前,可编程逻辑中的内核部分达到已知的复位状态。 gt_reset 的断言时间必须至少为六个 init_clk 时间段,以满足内核中包含的去抖动电路。

断电

这是一个高电平有效信号。 断言powerdown时,Aurora 8B/10B 内核中的收发器将关闭,将它们置于非工作、低功耗模式。 取消断言断电时,内核会自动复位。 gt_reset 必须在powerdown 后置位后置位。

Shared Logic(共享逻辑)

Vivado IDE 中的共享逻辑选项将内核配置为包括可共享资源,例如收发器四通道 PLL (QPLL)、收发器差分 refclk 缓冲器 (IBUFDS_GTE2),以及内核或示例设计中的时钟和复位逻辑。

共享逻辑层次结构称为 <component_name>_support。 图 3-9 和图 3-10 显示了两个层次结构,其中共享逻辑块包含在内核或示例设计中。 两个层次的区别在于核心的边界。 它使用 Vivado中的 Shared Logic 选项进行控制。当共享逻辑位于内核中时,Single Ended 选项将从内核中排除相应的差分时钟缓冲器。

共享逻辑的内容取决于物理接口和目标设备。共享逻辑包含收发器差分缓冲区 (IBUFDS_GTE2/IBUFDS_GTE3) 的实例、支持复位逻辑和 <USER_COMPONENT_NAME:>_CLOCK_MODULE 的实例化。 共享逻辑还包含基于所选收发器类型的收发器公共实例 GTPE2_COMMON、GTXE2_COMMON 或 GTHE2_COMMON。 支持复位逻辑包含用于复位和 gt_reset 端口的去抖动逻辑。

Aurora 8B/10B 内核使用 CPLL,不使用 QPLL(即 GTXE2_COMMON/GTHE2_COMMON)。 QPLL 用于 Zynq-7000 和 7 系列器件,并在共享逻辑中进行实例化,以与其他赛灵思串行连接内核保持一致。

下表列出了每个系列的的共享资源。

Sharable Resources

| Transceiver Type used in the Aurora 8B/10B Core | Resources |

|---|---|

| Zynq-7000 and 7 series device GTX/GTH/GTP transceivers in 2-byte mode | IBUFDS_GTE2: transceiver reference clock GT*_COMMON: transceiver clocking; BUFG: clocking IBUFDS: init_clk |

| Zynq-7000 and 7 series device GTX/GTH/GTP transceivers in 4-byte mode | IBUFDS_GTE2: transceiver reference clock GT*_COMMON: transceiver clocking MMCM: clocking 2xBUFG: clocking; IBUFDS: init_clk |

| UltraScale GTH Transceivers | IBUFDS_GTE3: transceiver reference clock BUFG_GT: clocking |

| UltraScale+ GTH Transceivers | IBUFDS_GTE4: transceiver reference clock BUFG_GT: clocking |

gt_refclk1_out 和 gt_refclk2_out 信号可以由设计中的其他收发器共享,并且应遵循收发器时钟指南以实现连接性和收发器四通道邻近性。图 3-11 显示了从包含共享逻辑的内核 (aurora_8b10b_0) 到另一个不包含共享逻辑的内核实例 (aurora_8b10b_1) 的可共享资源连接。 某些端口可能会根据内核配置和所选收发器的类型而改变。

Using the Scrambler/Descrambler(使用扰码器/解扰器)

一个 16 位加扰器/解扰器,用于具有多项式的数据:G(x) = X16 + X5 + X4 + X3 + 1,可在 < component name>_scrambler.v[hd] 中获得 模块。它确保在很长一段时间内不会出现重复数据。 加扰器和解扰器分别基于时钟补偿字符的发送和接收进行同步。扰码器仅影响数据符号。

使用 CRC

为用户数据实现的 16 位或 32 位 CRC 在 < component name>_crc_top.v[hd] 模块中可用。

为 2 字节设计生成 CRC16,为 4 字节设计生成 CRC32。 crc_valid 和 crc_pass_fail_n 信号指示接收到的 CRC 与发送的 CRC 的结果。 CRC-CCITT (16’h1021) 和标准以太网多项式 (32’h04C11DB7) 分别用作 16 位和 32 位的 CRC 多项式。CRC 是按通道计算的,并以数据为后缀。 在接收器 AXI 接口处,CRC 被删除,数据包按照发送器的 AXI 接口接收到的方式发送。 下图说明了如何在没有 CRC 的情况下发送相同的数据包以及何时启用 CRC 选项。

热插拔逻辑

Aurora 8B/10B 中的热插拔逻辑(使用自由运行的 init_clk 信号)基于接收到的时钟补偿字符。 Aurora RX 接口接收到时钟补偿字符意味着通信通道处于活动状态且未中断。 如果在预定时间内没有接收到时钟补偿字符,热插拔逻辑将复位内核和收发器。 时钟补偿模块必须用于 Aurora 8B/10B 设计。

时钟补偿

时钟补偿功能允许在 Aurora 8B/10B 通道的每一侧使用的参考时钟频率差异高达 ±100ppm。 根据 Aurora 8B/10B 协议规范 ,使用内核生成标准时钟补偿模块 <component_name>_standard_cc_module.v[hd]。

standard_cc_module 处理时钟补偿字符的生成周期,如下表中所述。 可以使用 CC_FREQ_FACTOR 控制周期性。

| Lane Width | DO_CC 之间的 USER_CLK 周期 | DO_CC 持续时间(USER_CLK 周期) |

|---|---|---|

| 2 | 5,000 | 6 |

| 4 | 2,500 | 3 |

防止 16 字节 UFC 消息与时钟补偿序列冲突所需的先行周期数取决于通道中的通道数和每个通道的宽度。在时钟补偿字符传输期间,本机流控制消息请求未被确认。 这有助于防止 NFC 消息和时钟补偿序列发生冲突。参数 CC_FREQ_FACTOR 确定 CC 序列的频率。 任何增加或减少参数的尝试都应该经过仔细的分析和测试。

确保选择的持续时间和周期足以校正所用时钟频率之间的最大差异。不要在彼此的八个周期内执行多个时钟校正序列。用CC 序列替换长的空闲序列(>12 个周期)可以降低EMI。

使用小端支持

Aurora 8B/10B 内核默认支持大端格式的用户界面。 它还支持小端格式以无缝连接到符合 AXI4-Stream 的 IP 内核。

reference

- PG046

边栏推荐

- Error running code generator file: the server time zone value ' й ��� ʱ ��‘ is unrecognized or represents more than one time

- NFT platform track dark horse takes advantage of the situation

- Importance of variables in code

- Microbial ecological data analysis - redundancy analysis

- El table remove the scroll bar and Zebra Stripe color modification

- el-table去掉滚动条和斑马纹颜色修改

- Microbial ecological sequencing analysis -- CCA analysis

- After the code is generated by the code generator, the copy is completed, and the module is not displayed on the web page

- lambda-stream

- Discussion on the American ess audio DAC decoder chip es9023

猜你喜欢

C语言课程设计(服装管理系统详解)

【MYSQL】MySQL的SQL语句执行流程

![Leetcode 75 - 颜色分类 [Medium] 三种实现方法](/img/52/61ae051babf6b5c6b603093a17e55c.png)

Leetcode 75 - 颜色分类 [Medium] 三种实现方法

Interprocess communication (IPC): semaphores

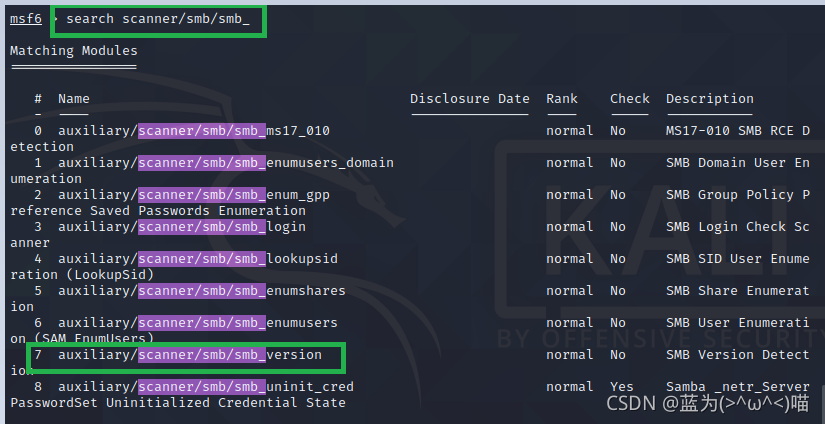

Metasploit入侵win7

Touch chip applied in touch screen of washing machine

Working principle of digital temperature sensor and analysis of temperature measurement principle

应用在洗衣机触摸屏中的触摸芯片

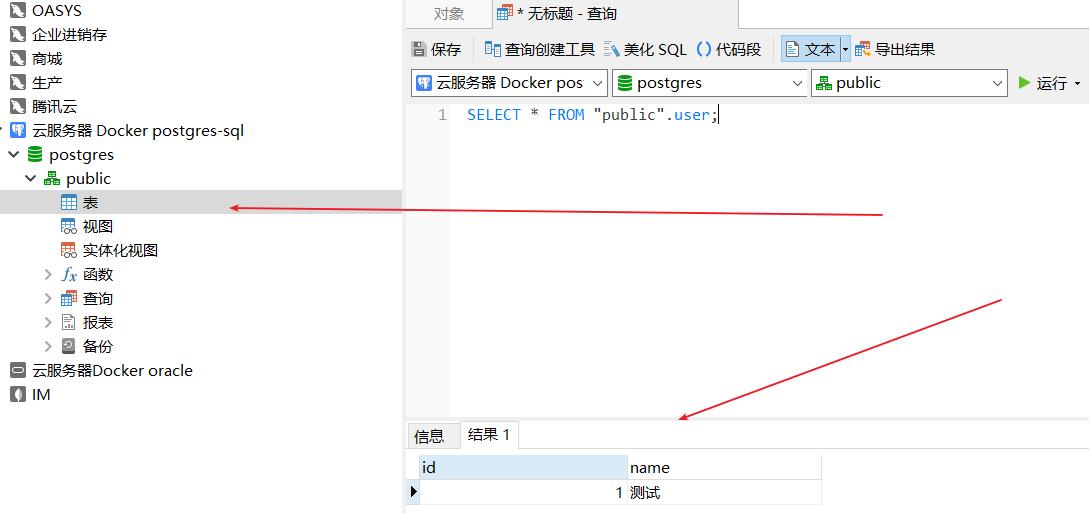

记录 Navicat 连接 PostgreSQL 无法显示对应表的问题

Use of mysqldump in MySQL

随机推荐

tf.compat.v1.get_default_graph

397 linked list (206. reverse linked list & 24. exchange nodes in the linked list in pairs & 19. delete the penultimate node of the linked list & interview question 02.07. link list intersection & 142

El table remove the scroll bar and Zebra Stripe color modification

ReturnType

应用在LED植物照明中的LED照明灯

tf.contrib.slim.conv2d()

一次Namenode的RPC延迟故障排查引发的深入思考

Importance of variables in code

Aurora8B10B IP使用 -05- 收发测试应用示例

第一章:数据库系统概述(数据库期末复习)

复制 代码生成器 生成的代码到idea中,运行后网址报错怎么解决

模块 14 - 15:网络应用通信考试

sqli-labs-17

Attention based seq2seq model

计组必刷题:存储系统(已完结,附详细解析)

【Grafana】Grafana Mimir在海量时间序列指标中的优化

sqli-labs23

R statistical plot - correlation of environmental factors +mantel test combination diagram (linket package introduction 1)

Leetcode刷题 ——— (4)字符串中的第一个唯一字符

Cross chain revelation: has your assets really been transferred in the process of cross chain?