当前位置:网站首页>Input / output and interrupt technology -- microcomputer Chapter 6 learning notes

Input / output and interrupt technology -- microcomputer Chapter 6 learning notes

2022-06-30 04:23:00 【IOT classmate Huang】

I / O and interrupt technology —— Microcomputer Chapter 6 study notes

List of articles

- I / O and interrupt technology —— Microcomputer Chapter 6 study notes

Preface

Pure review , I am tired , Open book !

MindMap

I / O system

One 、I/O Interface

characteristic

- complexity

- asynchrony

- The real time

- Equipment independence

Problem solved

- Speed match (Buffer)

- Signal drive ( Level converter 、 Driver )

- Matching of signal form and level (A/D、D/A)

- Information format ( Byte stream 、 Block, etc )

- Timing matching ( Timing relationship )

- Bus isolation —— Tristate gate

function

- Address decoding and device selection

- Information input and output

- command 、 Buffer and latch of data and status

- Information conversion ( Analog revolution, etc )

Two 、I/O port

classification

- Data port DB

- Status port AB

- Control port CB

The difference and relationship between ports and interfaces

In a word : An interface is a collection of one or more ports .

Port address formula : Port address = Chip address ( Constitute a high position )+ On chip address

3、 ... and 、I/O How to address the port

The main discussion is 8088/8086

Memory has 1MB, Ports have 64K individual

Unified addressing with memory

- Command and control signals are unified

- Memory address resources are reduced ( Because the port is given , So the address of the original memory is less , It can be understood that there is less memory )

Address independently

- Make full use of memory address resources

- There are fewer instructions that can be applied to ports

Addressing signal

I O R ‾ 、 I O W ‾ 、 A 15 ∼ A 0 \overline{IOR}、\overline{IOW}、A_{15}\sim A_0 IOR、IOW、A15∼A0

Four 、 decoding

Is to determine the port address .

Address signal

- Single port interface :16 Bit address lines participate in decoding , Directly select the port for decoding output .

- Multiple ports : High bit decoding , Determine the base address of the interface , The low order determines the port ( Chip selection ).

Simple interface circuit

One 、 Basic composition of the interface

- data input / Output register —— Temporary input / Output data .

- Command register —— Store control commands .

- Status register —— Save current state , for CPU Read .

Two 、 Types and characteristics of interfaces

According to different classification , There are different situations .

classification

- Direction :

- Input

- Output

- type :

- Numbers

- simulation

- The way :

- parallel

- Serial

characteristic

- Input interface : Data control 、 Tristate gate

- Output : Data latch 、 Latch

3、 ... and 、 Tristate gates and 74LS244

Tristate gate

The one in the middle , In fact, it is an input , It is used to control whether it is on or off .

74LS244

Four 、 Latch

D trigger

Look directly at the menu

74LS273

Pure is just one 8D trigger , Latch only , Don't control .

74LS374

Than 273 Better , Add the tristate gate , Achieve control .

It can be used as an input interface , It can also be used as an output interface .

Basic input / Output method

One 、 Unconditional transmission

It is required that peripherals are always ready .

advantage

The software and interface hardware are simple

shortcoming

Only for simple peripherals , Narrow adaptation range .

Two 、 How the query works

It is necessary to meet the conditions for data transmission , A single transmission corresponds to a single transmission condition .

Working conditions

Peripherals need to provide equipment status information .

The interface should have a status port .

advantage

The software and hardware are relatively simple

shortcoming

CPU Low efficiency , Poor real-time performance , Slow speed .

3、 ... and 、 Interrupt control mode

characteristic

peripherals When needed request ,CPU Then go to service , After service or when not needed ,CPU Execute your own program .

shortcoming

Program addressing is relatively complex .

advantage

CPU Efficient 、 Strong real time , Fast .

Three of the above I/O Mode commonality

- Information transmission shall be through CPU

- Software , Data transmission has been switched on CPU The execution procedure is completed (PIO The way ).

- Hardware : Read / write control signal 、 Address signals are generated by CPU Emitted .

- The disadvantage is The speed of data transmission Limited by The execution speed of the program .

Four 、DMA

characteristic

- Peripherals exchange data directly with memory .

- The bus is controlled by DMAC Control , Memory / The address and read / write control signal of the peripheral are controlled by DMAC Provide .(CPU Will give up bus control )

- Data transmission is performed by DMA Hardware control , Data is exchanged directly between memory and peripherals , The transmission rate is very high .

- Control is complex , High hardware cost .

Interrupt technology

One 、 The basic concept of interruption

interrupt

CPU When executing the program , Some random event occurs ( Inside or outside ), cause CPU Temporary interruption Running programs , Turn to execution Interrupt service subroutine , Deal with the incident , After that, the program that returns to the original interrupt continues to execute , The process is interrupt .

Interrupt source

cause CPU Interruptions .

classification

- Internal interruption

- Abnormal interruption —— Unusual events

- Software interrupt —— Interrupt instruction

- External interrupt

- Maskable interrupt ——INTR interrupt

- Unshielded interrupt ——NMI interrupt

Two 、 External interrupt response process

Interrupt request

- The request signal remains until Interrupts are handled until .

- CPU After response interruption , The request signal shall be cancelled in time .

Interrupt source identification

The two methods : Software query and interrupt vector method . This part is made up of hardware system complete .

Interrupt optimization

In fact, multiple interrupt requests occur at the same time , Which one should be responded to first Interrupt source .

Rule of excellence

Priority rule and Queuing rule .

Software optimization

Query requests by priority , Query first, service first .

Hardware Services —— Interrupt vector code

- Interrupt controller optimization ——8259A

- Chain judgement 、 Parallel optimization .

- Chrysanthemum chain , In fact, it is the condition of chain optimization , Each peripheral interrupt signal has a daisy link , The output of the daisy chain at the front will control the output of the daisy chain at the back .

Interrupt response

- To the interrupt source

~INTAInterrupt response signal . - Close the interrupt .

- Protect the hardware site .—— take FLAGS Push into the stack .

- Protect breakpoints —— take CS、IP Push into the stack .

- Get the interrupt service program entry address .

The above is completed by the hardware system .

Response conditions

- CPU Open the interrupt ,IF=1.

- No, RESET,HOLD, Internal interruption ,NMI.

- Currently executing STI and IRET, Need to complete .

Interrupt handling

Is to perform Terminal services subroutine ,“ Far process ”, IRET Command return .

Interrupt the work of the service subroutine

- Close the interrupt , Protection site , Protect breakpoints , Find the entrance address .

- Protect the software site ( Parameters ).

- Open the interrupt (STI)—— Allow nesting .

- Interrupt handling .

- Close the interrupt (CLT).

- Restore the scene .

- Interrupt return .

Interrupt return

Is to perform IRET Instructions , Then register IP、CS、FLAGS Pop... From the stack .( Restore breakpoints and hardware sites )

technological process

3、 ... and 、8088/8086 Interrupt the system

Interrupt vector table

- The entry address where the interrupt service subroutine is stored .

- Each entrance 4 individual Bytes, The high section is the base address of the section , The low bit is the offset address in the segment .

- The address of the table is located in the memory 000000H~003FFH, size 1KB, common 256 An entrance .

initialization

It is to put the user-defined interrupt service program entry address into the vector table .

Be careful :

- The segment address where the vector table is located =0.

- The offset address of the unit where the subroutine entry is stored =nx4.

The big one is coming

Programmable interrupt controller 8259A( difficulty )

According to the priority of the interrupt request, the CPU issue Interrupt request , And when the CPU After entering the interrupt service subroutine in response to the interrupt request , If a new external interrupt request has a higher priority than the current interrupt , Will execute a new interrupt , The original interrupt is masked first , Pause , Implement nested interrupts .

monolithic 8259A Ability to manage 8 Level interrupt .

One Pin and function structure

1 Chip pin definition

- D0~D7,8 Two way data line .

- ~WR, Write control signals , Low level active , Used to inform 8259A Prepare to receive data from the data line .

- ~RD, Read the control signal , Low level active .

- ~CS, Chip selection signal terminal , It is connected with the system address bus through the address decoding logic circuit , For gating 8259A.

- A0: Address line , Used to indicate the current 8259A The two ports that are accessed are

Strange address ( high 8 position )stillMy address ( low 8 position ),8088 even A0,8086 even A1. - IR0~IR7:8 Level interrupt request input .

- INT: Interrupt request signal .

- ~INT A: Interrupt answer line .

- SP/EN: Dual function bidirectional signal line , They represent two working modes : Buffer working mode 、 Master slave working mode .

- CAS0~CAS2:3 Root cascade control signal .

Two 、 Internal structure and interrupt workflow

Workflow

- An external interrupt source causes 8259A One or more interrupt request lines of the turn high .

- The highest priority requests that are not masked for these requests are from INT Output , Leave it to CPU Respond to .

- if CPU Open the interrupt , Execute the current procedure , Just use INTA As a response signal to 8259A Of INTA,8259A First interrupt response received ~INTA after , First the ISR The highest interrupt priority in the 1, then IRR Corresponding position in 0.

- 8259A Got the second ~INTA after , Type of the interrupt corresponding to this interrupt n from A register called interrupt type (

IMR) To the data line ,CPU Read n, Obtain the interrupt entry address corresponding to the interrupt according to the interrupt vector table , Then execute the corresponding interrupt service subroutine . - ISR Reset , according to

Mode controllerHow to end , YesEOIandAEOI.

3、 ... and 、 Control word format

ICW

Initialize command word , There are four , Respectively ICW1~ICW4.

OCW

Working mode command word or operation command word . There are three , The initialization command word must be set before writing 3 Corresponding registers . Dynamically operate and control the interrupt processing process .

flow chart

ICW1

Chip control initialization command , Should write Even address port , namely A0 by 0.

Write conditions :A0=0,CS=0, Characteristic bit D4=1.

- D0 Indicates whether to write ICW4

- D1 Express

monolithicstillcascade. - D3

High activestillThe rising edge is effective.

ICW2

Set up Interrupt type code Initialization command of .

Write conditions : With the ICW1 after ,CS*=0,A0=1.

- D7~D3: Specify the top five digits of the interrupt type code .

ICW3

Identify the main piece / Slave piece Initialize command word .

Write conditions : Cascade mode , With the ICW2 after ,CS=0,A0=1 And ICW1 Medium D1=0.

The master chip is connected with the slave chip IR Set up 1, From slice D2、D1、D0 Indicates the access to the main chip IR End coding .

Be careful : Master and slave ICW3 Must be different .

ICW4

Interrupt end mode initialization command word .

Write conditions :ICW2 or ICW3 after , And ICW1 Medium D0=1,D7~D5=0m,CS=0,A0=1.

- D4=1, Special fully nested .

- D4=0, Generally completely nested .

- D3, Set the buffer mode .

- D2, Set master-slave under buffer .

- D1, The setting takes you to the end .

- D0, Set the appropriate CPU System .

OCW1

Is to set the interrupt mask word , Write to interrupt mask register IMR in .1 Indicates shielding .

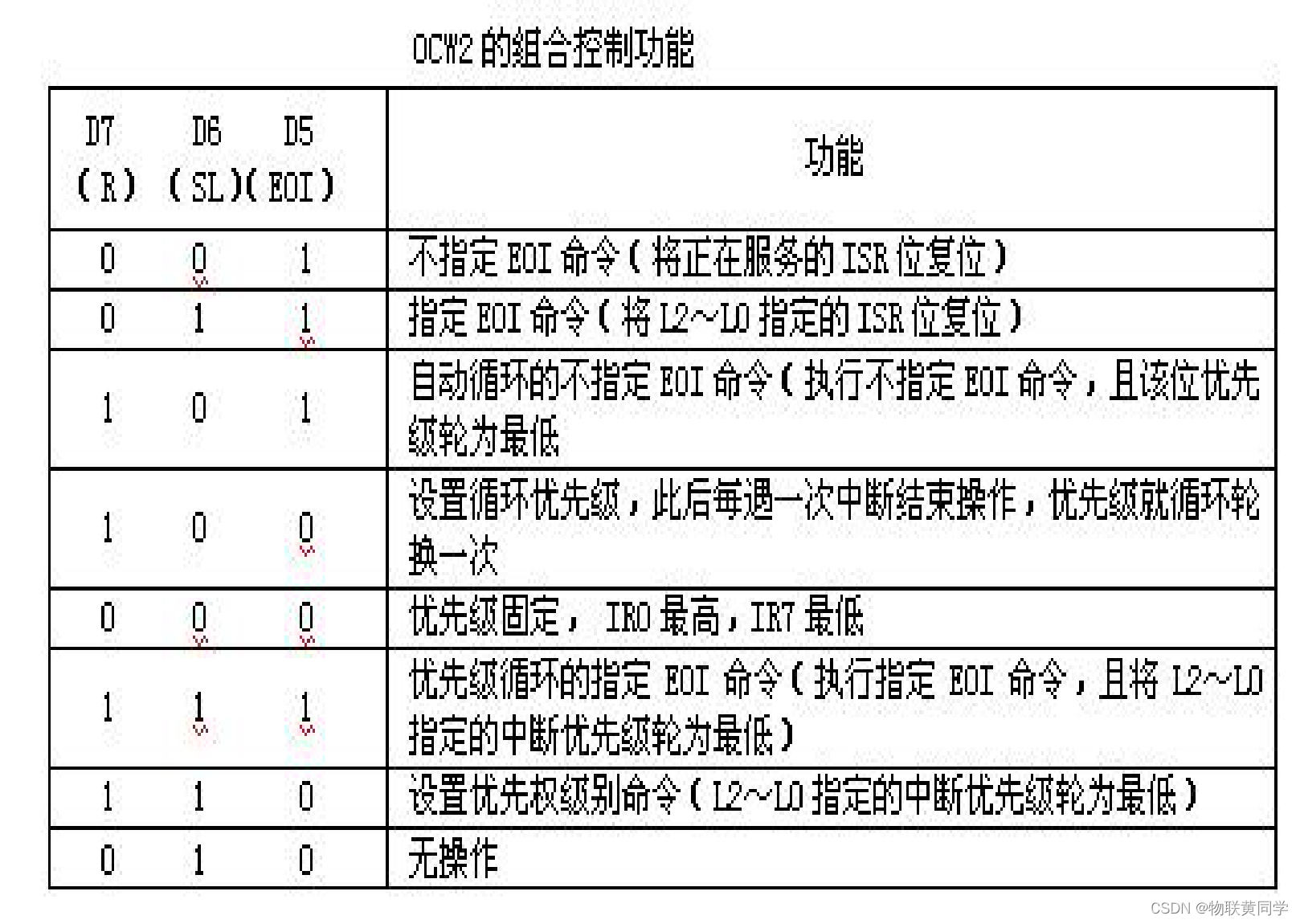

OCW2

A0=0.

OCW3 It is a multi-function operation command word , Used to control 8259A Interrupt mask and read register status .

All knock here , Let's have a compilation !

MOV AL,13H ; Write ICW1, monolithic , edge-triggered , want ICW4

OUT 20H,AL

MOV AL,8 ; Write ICW2, The interrupt type number is from 8 Start

OUT 21H, AL

MOV AL, 0DH ; Write ICW4, Buffer working mode ,8088/8086 To configure

OUT 21H, AL

MOV AL,0 ; Write OCW1, allow IR0~IR7 All 8 Level interrupt request

OUT 21H,AL

边栏推荐

- How the FortiGate firewall rejects a port by using the local in policy policy

- Slam mapping, automatic navigation and obstacle avoidance based on ROS (bingda robot)

- 两个月拿到N个offer,什么难搞的面试官在我这里都不算事

- Internship: interface case implementation

- Thingsboard tutorial (II and III): calculating the temperature difference between two devices in a regular chain

- OneNote production schedule

- Machine learning notes

- [learn FPGA programming from scratch -52]: high level chapter - FPGA development based on IP core - basic framework for IP core use (taking PLL as an example)

- An error occurs when sqlyog imports the database. Please help solve it!

- Technology sharing | broadcast function design in integrated dispatching

猜你喜欢

基于servlet+jsp+mysql实现的工资管理系统【源码+数据库】

Junior students summarize JS advanced interview questions

![[image fusion] multi focus and multi spectral image fusion based on cross bilateral filter and weighted average with matlab code](/img/9c/2553d192c2f9b93acc6550220c447f.png)

[image fusion] multi focus and multi spectral image fusion based on cross bilateral filter and weighted average with matlab code

DBT product initial experience

Threejs实现模拟河流,水面水流,水管水流,海面

基于SSM框架茶叶商城系统【项目源码+数据库脚本+报告】

Redis cache avalanche, breakdown and penetration

Day 9 script and resource management

MySQL DDL change

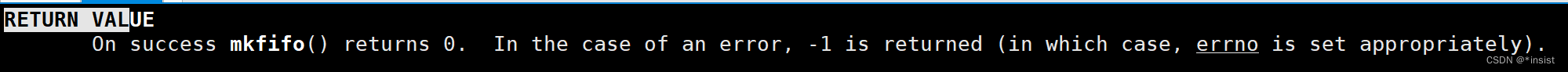

管道实现进程间通信之命名管道

随机推荐

SQLyog导入数据库时报错,求帮解决!

MySQL DDL change

Redis cache avalanche, breakdown and penetration

el-upload上傳文件(手動上傳,自動上傳,上傳進度)

进程间通信之匿名管道

Es2018 key summary

JS import and export

QT creator 8 beta2 release

Explain the underlying principles of JVM garbage collection in simple terms

What is the difference between synchronized and lock

Day 9 script and resource management

FortiGate firewall and Aruze cloud tunnel interruption

Thinkphp5 implements import function

Myrpc version 2

Find the interface and add parameters to the form

SQL error caused by entity class: Oracle "ora-00904" error: possible case of invalid identifier

数据链路层详解

MySQL updates JSON string in array form

A solution to the problem of "couldn't open file /mnt/repodata/repomd.xml"

[Thesis reading | deep reading] role2vec:role based graph embeddings