当前位置:网站首页>Mastering JESD204B (1) – Debugging of AD6676

Mastering JESD204B (1) – Debugging of AD6676

2022-07-30 07:38:00 【FPGA - Signal Processing】

Mastering JESD204B (1)-AD6676 debugging

Hardware Platform Description

The hardware platform mainly includes:

- Virtex7:690T-FFG1761;

- Zynq:XC7Z015-CLG485;

- AD chip: AD6676;

- Clock Chip: HMC7044.

System Requirements

The system mainly completes the configuration of the clock chip, completes the acquisition of 4 pieces of AD6676, and uploads the collected data through the Zynq network, and uploads it to the host computer and saves it as a file for subsequent data processing;

System part hardware diagram design

- Clock Design Section

- AD6676 hardware design

- FPGA receiving data hardware design

The next chapter will continue to explain the configuration of 204B

边栏推荐

猜你喜欢

随机推荐

图扑软件数字孪生民航飞联网,构建智慧民航新业态

2021-05-26

为数字政府构建智能化网络安全管控体系

Simple use of xftp

libgrape-lite on GPUs:GPU助力加速图分析任务

测试第二题

mysql数据库怎么设置手动提交

Devops基本概念和原理

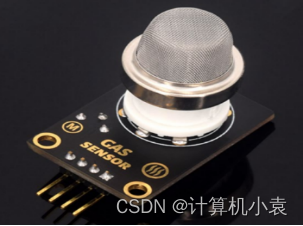

基于STM32F103的消防系统之MQ-4气体传感器

JSP自定义标签

Jenkins一些常见问题

关于memcache内核,全网最通俗的讲解

NS3 error fatal error: ns3/opengym-module.h: No such file or directory

GadgetInspector原理分析

掌握JESD204B(三)–AD6676的调试

C language, usage of qsort in library function, and explanation

网络协议03 - 路由和NAT

不依赖框架的文件下载

SQL并列排序问题

Vineyard: 开源分布式内存数据管理框架