当前位置:网站首页>[vcs+verdi joint simulation] ~ take the counter as an example

[vcs+verdi joint simulation] ~ take the counter as an example

2022-06-30 05:00:00 【AI is very good】

Contents of this chapter :

- 0. Preface

- 1. summary

- 2. from “0” Begin to learn

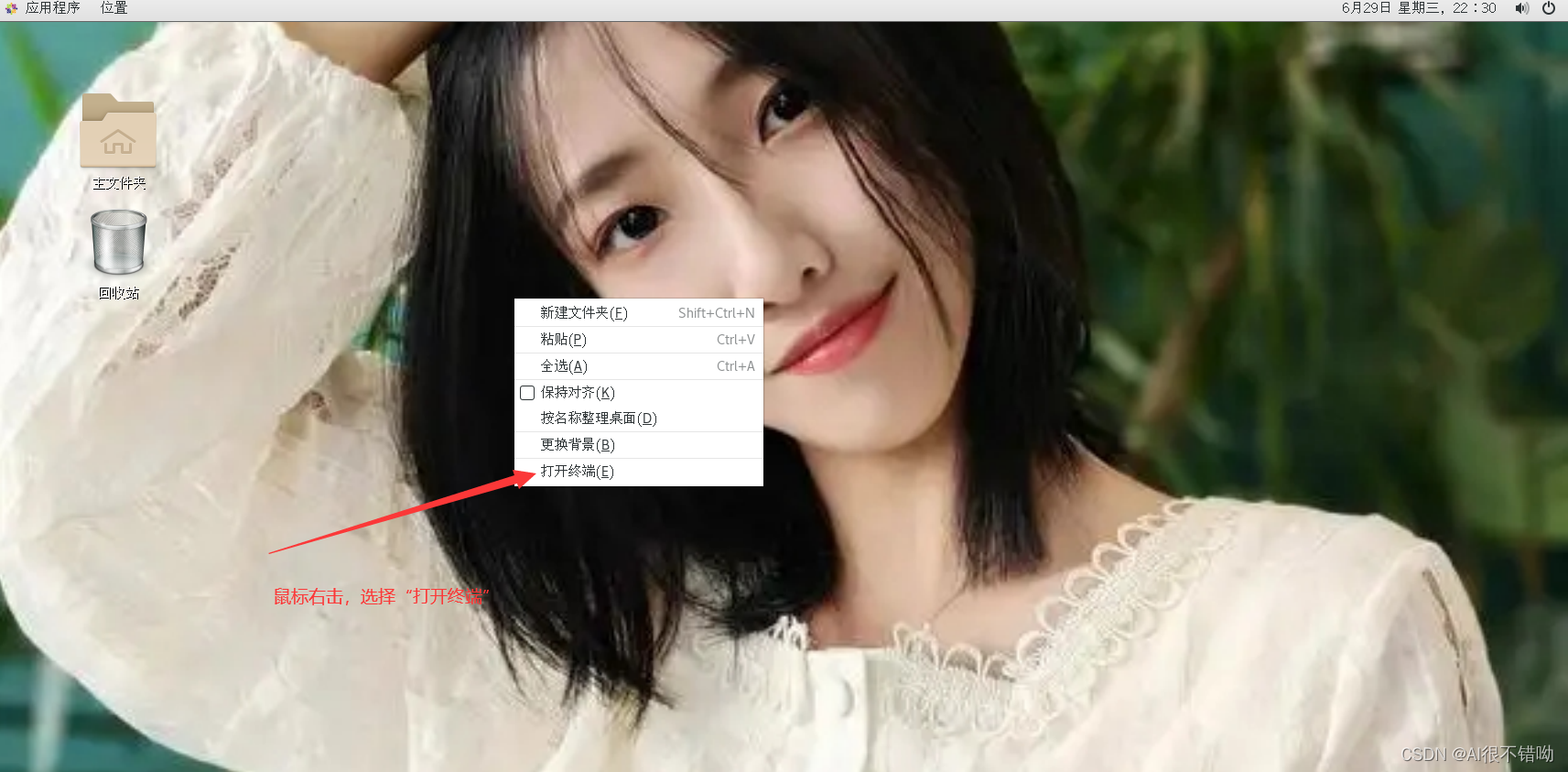

- 2.1 Enter virtual machine , choice “” Open the terminal

- 2.2 Create related files

- 2.2.1 adopt linux Command to create the corresponding file , Here I take the counter as an example , Need to create Counter Folder ,

- 2.2.2 stay Counter Create in folder 3 A folder

- 2.2.3 stay module Created in rtl Code

- 2.2.4 stay tb Create test code in

- 2.2.5 stay verification in file_list And script files

- 2.3 everything , Just under run

- 2.4 Good habit after the event

- 3. summary

0. Preface

First , Say it first , When I wrote this blog, I was a pure white , No secret , Just learned for a day , Ha ha ha , you 're right , You read that right , Is a day !!! Mainly because the day before yesterday, I had to brush questions and find a job , Need familiarity VCS and Verdi Joint simulation of ( It is said to be very easy to use , Follow the crowd !!!), So there will be some related blogs in the future , I'm going to turn it into a column , So that there are friends in need , Make a reference , Don't talk much , Let's go straight to work .

1. summary

I believe you have more or less touched one or more EDA Related software , You're like Vivado,Quartus, They all contain RTL, compile , Simulation , comprehensive , Look at the waveform , Board burning and other functions . Then why not use this ? Is there a problem with the company ??? ha-ha , You are being paranoid. , The company is ten to twenty years ahead of our school , So , There is nothing wrong with learning from the company . take the reverse into consideration VCS and Verdi It's very single-minded ,VCS Focus on Compilation and simulation ,Verdi Focus on the waveform . Then there VCS Compiling simulation is extremely fast , Very efficient , Save time for everyone ,Verdi It is also very convenient to see the waveform debug, It supports signal tracing , Seamless addition of signal waveform and other functions .

2. from “0” Begin to learn

Environmental Science : CentOS7

Code writing : Vim

Compile simulation : VCS

Waveform view : Verdi

About virtual machine installation, please move to my other blog , Portal

About VCS and Verdi relevant EDA I can get the installation of tools in the comment area or in private chat .

=============================================================================================

All right, let's move on ===>

Default here VCS and Verdi The environment has been set up , Refer to my blog for configuration environment ,.bashrc Configuration of files

2.1 Enter virtual machine , choice “” Open the terminal

2.2 Create related files

2.2.1 adopt linux Command to create the corresponding file , Here I take the counter as an example , Need to create Counter Folder ,

( Pay attention to is ,Linux The portal is here , Click on the portal )

$cd _Project/ # cd Folder name

# Below is my folder _Project The files inside

# Counter

2.2.2 stay Counter Create in folder 3 A folder

mkdir module tb verification # establish 3 File , The name is module、tb、 verification

# Below is the result

drwxrwxr-x. 2 ICer ICer 23 6 month 29 17:43 module

drwxrwxr-x. 2 ICer ICer 27 6 month 29 17:55 tb

drwxrwxr-x. 2 ICer ICer 39 6 month 29 21:03 verification

2.2.3 stay module Created in rtl Code

vim counter.v # adopt vim The editor creates counter.v file

# For the corresponding code writing process, you can refer to vim Look at the use of , When I have time to write an article about vim Articles used , According to your needs , Let me know if there is any comment area !!!

After writing the code :

1 module counter(

2 input clk,

3 input rst,

4 output reg [5:0] count

5 );

6

7 always @ (posedge clk or negedge rst) begin

8 if(!rst) begin

9 count <= 0;

10 end

11 else begin

12 count <= count + 1;

13 end

14 end

15 endmodule

2.2.4 stay tb Create test code in

vim tb.sv # adopt vim establish tb.sv file

After writing the code :

1 module tb_counter();

2

3 reg clk,rst;

4 wire [5:0] counter;

5

6 counter u1(clk,rst,counter);

7

8 always #(5) clk = ~clk;

9

10 initial begin

11 clk <= 0;

12 rst <= 0;

13 #20;

14 rst <= 1;

15 #50;

16 if(counter != 5)

17 $display("Failure 1: the counter should be 5 but it is %d",counter);

18 else

19 $display("You gotta the right result!");

20 $finish;

21 end

22

23 //.v file

24 //`ifdef FSDB

25 //initial begin

26 // $fsdbDumpfile("tb_counter.fsdb");

27 // $fsdbDumpvars;

28 //end

29 //`endif

30

31 //.sv file

32 initial begin

33 $fsdbDumpfile("tb.fsdb");

34 $fsdbDumpvars;

35 end

36 endmodule

2.2.5 stay verification in file_list And script files

# This file may not be suffixed , The main function is to organize the front rtl Path to code and test files , Convenient for script file calling

vim file_list

# This file is a script file , adopt make Instruction call ( Let's see Makefile Use , I have a document here , You can leave a message in the same private message or comment area )

# Its function is to plan and schedule the running sequence of all files , He is a big brother

vim Makefile

After writing the code :

all: \

3 vcs \

4 verdi

5

6 #-------------------------------------------------------------------------------------------------------

7 # VCS

8 vcs :

9 vcs \

10 -f file_list \

11 -timescale=1ns/1ns \

12 -full64 -R +vc +v2k -sverilog -debug_access+all \

13 |tee vcs.log

14 #-------------------------------------------------------------------------------------------------------

# verdi

34

35 verdi :

36 verdi -sv -f file_list -ssf tb.fsdb &

37

38 #-------------------------------------------------------------------------------------------------------

39 clean :

40 rm -rf *~ core csrc simv* vc_hdrs.h ucli.key urg* *.log novas.* *.fsdb* verdiLog 64* DVEfiles *.vpd

41 rm -rf INCA_libs irun*

42 rm -rf modelsim.ini transcript work

2.3 everything , Just under run

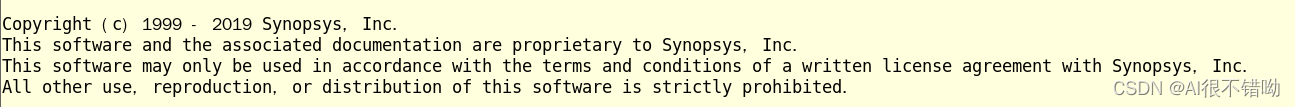

2.3.1 function vcs

$make vcs # adopt make Instruction call Makefile function vcs

Running results :

What is marked in the picture is the original , The rest are generated by simulation , Terror no ??? Ha ha ha , Just get used to it

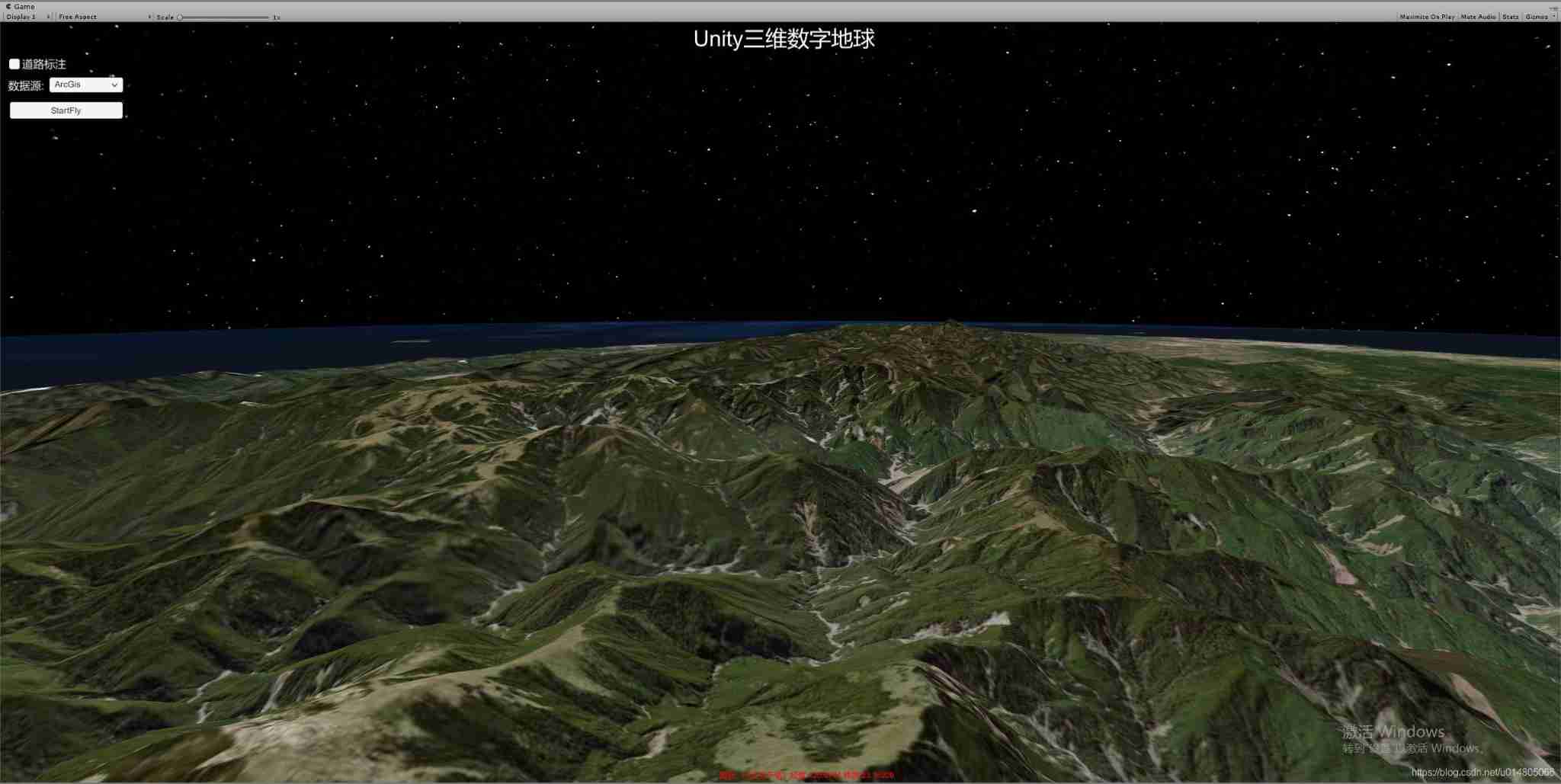

2.3.2 function verdi

make verdi # adopt make Instruction call Makefile function verdi

Running results :

No waveform ???

There's one more step , Is to add the signal you want to observe , Just look at the picture below .

That's the end of it ? What about? , Did you stop learning ?

Put the abandoned students in the comment area !!!

2.4 Good habit after the event

After reading the waveform , A lot of files have been generated before ? You can't clean up ! You have to tidy up after dinner , To do ?

Don't forget Makefile In the end, there is no clean Instructions ? Dry is finished !!!

make clean # Clean up the generated files

result :

Only the files before our simulation are left !!!

3. summary

Through this day's study , You really don't have to say ,vcs and verdi Joint simulation is really easy to use , Come here , I haven't learned enough , Just a little bit of fur , You have to keep learning , Refer to the strengths of others , I hope you can learn together , Common progress , If there is a mistake , Welcome criticism !!!

Okay , End of the flower , Duoduo Sanlian , Continuous updating .

=========================================================================

To be continued …

边栏推荐

- [UGV] schematic diagram of UGV version 32

- 【Paper】2017_ Distributed control for high-speed trains movements

- Error about the new version of UE4: unavigationsystemv1:: simplemovetoactor has been deprecated

- 力扣292周赛题解

- Have a heart beating Valentine's day in Singapore

- JPA复合主键使用

- UE4 method of embedding web pages

- 003-JS-DOM-Attr-innerText

- The golden deer, a scenic spot in London -- a sailing museum that tells vivid sailing stories

- One command to run rancher

猜你喜欢

【Paper】2019_ Distributed Cooperative Control of a High-speed Train

Procedural animation -- inverse kinematics of tentacles

力扣589:N 叉树的前序遍历

Unity3d Google Earth

Approaching history, introduction to the London Guard Museum

Efficiency test of adding and querying ArrayList and LinkedList

LxC and LXD container summary

![[UGV] schematic diagram of UGV version 32](/img/4b/03471d2cc96be5d57c97fd1c4e17dc.jpg)

[UGV] schematic diagram of UGV version 32

Solution to Autowired annotation warning

MySQL查询小工具(一)json格式的字符串字段中,替换json数组中对象的某个属性值

随机推荐

Malignant bug: 1252 of unit MySQL export

One interview question and one joint index every day

003-JS-DOM-Attr-innerText

Solution to 293 problems in the week of Li Kou

Sailing experience not to be missed in New York Tourism: take you to enjoy the magnificent city scenery from different perspectives

Webots notes day 2

力扣349. 两个数组的交集

Unit screenshot saved on the phone

Unity realizes rotation and Revolution

Unrealeengine4 - about uobject's giant pit that is automatically GC garbage collected

Unreal 4 learning notes - set player birth point

Qos(Quality of Service)

Force buckle 27 Removing Elements

力扣292周赛题解

Force buckle 59 Spiral matrix II

Harbor API 2.0 query

Connect to the database and run node JS running database shows that the database is missing

Basic operations of Oracle data

Autowired注解警告的解决办法

【Paper】2015_ Coordinated cruise control for high-speed train movements based on a multi-agent model