当前位置:网站首页>FPGA question brushing sequence detection

FPGA question brushing sequence detection

2022-07-26 05:19:00 【Juanshi】

Verilog The quick start has all been brushed , See the main page. FPGA Brush problem (1)~(5)

Start today Verilog Advanced challenges , The sequence detection part includes 4 Problem :

Catalog

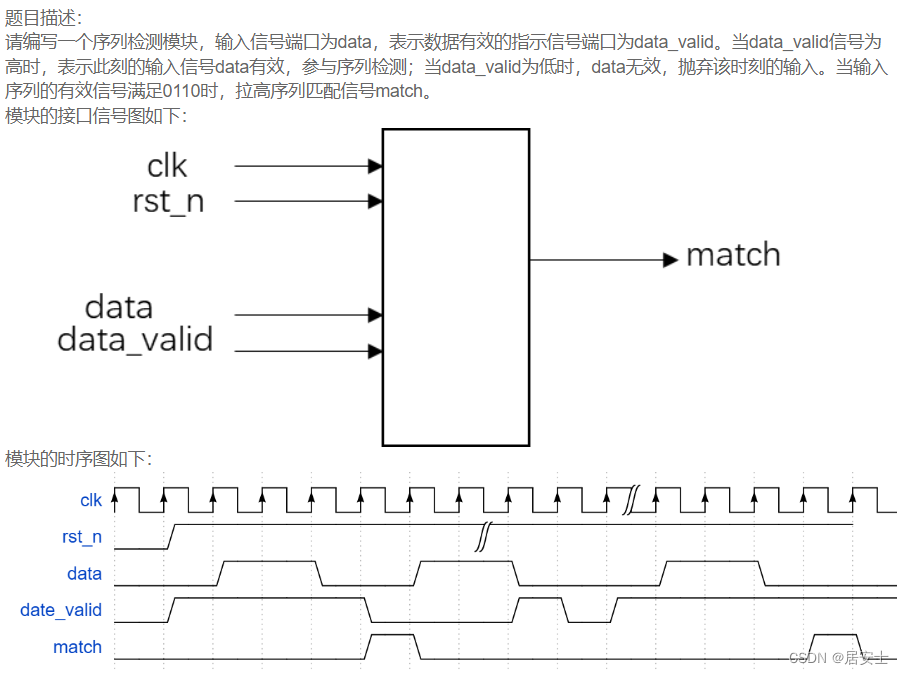

Input sequence continuous sequence detection

Sequence detection with irrelevant items

Non overlapping sequence detection

Input sequence continuous sequence detection

Input sequence continuous sequence detection

For sequence detection problems , There are two conventional solutions : State machine method and sequence cache comparison method .

The process of state machine method is similar to the process mentioned in topic meaning understanding : In the initial state , First, judge whether the first one meets , If it conforms, it will enter the next state , Judge whether the second place meets ; If the first one does not comply, it will remain in the initial state , Until the first one matches . If the first two match , Then judge whether the third place meets , If the first digit matches , The newly entered value does not match the second digit of the target sequence , Then according to whether the latest bit matches the first bit , Enter the first matching state or initial state . By analogy .

Sequence cache comparison method , Is to cache the data for eight moments , As an array , The input of each time is at the end of the array , Move other elements of the array to the left , Remove the earliest input data . Then compare the array with the target sequence , If the array and the target sequence are equal , Then the target sequence appears .

The sequence cache comparison method is relatively simple in implementation , This problem is realized by this method . First declare an array , Cache eight moments a The value entered . Shift can be achieved by bit interception and bit splicing :a_tem[6:0] To intercept a_tem It's low 7 position ,{a_tem[6:0],a} Express the a_tem[6:0] And the newly entered value a Splicing ,a In the low position .

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

reg[7:0]a_reg;

[email protected](posedge clk or negedge rst_n)begin

if(~rst_n)begin

a_reg<=8'd0;

end

else begin

a_reg<={a_reg[6:0],a};

end

end

[email protected](posedge clk or negedge rst_n)begin

if(a_reg==8'b01110001)begin

match<=1'd1;

end

else begin

match<=1'd0;

end

end

endmoduleSequence detection with irrelevant items

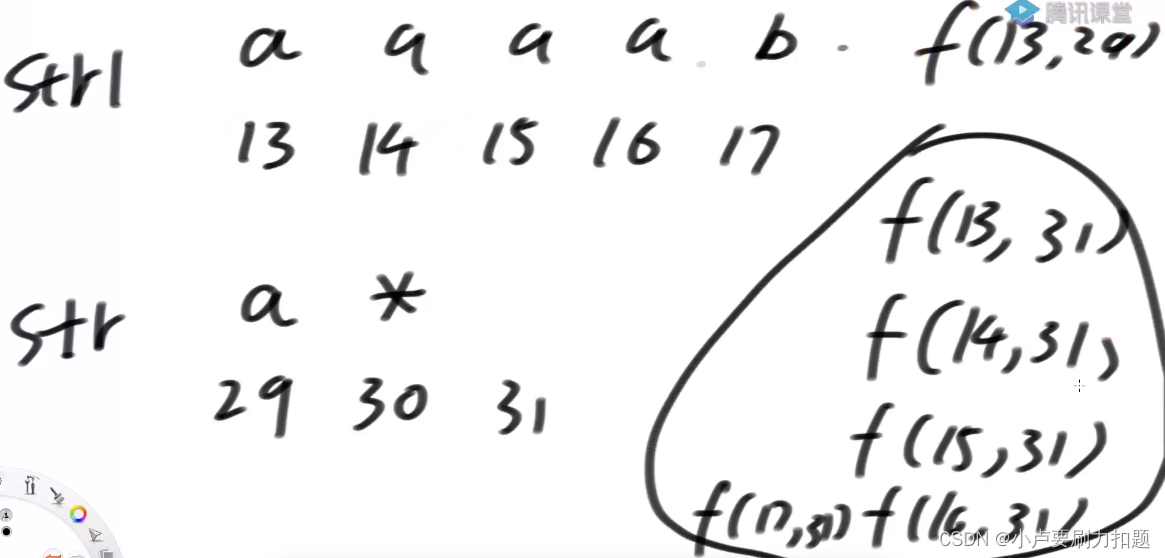

The title requires testing a Sequence ,a For single bit Input , Each moment may have different values , The title requires testing the top three and the bottom three , It is not required to detect the middle three , If you put the middle XXX, List separately :000,001,010,011,100,101,110,111, Test separately , The code is too cumbersome , Consider detecting the top three and the bottom three respectively , Sequence detection divided into two small segments . When the current three bit signal and the last three bit signal match at the same time , Match the signal match pull up .

Cache the data of nine moments , As an array , The input of each time is at the end of the array , Move other elements of the array to the left , Remove the earliest input data . Then intercept the first three digits of the array and the target sequence 011 contrast , Intercept the last three digits of the array and the target sequence 110 contrast , If both arrays are equal to the target sequence , Then the target sequence appears .

module sequence_detect(

input clk,

input rst_n,

input a,

output match

);

reg [8:0] a_reg;

reg match_1;

reg match_0;

[email protected](posedge clk or negedge rst_n)begin

if(~rst_n)begin

a_reg<=9'd0;

end

else begin

a_reg<={a_reg[7:0],a};

end

end

[email protected](posedge clk or negedge rst_n)begin

if(~rst_n)begin

match_1<=1'd0;

end

else if(a_reg[8:6]==3'b011)begin

match_1<=1'd1;

end

else begin

match_1<=1'd0;

end

end

[email protected](posedge clk or negedge rst_n)begin

if(~rst_n)begin

match_0<=1'd0;

end

else if(a_reg[2:0]==3'b110)begin

match_0<=1'd1;

end

else begin

match_0<=1'd0;

end

end

assign match = (match_1) && (match_0);

endmoduleNon overlapping sequence detection

The title requires testing a Sequence ,a For single bit Input , Each moment may have different values , When six consecutive input values match the target sequence, the sequence matches , When one or more of the six input values do not match, the sequence does not match .

It is worth noting that : The title requires six digit data as a group , Different from common sequence detection , Repeat sequence detection is required , Pay attention when drawing the state transition diagram , For example, the first digit does not match , You should not return to the initial state to make the first judgment , Because the input at this time is the second digit , The question requires that this value should not be judged , You need to wait until after six clock cycles , That is, the seventh data ( The first digit of the second set of values ) Then judge whether it matches the first bit of the target sequence .

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

parameter ZERO=0, ONE=1, TWO=2, THREE=3, FOUR=4, FIVE=5, SIX=6, FAIL=7;

reg [2:0] state, nstate;

reg [2:0] cnt;

[email protected](posedge clk or negedge rst_n) begin

if(~rst_n)

cnt <= 0;

else

cnt <= cnt==6? 1: cnt+1;

end

[email protected](posedge clk or negedge rst_n) begin

if(~rst_n)

state <= ZERO;

else

state <= nstate;

end

[email protected](*) begin

if(~rst_n)

nstate = ZERO;

else

case(state)

ZERO : nstate = data? FAIL : ONE;

ONE : nstate = data? TWO : FAIL;

TWO : nstate = data? THREE: FAIL;

THREE: nstate = data? FOUR : FAIL;

FOUR : nstate = data? FAIL : FIVE;

FIVE : nstate = data? FAIL : SIX;

SIX : nstate = data? FAIL : ONE;

FAIL : nstate = cnt==6&&data==0? ONE: FAIL;

default: nstate = ZERO;

endcase

end

[email protected](*) begin

if(~rst_n) begin

match = 0;

not_match = 0;

end

else begin

match = cnt==6&&state==SIX;

not_match = cnt==6&&state==FAIL;

end

end

endmodule

Input sequence continuous sequence detection

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

reg [3:0] pstate,nstate;

parameter idle=4'd0,

s1_d0=4'd1,

s2_d01=4'd2,

s3_d011=4'd3,

s4_d0110=4'd4;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

pstate<=idle;

else

pstate<=nstate;

end

always @(pstate or data or data_valid)

begin

case(pstate)

idle:

if(data_valid && !data)

nstate=s1_d0; // The first bit matches

else

nstate=idle;

s1_d0:

if (data_valid)

begin

if (data) nstate = s2_d01; // The data is valid and 1, The first two 01 matching , The next state is s2_d01

else nstate = s1_d0; // The data is valid but 0, That is, only the first 0 matching , The next state is s1_d0

end

else nstate = s1_d0; // Invalid data , Stay in s1_d0

s2_d01:

if (data_valid)

begin

if (data) nstate = s3_d011; // The data is valid and 1, That is, the top three 011 matching , The next state is s3_d011

else nstate = s1_d0; // The data is valid but 0, That is, only the first 0 matching , The next state is s1_d0

end

else nstate = s2_d01; // Invalid data , Stay in s2_d01

s3_d011:

if (data_valid)

begin

if (!data) nstate = s4_d0110; // The data is valid and 0, That is, the top four 0110 matching , The next state is s4_d0110

else nstate = idle; // The data is valid but 1, That is, it does not match , The next state is idle

end

else nstate = s3_d011; // Invalid data , Stay in s3_d011

s4_d0110:

if (data_valid)

begin

if (!data) nstate = s1_d0; // The data is valid and 0, That is, match the first bit of the target sequence 0, The next state is s1_d0

else nstate = idle; // The data is valid but 1, Does not match the target sequence , The next state is idle

end

else nstate = idle; // Invalid data , The next state is idle

default:

nstate=idle;

endcase

end

always @(pstate or rst_n)

begin

if(!rst_n==1)

match=1'b0;

else if(pstate==s4_d0110) // Enter the state of s4_d0110 Indicates that all four bits of data match , Match the indication signal match pull up

match=1'b1;

else

match=1'b0;

end

endmodule边栏推荐

- ABAP grammar learning (ALV)

- YOLOv5执行全过程----目录

- 测试用例评审如何开展

- Shell read read console input, use of read

- Getting started with ALV

- Excel VBA: realize automatic drop-down filling formula to the last line

- NetCore MySql The user specified as a definer (‘admin‘@‘%‘) does not exist

- Recommend 12 academic websites for free literature search, and suggest to like and collect!

- Simulation of future air pollution changes

- Why is the value represented by a negative number greater than an integer by 1?

猜你喜欢

87. 扰乱字符串

Nacos registry

NetCore MySql The user specified as a definer (‘admin‘@‘%‘) does not exist

攻防世界--easy_web

![[pytorch] install torch 1.8.1 and check whether torch version and GPU are available](/img/97/078c72729a29675939a84895b5ab86.png)

[pytorch] install torch 1.8.1 and check whether torch version and GPU are available

没背景、没学历?专科测试员进入互联网大厂是不是真的没希望?

Day011 一维数组

第二讲 初识SLAM

MODFLOW flex, GMS, FEFLOW, hydraus practical application

10. 正则表达式匹配

随机推荐

ALV program collection

Common modules in ansible

MySQL eight knowledge points: from getting started to deleting the database

Recommendation system - machine learning

An online accident, I suddenly realized the essence of asynchrony

Shell process control (emphasis), if judgment, case statement, let usage, for ((initial value; loop control condition; variable change)) and for variable in value 1 value 2 value 3..., while loop

@Principle of Autowired annotation

Yolov5 implementation process - Directory

[Luogu] p1383 advanced typewriter

C language - Advanced pointer

ALV报表流程图解

Compilation method of flood control evaluation report and flood modeling under the new guidelines

C语言力扣第41题之缺失的第一个正数。两种方法,预处理快排与原地哈希

Why is the value represented by a negative number greater than an integer by 1?

Meta analysis [whole process, uncertainty analysis] method based on R language and meta machine learning

unity场景跳转脚本

Computable general equilibrium (CGE) model practice technology in resource environment under the goal of "double carbon"

测试必备工具之Fiddler,你真的了解吗?

Excel vba: saving multiple worksheets as new files

Mathematical modeling and optimization analysis based on general optimization software gams