当前位置:网站首页>Understand chisel language. 27. Chisel advanced finite state machine (I) -- basic finite state machine (Moore machine)

Understand chisel language. 27. Chisel advanced finite state machine (I) -- basic finite state machine (Moore machine)

2022-07-27 09:41:00 【github-3rr0r】

Chisel Advanced finite state machine ( One )—— Basic finite state machine

Finite state machine (FSM,Finite-State Machine) It is the basic building block in digital design , Many state logic in digital design can be abstracted as FSM. This part will be for FSM Of Chisel Implementation is introduced in detail , In addition to the basic finite state machine (Moore Finite state machine ) outside , Can also learn Mealy Finite state machine and and compare the two . This article first introduces Moore Finite state machine .

Finite state machine

Finite state machine , namely FSM, Can describe a set of States (states) Conditional state transition between States (state transitions).FSM There is an initial state , It will be set when resetting . and FSM And a name , It is called synchronous sequential circuit , Does it sound familiar , you 're right , In essence, all synchronous sequential circuits can be abstracted as finite state machines .

One FSM The implementation of requires three parts :

- A register that stores the current state ;

- A combinational logic circuit that calculates the next state based on the current state and the input signal ;

- Calculation FSM Combination logic of output .

In principle , Any digital circuit containing a register or other memory element for storing state can be described by a single finite state machine . However, this is not realistic , For example, if you want to use a single FSM It would be ridiculous to describe our computer . So this part still introduces a single FSM, And the next part will introduce the too small FSM The combination of builds greater communication FSM.

Basic finite state machine

The basic finite state machine is also called Moore Finite state machine , The picture below is FSM Schematic diagram :

As shown in the figure , The register contains the current state state, Next state calculation logic Next state logic Or according to the current state And the input in To calculate the next state nextState, In the next cycle ,nextState It becomes state. Output logic Output logic Accounting output out, Because the output here only depends on the current state , Once your state machine is called Basic finite state machine , It's also called Moore machine .

State transition diagram (State Diagram) Visually describe FSM act , In the state transition diagram , Each state is depicted as a circle labeled with the state name , State transitions are represented by arrows between States . The conditions for executing a transition are given in the form of labels on the arrows of the state transition . Here is a FSM Example of state transition diagram :

This FSM There are three states :green、orange and red, Indicates different levels of warnings .FSM from green The state begins , If one bad event coming , The warning level will be changed to orange, If the second happens bad event, Then further convert to red, At this time, we hope to ring ,ring bell yes FSM Unique output , We add the output to red In state , If you receive clear The signal , The warning level will be reset to green.

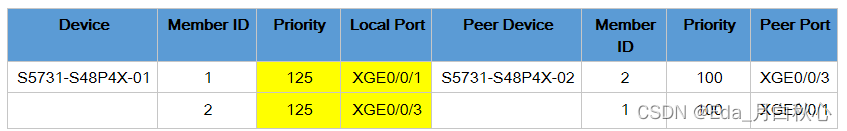

Although the state transition diagram can be visually described FSM The function of , It looks very comfortable , It's easy to master , But state transition tables are faster to write when used to write code . The following table warns on the above FSM State transition table :

The next state corresponding to different current states and input values and the output corresponding to the current state are listed in the table . In principle , We need to list all the possibilities of all States , Then this watch will have 3 × 4 = 12 3\times 4=12 3×4=12 That's ok . But we can simplify it a little , For example if bad event When it happened ,clear The signal is ignored , in other words bad event Than clear There is a higher priority . There are some repetitions in the output column , If our FSM Larger or more output , Then we can draw two tables , One for the next state logic , The other is for output logic .

After designing the warning level FSM after , We can use it Chisel The code is written , The complete code is as follows :

// package my.hello

import chisel3._

import chisel3.util._

class SimpleFsm extends Module {

val io = IO(new Bundle {

val badEvent = Input(Bool())

val clear = Input(Bool())

val ringBell = Output(Bool())

})

// FSM Three states of

val green :: orange :: red :: Nil = Enum(3)

// Status register

val stateReg = RegInit(green)

// State transition logic

switch (stateReg) {

is (green) {

when(io.badEvent) {

stateReg := orange

}

}

is (orange) {

when(io.badEvent) {

stateReg := red

} .elsewhen(io.clear) {

stateReg := green

}

}

is (red) {

when(io.clear) {

stateReg := green

}

}

}

// Output logic

io.ringBell := stateReg === red

}

object MyModule extends App {

println(getVerilogString(new SimpleFsm()))

}

Let's explain the code :

- Because we need to use Chisel Of

EnumThe type andswitchControl command , So you need to importimport chisel3.util._; - We use both input and output Chisel Of

Booltype ; - This FSM There are two inputs and one output signal , All contained in a

IOOfBundleInside , This structure has been mentioned many times before ; - Many works have studied optimal state coding , The two common choices are binary coding or single hot coding , But we are Chisel Choose to leave these low-level decisions to the integrated tool , We are only responsible for writing readable code , So we used

Enumclass , Symbolic names are also used to represent states :val green :: orange :: red :: Nil = Enum(3)( Current version ChiselEnumBinary code is still used , If you want to use exclusive coding, you can define it yourself Chisel Constant ); - And then the last one , These states are described as a list , Elements are connected by operators

::Connect ,NilIndicates the end of the list , Then one ChiselEnumInstance of type Assigned to This status list ; - The reset value is given when defining the register storing status information :

val stateReg = RegInit(green); - FSM The focus of is the next state logic , Here we use Chisel Of

switchstructure , Covers all States , At everyisInside the branch , We are all based on input , The next state logic is realized by assigning a new state to the state register ; - Finally, output logic , That is, when the value of the status register is

redWhenringing bell, There's nothing to say about this .

It should be noted that , We didn't introduce one for the register next_state The signal , Because in Verilog and VHDL That's what it does inside . stay Verilog and VHDL Inside , Registers are described in special syntax , Cannot be assigned and reassigned by a combinational logic block . therefore , The extra signal is directly connected to the input of the register after being calculated by the combinational logic block . But in the Chisel The register inside is a basic type , It can be used casually in combinational logic blocks .

Conclusion

This article introduces the basic finite state machine (FSM), namely Moore machine , The corresponding output is a finite state machine that only relates to the current state , In the next article, we will learn about the state machine whose output depends on input , namely Mealy Finite state machine , Through the example of rising edge detection , It will be further compared Moore Machine and Mealy The difference between machines .

边栏推荐

- July training (day 17) - breadth first search

- 七月集训(第15天) —— 深度优先搜索

- Google Earth engine app - print the coordinates of points to the console and map, set the style and update it

- Sentinel 万字教程 | 文末送书

- July training (day 18) - tree

- Talk about 10 scenarios of index failure. It's too stupid

- C# 给Word每一页设置不同文字水印

- 深度剖析分库分表最强辅助Sharding Sphere

- 七月集训(第21天) —— 堆(优先队列)

- 如何使用TDengine Sink Connector?

猜你喜欢

随机推荐

flash闪存使用和STM32CUBEMX安装教程【第三天】

吃透Chisel语言.23.Chisel时序电路(三)——Chisel移位寄存器(Shift Register)详解

c'mon! Please don't ask me about ribbon's architecture principle during the interview

【武汉理工大学】考研初试复试资料分享

七月集训(第16天) —— 队列

七月集训(第21天) —— 堆(优先队列)

七月集训(第08天) —— 前缀和

吃透Chisel语言.24.Chisel时序电路(四)——Chisel内存(Memory)详解

At the end of the year, I'll teach you how to get high performance!

工程材料知识点总结(全)

刷题《剑指Offer》day04

BGP federal experiment

深度剖析分库分表最强辅助Sharding Sphere

July training (day 06) - sliding window

注解与反射

九种方式,教你读取 resources 目录下的文件路径

【云原生 • DevOps】一文掌握容器管理工具 Rancher

七月集训(第17天) —— 广度优先搜索

七月集训(第06天) —— 滑动窗口

Interviewer: what is scaffolding? Why do you need scaffolding? What are the commonly used scaffolds?