当前位置:网站首页>QEMU ARM interrupt system architecture 2

QEMU ARM interrupt system architecture 2

2022-06-22 05:40:00 【alex_ mianmian】

I'd like to list the log here to help the understand of the process.

GPIO_IN initialize API is :

void qdev_init_gpio_in(DeviceState *dev, qemu_irq_handler handler, int n)

{

qdev_init_gpio_in_named(dev, handler, NULL, n);

}

static inline void qdev_init_gpio_in_named(DeviceState *dev,

qemu_irq_handler handler,

const char *name, int n)

{

qdev_init_gpio_in_named_with_opaque(dev, handler, dev, name, n);

}

void qdev_init_gpio_in_named_with_opaque(DeviceState *dev,

qemu_irq_handler handler,

void *opaque,

const char *name, int n)

{

int i;

NamedGPIOList *gpio_list = qdev_get_named_gpio_list(dev, name);

assert(gpio_list->num_out == 0 || !name);

gpio_list->in = qemu_extend_irqs(gpio_list->in, gpio_list->num_in, handler,

opaque, n);

.....

gpio_list->num_in += n;

}

qemu_irq *qemu_extend_irqs(qemu_irq *old, int n_old, qemu_irq_handler handler,

void *opaque, int n)

{

qemu_irq *s;

int i;

if (!old) {

n_old = 0;

}

s = old ? g_renew(qemu_irq, old, n + n_old) : g_new(qemu_irq, n);

for (i = n_old; i < n + n_old; i++) {

s[i] = qemu_allocate_irq(handler, opaque, i);

}

return s;

}

qemu_irq qemu_allocate_irq(qemu_irq_handler handler, void *opaque, int n)

{

struct IRQState *irq;

irq = IRQ(object_new(TYPE_IRQ));

irq->handler = handler;

irq->opaque = opaque;

irq->n = n;

printf("alexdebug:%s irq at %p, n is %d\n",__func__,irq,n);

return irq;

}1. ARM CORE GPIO_IN irq creation.

static void arm_cpu_initfn(Object *obj)

{

ARMCPU *cpu = ARM_CPU(obj);

.....

qdev_init_gpio_in(DEVICE(cpu), arm_cpu_set_irq, 4);

.....

}The log is:

alexdebug:qemu_allocate_irq irq at 0x7fffbe6b4480, n is 0

alexdebug:qemu_allocate_irq irq at 0x7fffbe6644c0, n is 1

alexdebug:qemu_allocate_irq irq at 0x7fffbe6702c0, n is 2

alexdebug:qemu_allocate_irq irq at 0x7fffbe66fbe0, n is 32. GIC GPIO_IN irq creation

static void arm_gic_realize(DeviceState *dev, Error **errp)

{

GICState *s = ARM_GIC(dev);

.....

gic_init_irqs_and_mmio(s, gic_set_irq, gic_ops, gic_virt_ops);

.....

}

void gic_init_irqs_and_mmio(GICState *s, qemu_irq_handler handler,

const MemoryRegionOps *ops,

const MemoryRegionOps *virt_ops)

{

SysBusDevice *sbd = SYS_BUS_DEVICE(s);

int i = s->num_irq - GIC_INTERNAL;

/* For the GIC, also expose incoming GPIO lines for PPIs for each CPU.

* GPIO array layout is thus:

* [0..N-1] SPIs

* [N..N+31] PPIs for CPU 0

* [N+32..N+63] PPIs for CPU 1

* ...

*/

i += (GIC_INTERNAL * s->num_cpu);

qdev_init_gpio_in(DEVICE(s), handler, i);

for (i = 0; i < s->num_cpu; i++) {

sysbus_init_irq(sbd, &s->parent_irq[i]);

}

for (i = 0; i < s->num_cpu; i++) {

sysbus_init_irq(sbd, &s->parent_fiq[i]);

}

for (i = 0; i < s->num_cpu; i++) {

sysbus_init_irq(sbd, &s->parent_virq[i]);

}

for (i = 0; i < s->num_cpu; i++) {

sysbus_init_irq(sbd, &s->parent_vfiq[i]);

}

.....

}The log is:

alexdebug:arm_gic_realize

alexdebug:arm_gic_common_realize begin, SysBusDevice is at 0x7fffbe7a9ce0

alexdebug:qemu_allocate_irq irq at 0x7fffbe6627b0, n is 0

alexdebug:qemu_allocate_irq irq at 0x7fffbe662900, n is 1

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b47a0, n is 2

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4840, n is 3

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4910, n is 4

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b49e0, n is 5

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4ab0, n is 6

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4b80, n is 7

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4c50, n is 8

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4d20, n is 9

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4df0, n is 10

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4ec0, n is 11

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b4f90, n is 12

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5060, n is 13

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5130, n is 14

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5200, n is 15

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b52d0, n is 16

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b53a0, n is 17

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5ca0, n is 18

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5d70, n is 19

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5e40, n is 20

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5f10, n is 21

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b5fe0, n is 22

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b60b0, n is 23

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6180, n is 24

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6250, n is 25

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6320, n is 26

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b63f0, n is 27

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b64c0, n is 28

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6590, n is 29

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6660, n is 30

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6730, n is 31

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6800, n is 32

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b68d0, n is 33

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b69a0, n is 34

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6a70, n is 35

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b6b40, n is 36

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b7a80, n is 37

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b7b50, n is 38

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b7c20, n is 39

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b7cf0, n is 40

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b7dc0, n is 41

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b7e90, n is 42

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b7f60, n is 43

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b8030, n is 44

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b8100, n is 45

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b81d0, n is 46

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b82a0, n is 47

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b8370, n is 48

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b8440, n is 49

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b8510, n is 50

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b85e0, n is 51

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b86b0, n is 52

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b8780, n is 53

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b96e0, n is 54

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b97b0, n is 55

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9880, n is 56

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9950, n is 57

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9a20, n is 58

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9af0, n is 59

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9bc0, n is 60

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9c90, n is 61

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9d60, n is 62

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9e30, n is 63

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9f00, n is 64

alexdebug:qemu_allocate_irq irq at 0x7fffbe7b9fd0, n is 65

alexdebug:qemu_allocate_irq irq at 0x7fffbe7ba0a0, n is 66

alexdebug:qemu_allocate_irq irq at 0x7fffbe7ba170, n is 67

alexdebug:qemu_allocate_irq irq at 0x7fffbe7ba240, n is 68

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb370, n is 69

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb440, n is 70

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb510, n is 71

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb5e0, n is 72

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb6b0, n is 73

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb780, n is 74

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb850, n is 75

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb920, n is 76

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bb9f0, n is 77

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bbac0, n is 78

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bbb90, n is 79

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bbc60, n is 80

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bbd30, n is 81

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bbe00, n is 82

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bbed0, n is 83

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bbfa0, n is 84

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bc070, n is 85

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bc970, n is 86

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bca40, n is 87

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bcb10, n is 88

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bcbe0, n is 89

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bccb0, n is 90

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bcd80, n is 91

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bce50, n is 92

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bcf20, n is 93

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bcff0, n is 94

alexdebug:qemu_allocate_irq irq at 0x7fffbe7bd0c0, n is 953. timer GPIO_OUT irq connect to GIC GPIO_IN irq

static void a9mp_priv_realize(DeviceState *dev, Error **errp)

{

.....

A9MPPrivState *s = A9MPCORE_PRIV(dev);

.....

gicdev = DEVICE(&s->gic);

.....

gtimerbusdev = SYS_BUS_DEVICE(&s->gtimer);

.....

mptimerbusdev = SYS_BUS_DEVICE(&s->mptimer);

.....

wdtbusdev = SYS_BUS_DEVICE(&s->wdt);

.....

for (i = 0; i < s->num_cpu; i++) {

int ppibase = (s->num_irq - 32) + i * 32;

sysbus_connect_irq(gtimerbusdev, i,

qdev_get_gpio_in(gicdev, ppibase + 27));

sysbus_connect_irq(mptimerbusdev, i,

qdev_get_gpio_in(gicdev, ppibase + 29));

sysbus_connect_irq(wdtbusdev, i,

qdev_get_gpio_in(gicdev, ppibase + 30));

}

}Log is:

alexdebug:sysbus_connect_irq -------start --device arm.cortex-a9-global-timer --cpu is 0 , irq at 0x7fffbe7bcd80, irq->n is 91 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:sysbus_connect_irq -------start --device arm_mptimer --cpu is 0 , irq at 0x7fffbe7bcf20, irq->n is 93 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:sysbus_connect_irq -------start --device arm_mptimer --cpu is 0 , irq at 0x7fffbe7bcff0, irq->n is 94 ---

alexdebug:sysbus_connect_irq -------end -------We can see irq 91 is GIC 91 GPIO_IRQ(0x7fffbe7bcd80). 93,94 irqs are GIC 93,94 irq too.

4. PIC[] from GIC

static void vexpress_common_init(MachineState *machine)

{

qemu_irq pic[64];

.....

daughterboard->init(vms, machine->ram_size, machine->cpu_type, pic);

}

static void a9_daughterboard_init(const VexpressMachineState *vms,

ram_addr_t ram_size,

const char *cpu_type,

qemu_irq *pic)

{

init_cpus(machine, cpu_type, TYPE_A9MPCORE_PRIV, 0x1e000000, pic,

vms->secure, vms->virt);

}

static void init_cpus(MachineState *ms, const char *cpu_type,

const char *privdev, hwaddr periphbase,

qemu_irq *pic, bool secure, bool virt)

{

DeviceState *dev;

SysBusDevice *busdev;

A9MPPrivState *a9_s;

int n;

.....

{

a9_s = A9MPCORE_PRIV(dev);

printf("alexdebug:%s, GIC parent_irq at %p\n",__func__,a9_s->gic.parent_irq[0]);

}

for (n = 0; n < 64; n++) {

DeviceState* gicdev=DEVICE(&a9_s->gic);

pic[n] = qdev_get_gpio_in(gicdev, n);

//pic[n] = qdev_get_gpio_in(dev, n);

printf("alexxie:%s, pic[%d] at %p\n",__func__,n,pic[n]);

}

.....

}Log is:

alexdebug:init_cpus, GIC parent_irq at (nil)

alexxie:init_cpus, pic[0] at 0x7fffbe6627b0

alexxie:init_cpus, pic[1] at 0x7fffbe662900

alexxie:init_cpus, pic[2] at 0x7fffbe7b47a0

alexxie:init_cpus, pic[3] at 0x7fffbe7b4840

alexxie:init_cpus, pic[4] at 0x7fffbe7b4910

alexxie:init_cpus, pic[5] at 0x7fffbe7b49e0

alexxie:init_cpus, pic[6] at 0x7fffbe7b4ab0

alexxie:init_cpus, pic[7] at 0x7fffbe7b4b80

alexxie:init_cpus, pic[8] at 0x7fffbe7b4c50

alexxie:init_cpus, pic[9] at 0x7fffbe7b4d20

alexxie:init_cpus, pic[10] at 0x7fffbe7b4df0

alexxie:init_cpus, pic[11] at 0x7fffbe7b4ec0

alexxie:init_cpus, pic[12] at 0x7fffbe7b4f90

alexxie:init_cpus, pic[13] at 0x7fffbe7b5060

alexxie:init_cpus, pic[14] at 0x7fffbe7b5130

alexxie:init_cpus, pic[15] at 0x7fffbe7b5200

alexxie:init_cpus, pic[16] at 0x7fffbe7b52d0

alexxie:init_cpus, pic[17] at 0x7fffbe7b53a0

alexxie:init_cpus, pic[18] at 0x7fffbe7b5ca0

alexxie:init_cpus, pic[19] at 0x7fffbe7b5d70

alexxie:init_cpus, pic[20] at 0x7fffbe7b5e40

alexxie:init_cpus, pic[21] at 0x7fffbe7b5f10

alexxie:init_cpus, pic[22] at 0x7fffbe7b5fe0

alexxie:init_cpus, pic[23] at 0x7fffbe7b60b0

alexxie:init_cpus, pic[24] at 0x7fffbe7b6180

alexxie:init_cpus, pic[25] at 0x7fffbe7b6250

alexxie:init_cpus, pic[26] at 0x7fffbe7b6320

alexxie:init_cpus, pic[27] at 0x7fffbe7b63f0

alexxie:init_cpus, pic[28] at 0x7fffbe7b64c0

alexxie:init_cpus, pic[29] at 0x7fffbe7b6590

alexxie:init_cpus, pic[30] at 0x7fffbe7b6660

alexxie:init_cpus, pic[31] at 0x7fffbe7b6730

alexxie:init_cpus, pic[32] at 0x7fffbe7b6800

alexxie:init_cpus, pic[33] at 0x7fffbe7b68d0

alexxie:init_cpus, pic[34] at 0x7fffbe7b69a0

alexxie:init_cpus, pic[35] at 0x7fffbe7b6a70

alexxie:init_cpus, pic[36] at 0x7fffbe7b6b40

alexxie:init_cpus, pic[37] at 0x7fffbe7b7a80

alexxie:init_cpus, pic[38] at 0x7fffbe7b7b50

alexxie:init_cpus, pic[39] at 0x7fffbe7b7c20

alexxie:init_cpus, pic[40] at 0x7fffbe7b7cf0

alexxie:init_cpus, pic[41] at 0x7fffbe7b7dc0

alexxie:init_cpus, pic[42] at 0x7fffbe7b7e90

alexxie:init_cpus, pic[43] at 0x7fffbe7b7f60

alexxie:init_cpus, pic[44] at 0x7fffbe7b8030

alexxie:init_cpus, pic[45] at 0x7fffbe7b8100

alexxie:init_cpus, pic[46] at 0x7fffbe7b81d0

alexxie:init_cpus, pic[47] at 0x7fffbe7b82a0

alexxie:init_cpus, pic[48] at 0x7fffbe7b8370

alexxie:init_cpus, pic[49] at 0x7fffbe7b8440

alexxie:init_cpus, pic[50] at 0x7fffbe7b8510

alexxie:init_cpus, pic[51] at 0x7fffbe7b85e0

alexxie:init_cpus, pic[52] at 0x7fffbe7b86b0

alexxie:init_cpus, pic[53] at 0x7fffbe7b8780

alexxie:init_cpus, pic[54] at 0x7fffbe7b96e0

alexxie:init_cpus, pic[55] at 0x7fffbe7b97b0

alexxie:init_cpus, pic[56] at 0x7fffbe7b9880

alexxie:init_cpus, pic[57] at 0x7fffbe7b9950

alexxie:init_cpus, pic[58] at 0x7fffbe7b9a20

alexxie:init_cpus, pic[59] at 0x7fffbe7b9af0

alexxie:init_cpus, pic[60] at 0x7fffbe7b9bc0

alexxie:init_cpus, pic[61] at 0x7fffbe7b9c90

alexxie:init_cpus, pic[62] at 0x7fffbe7b9d60

alexxie:init_cpus, pic[63] at 0x7fffbe7b9e305. GIC GPIO_OUT irq connect to ARM CORE GPIO_IN irq

static void init_cpus(MachineState *ms, const char *cpu_type,

const char *privdev, hwaddr periphbase,

qemu_irq *pic, bool secure, bool virt)

{

DeviceState *dev;

SysBusDevice *busdev;

int n;

unsigned int smp_cpus = ms->smp.cpus;

.....

busdev = SYS_BUS_DEVICE(dev); /*here busdev is a9mpcore_priv*/

.....

for (n = 0; n < smp_cpus; n++) {

DeviceState *cpudev = DEVICE(qemu_get_cpu(n));

sysbus_connect_irq(busdev, n, qdev_get_gpio_in(cpudev, ARM_CPU_IRQ));

sysbus_connect_irq(busdev, n + smp_cpus,

qdev_get_gpio_in(cpudev, ARM_CPU_FIQ));

sysbus_connect_irq(busdev, n + 2 * smp_cpus,

qdev_get_gpio_in(cpudev, ARM_CPU_VIRQ));

sysbus_connect_irq(busdev, n + 3 * smp_cpus,

qdev_get_gpio_in(cpudev, ARM_CPU_VFIQ));

}

.....

}Log is:

alexdebug:sysbus_connect_irq -------start --device a9mpcore_priv --cpu is 0 , irq at 0x7fffbe6b4480, irq->n is 0 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:sysbus_connect_irq -------start --device a9mpcore_priv --cpu is 1 , irq at 0x7fffbe6644c0, irq->n is 1 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:sysbus_connect_irq -------start --device a9mpcore_priv --cpu is 2 , irq at 0x7fffbe6702c0, irq->n is 2 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:sysbus_connect_irq -------start --device a9mpcore_priv --cpu is 3 , irq at 0x7fffbe66fbe0, irq->n is 3 ---

alexdebug:sysbus_connect_irq -------end -------

ARM CORE GPIO_IN irq 0 is 0x7fffbe6b4480, GIC connect to ARM CORE.

6. Device GPIO_OUT irq connect to GIC GPIO_IN irq

static void vexpress_common_init(MachineState *machine)

{

.....

pl011_create(map[VE_UART0], pic[5], serial_hd(0));

pl011_create(map[VE_UART1], pic[6], serial_hd(1));

pl011_create(map[VE_UART2], pic[7], serial_hd(2));

pl011_create(map[VE_UART3], pic[8], serial_hd(3));

.....

}The log is:

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexdebug:sysbus_connect_irq -------start --device pl011 --cpu is 0 , irq at 0x7fffbe7b49e0, irq->n is 5 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:pl011_create, uart irq is at 0x7fffbe7b49e0,(nil),(nil),(nil),(nil),(nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexdebug:sysbus_connect_irq -------start --device pl011 --cpu is 0 , irq at 0x7fffbe7b4ab0, irq->n is 6 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:pl011_create, uart irq is at 0x7fffbe7b4ab0,(nil),(nil),(nil),(nil),(nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexdebug:sysbus_connect_irq -------start --device pl011 --cpu is 0 , irq at 0x7fffbe7b4b80, irq->n is 7 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:pl011_create, uart irq is at 0x7fffbe7b4b80,(nil),(nil),(nil),(nil),(nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexxie:pl011_init, uart irq at (nil)

alexdebug:sysbus_connect_irq -------start --device pl011 --cpu is 0 , irq at 0x7fffbe7b4c50, irq->n is 8 ---

alexdebug:sysbus_connect_irq -------end -------

alexdebug:pl011_create, uart irq is at 0x7fffbe7b4c50,(nil),(nil),(nil),(nil),(nil)Here UART GPIO_OUT irq connect to GIC GPIO_IN 5,6,7,8 irq.

边栏推荐

- How wechat applet assigns values to sub components

- 关于图片懒加载的实现(总结梳理)

- CMAKE notes

- Tensorflow 2.x(keras)源码详解之第十四章:keras中的回调及自定义回调

- 大厂晋升学习方法三:链式学习法

- Amazon and independent station are not simply two choices

- Research Report on demand and investment opportunities in key areas of global and Chinese strontium tungstate industry 2022-2027

- CLion安装下载

- From "platform transformation" to "DTC brand going to sea", what is the trend of 2021?

- Kubernetes -- setting up an environment using minicube

猜你喜欢

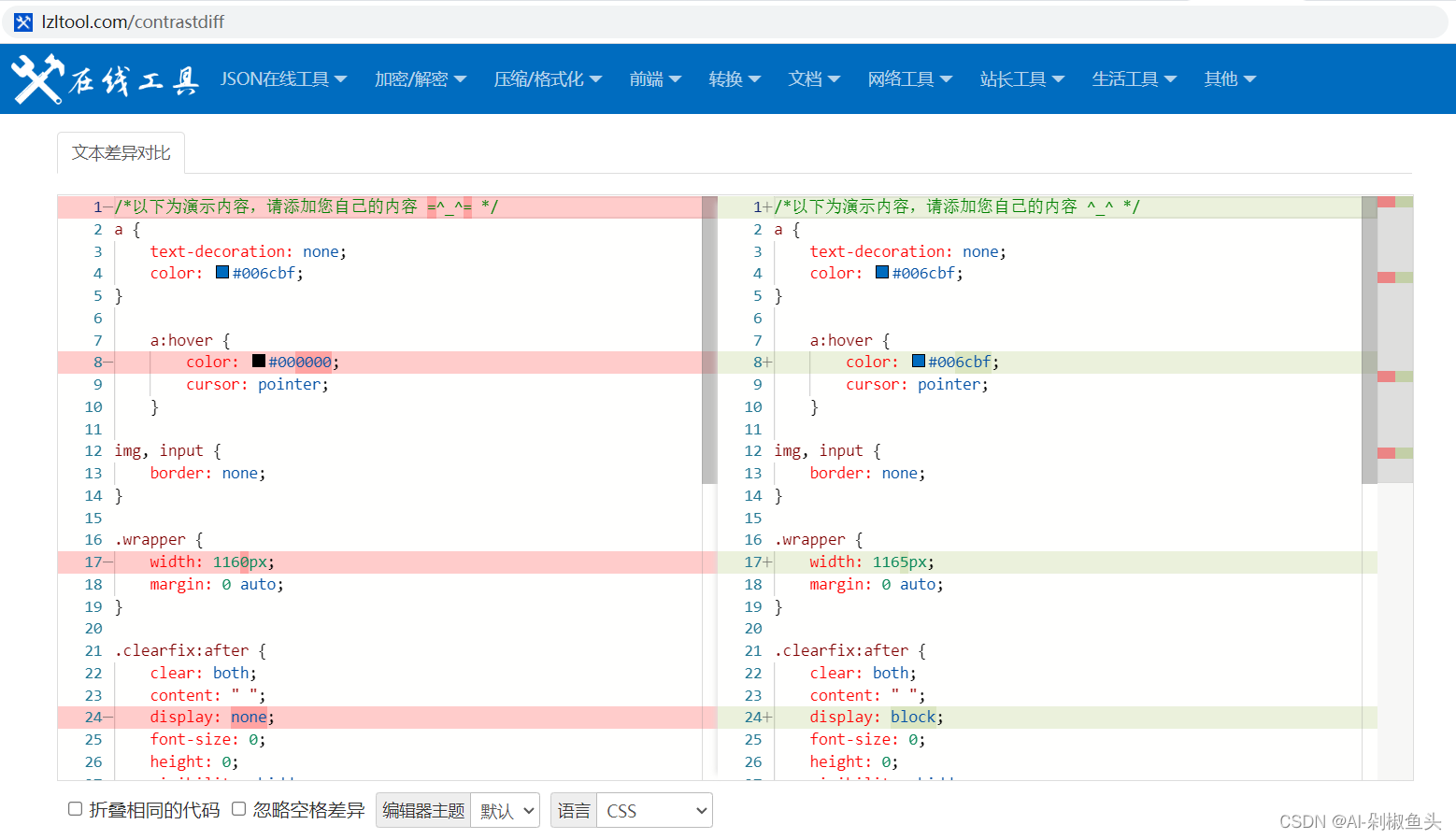

在线文本代码对比工具

Hide symbol of dynamic library

Go语言使用zap日志库

基于WebUploader实现大文件分片上传

Implementation of Nacos server source code

P1318 ponding area

Talk about MySQL's locking rule "hard hitting MySQL series 15"

vscode 远程连接错误:Server status check failed - waiting and retrying

机器学习笔记 六:逻辑回归中的多分类问题之数字识别

Graduation season | a new start, no goodbye

随机推荐

How wechat applet assigns values to sub components

open source hypervisor

记本地项目启动报错:无效的源发行版: 8

Innosetup method for judging that the program has run

nacos server 源码运行实现

Network, IO flow, reflection, multithreading, exception

C#中Cookie设置与读取

机器学习笔记 八:Octave实现神经网络的手写数字识别

想投放Facebook广告却不知从何入手?此文带你深入了解

Global and Chinese digital imager market development outlook and investment competitiveness analysis report 2022-2027

关于背包问题的总结

新手开店货源怎么找,怎么找到优质货源?

独立站优化清单丨如何有效提升站内转化率?

From "platform transformation" to "DTC brand going to sea", what is the trend of 2021?

Parameter serialization

代码走查的优化方向(接口请求便捷、动态class判断条件过长、去除无用console、抽离公共方法)

Analysis of 43 cases of MATLAB neural network: Chapter 29 research on the application of limit learning machine in regression fitting and classification -- Comparative Experiment

Data storage (Advanced)

Research Report on demand and investment opportunities in key areas of global and Chinese strontium tungstate industry 2022-2027

2022 Shanxi secondary vocational group "Cyberspace Security" event module b- web page penetration