当前位置:网站首页>[basic knowledge] ~ hard core / soft core / solid core, pwm/spwm, Fibonacci sequence, large end mode storage, Fourier transform, Nyquist sampling law, chip selection, Kirchhoff law, fir/iir filter

[basic knowledge] ~ hard core / soft core / solid core, pwm/spwm, Fibonacci sequence, large end mode storage, Fourier transform, Nyquist sampling law, chip selection, Kirchhoff law, fir/iir filter

2022-06-09 11:24:00 【AI is very good】

1. hardcore / Soft nucleus / Solid core

hardcore (Hard IP Core) : The hard core is EDA Design domain refers to the verified design layout ; Specific in FPGA Design refers to fixed layout and process 、 Front end and back end validated design , Designers can't modify it . There are two reasons why it can't be modified : First of all, the system design has strict requirements on the timing of each module , It is not allowed to disrupt the existing physical layout ; The second is the requirement of protecting intellectual property rights , Designers are not allowed to make any changes to it .IP The feature of hard core can not be modified makes it difficult to reuse , So it can only be used for some specific applications , The scope of application is narrow .

Soft nucleus (Soft IP Core) : The soft core is EDA Design domain refers to the register transfer level before synthesis (RTL) Model ; Specific in FPGA Design refers to the hardware language description of the circuit , Including logical description 、 Net list and help document, etc . Soft core only through functional simulation , You need to go through synthesis and layout to use . Its advantage is high flexibility 、 Strong portability , Allow users to self configure ; The disadvantage is the low predictability of the module , There is a possibility of error in subsequent design , There are certain design risks . The soft core is IP The most widely used form of nuclear .

Solid core (Firm IP Core) : The solid core is EDA The design domain refers to a net list with planning information ; Specific in FPGA Design can be seen as a soft core with layout planning , Usually, the RTL The mixed form of code and corresponding specific process net list is provided . take RTL This paper describes the comprehensive optimization design combined with specific standard cell library , Form gate level netlist , Then you can use the layout and routing tool . Compared to the soft core , The design flexibility of the solid core is slightly poor , But there is a big improvement in reliability . at present , So is the solid core IP One of the mainstream forms of nuclear .

2. PWM/SPWM

PWM, English name Pulse Width Modulation, Short for pulse width modulation , It is by modulating the width of a series of pulses , Equivalent to the required waveform ( Including shape and amplitude ), Digitally code the analog signal level , That is to say, adjust the signal by adjusting the change of duty cycle 、 Changes in energy, etc , Duty cycle means in a cycle , The time when the signal is at high level accounts for the percentage of the whole signal period , For example, the duty cycle of square wave is 50%.

SPWM, English name Sinusoidal PWM, Pulse width changes according to sine law and is equivalent to sine wave PWM wave form .

3. Big end mode storage

3.1 summary

Big end model (Big-endian), The high byte of data , Stored in a low address in memory , And the lower bytes of data , Stored in a high address in memory , This kind of storage mode is a bit similar to processing data in string order : The address increases from small to large , And the data goes from high to low ;

The so-called small end mode (Little-endian), The high byte of data is stored in the high address of memory , The low byte of the data is stored in the low address of the , This storage mode combines the height of the address with the data bits Effective combination of power , The weight of high address part is high , The weight of low address part is low , Consistent with our logical approach ;

3.2 There are different sizes ?

Because in the computer system , We are in bytes , Each address corresponds to a byte , A byte is 8bit. But in C In language, except 8bit Of char outside , also 16bit Of short type ,32bit Of long type ( It depends on the compiler ), in addition , For digits greater than 8 Bit processor , for example 16 Bits or 32 Bit processor , Because the register width is larger than one byte , So there must be a problem of how to arrange multiple bytes . So it leads to big end storage mode and small end storage mode . That we use a lot X86 The structure is small end mode , and KEIL C51 It's the big end mode . A great deal of ARM,DSP It's all small end mode . There are some ARM The processor can also choose the big end mode or the small end mode by the hardware .

4. Fibonacci sequence

The Fibonacci sequence refers to a sequence that looks like this :0、1、1、2、3、5、8、13、21、34、……

This sequence starts at number one 3 A start , Each of these terms is equal to the sum of the first two terms .

5. The Fourier transform

Fourier transformation , It means that a function satisfying certain conditions can be expressed as a trigonometric function ( Sine and / Or cosine function ) Or a linear combination of their integrals . In different areas of research , Fourier transform has many different variants , Such as Continuous Fourier transform and discrete Fourier transform .

6. Nyquist's sampling law

Nyquist sampling theorem means that if the bandwidth is limited , To recover the original signal without distortion from the sampled signal , The sampling frequency shall be greater than 2 Times the maximum frequency of the signal .

The sampling frequency is less than 2 Times the highest frequency of the spectrum , The spectrum of the signal is aliased .

The sampling frequency is greater than 2 Times the highest frequency of the spectrum , There is no aliasing in the spectrum of the signal .

7. Kirchhoff's law

Kirchhoff's law includes current law and voltage law :

Current law : In a lumped circuit , At any instant , The sum of the currents flowing to a node is equal to the sum of the currents flowing from the node .

The law of voltage : In a lumped circuit , At any moment , Go round any circuit in the circuit , In this circuit, the sum of electromotive force is equal to the sum of voltage drops on each resistor .

8. Chip selection

First Basic functions, of course . The function must meet your needs .

secondly Performance needs to be considered , For example, signal-to-noise ratio 、 bandwidth 、 transmission speed 、 storage capacity 、 Working voltage 、 Quiescent current loss, etc , It depends on the function of your chip . Of course, it is necessary to consider both performance and cost .

Besides , We also need to consider the packaging form of the chip 、 Operating temperature range 、ESD Protection level 、 Lead free, etc .

Next Ask from the perspective of production process “ Is this chip solderable ?” For example, it is impossible to weld in a processing plant with a low technological level / test BGA Is a package of components .

Next Ask from the perspective of supply chain management “ Is this chip easy to buy ? Is there a stable and reliable source channel ?” If you choose a chip after a lot of hard work 、 But I found that I couldn't buy it all over the world , That would be useless .

9. FIR/IIR filter

9.1 summary

FIR( Finite impulse response ) filter : Non recursive ( There is no feedback channel ), With linear phase .

IIR( Infinite impulse response ) filter : Recursive structure ( Including feedback channel ), Nonlinear phase .

9.2 Difference between the two

Same order FIR and IIR filter ,IIR The filter has good filtering effect , But it will produce phase distortion .FIR The filter has stable performance , But the order ratio required for the same amplitude index IIR higher 5~10 times , Cost is very high . stay DSP In design ,FIR Than IIR Need more parameters , That is to say, more calculations are needed , More resources are consumed and more computing time is required , Yes DSP The real-time performance of .

9.3 FIR filter

Yes N Samples are weighted and averaged ( Convolution ) Handle .

The treatment process is expressed by the following formula :

chart :( The triangle symbol in the figure means delay )

9.4 IIR filter

Contains both recursive and non recursive parts . One IIR The filter can be seen as consisting of two FIR Filter composition . One of the filters is located in the feedback loop , Design IIR The key of the filter is to ensure the stability of the recursive part .

The treatment process is expressed by the following formula :( have N Feedforward coefficients and M-1 A feedback coefficient )

chart :

FIR filter , Maybe I'm based on FPGA When the digital signal processing system needs filtering , The first thing that comes to mind . Because it is very convenient . About the use of filters ,xilinx The official provided FIR Compiler IP Core to call . The traditional design method is , Use matlab Of FDATool Tools to design filters , And export the tap file , It's the one in the picture above W(0)—W(N-1) These weights , And in vivado Call in FIR IP, Configure import tap file . If using system generator It will be more convenient to design , stay Sysgen We can put FDATool and FIR Compiler Make an association , You do not need to manually export or import the taps FIR Design of filter .

边栏推荐

- Matlab相关函数知识点(三)-floor函数+点除运算符+矩阵索引规则

- 中银证券靠谱吗?开证券账户安全吗?

- no provider available for the service错误解决方案

- Use the five number generalization method to determine the outliers in the data set

- Shutter popup shutter shutter_ easyloading

- 文档书写规范

- DM 平台管理 - netcore

- What are the preparations for building your own website

- TiDB Cloud 上线 Google Cloud Marketplace,以全新一栈式实时 HTAP 数据库赋能全球开发者

- Post processing of wechat applet login failure

猜你喜欢

企评家用杜邦分析法剖析:华东建筑集团股份有限公司企业财务状况

Multi engine database management tool DataGrid 2022.1.5 Chinese version

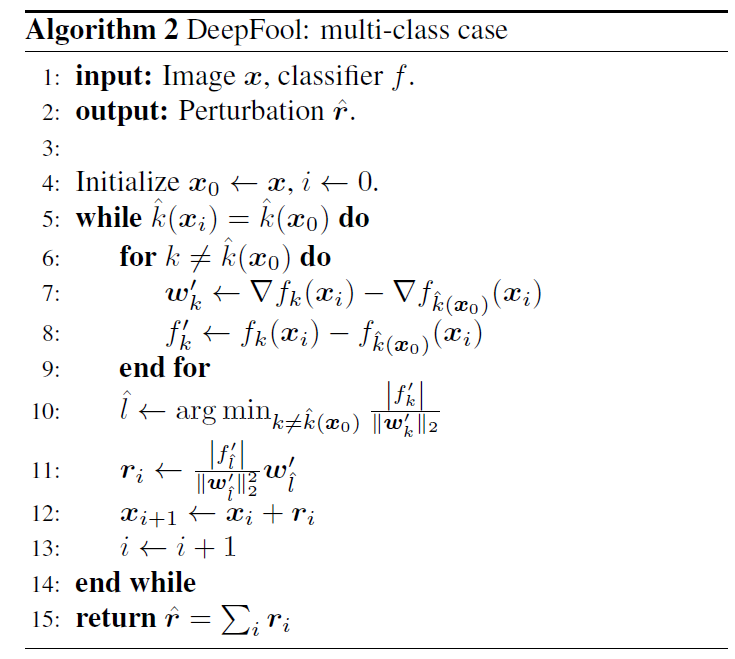

论文阅读 (54):DeepFool: A Simple and Accurate Method to Fool Deep Neural Networks

福建土楼沟文化旅游开发有限公司6%股权转让,来自塔米狗分享

使用 KubeKey 搭建 Kubernetes/KubeSphere 环境的“心路(累)历程“

Web development exchange, web development example tutorial

叶酸配体的金属有机骨架材料MOFs负载5-氟尿嘧啶,西达本胺,紫杉醇,阿霉素,柔红霉素等药物

What are the preparations for building your own website

【mysql进阶】利用执行计划explain优化sql(二)

多引擎数据库管理工具 DataGrip 2022.1.5中文版

随机推荐

太神奇的 SQL 查询经历,group by 慢查询优化!

Introduction and simple use of protobuf

merge sort

MySQL learning notes - Part 3 - indexes, stored procedures and functions, views, triggers

无法在debug时进入ArrayList底层解决方案

RDMA Verbs API

EasyRecovery15免费版本数据恢复软件

Leetcode 2048. 下一个更大的数值平衡数(有点意思,已解决)

Based on the actual development of Huawei's cloud King returnable martyr tracing system [Huawei cloud to jianzhiyuan]

【mysql进阶】利用执行计划explain优化sql(二)

第四讲:数据仓库搭建(二)

Detailed steps for using Excel conditional format

This article takes you to understand gaussdb (DWS) [Gauss is not a mathematician this time]

基于物联网设计的铂电阻气体测温仪(华为云IOT)【玩转华为云】

Shutter popup shutter shutter_ easyloading

Enterprise distributed batch processing scheme based on task scheduling

Perfdog releases new indicators, tailored to the game

Monomer mode

Introduction to automatic partition management of gaussdb (DWS)

小知识——let const var的区别