当前位置:网站首页>[mit 6.s081] LEC 4: page tables notes

[mit 6.s081] LEC 4: page tables notes

2022-07-27 18:27:00 【PeakCrosser】

Lec 4: Page tables

- Ref: https://github.com/huihongxiao/MIT6.S081/tree/master/lec04-page-tables-frans

- Preparation: xv6 book Chapter 3

Outline

- Address spaces address space

- paging HW Support page table ( Virtual memory ) The related hardware

- xv6 vm code+layout

Address Spaces

Strong isolation

Page Tables

summary

Used to create different address spaces for processes

from CPU and Memory management unit (Memory Management Unit, MMU) Realization

The page table is stored in memory , There are special registers to record its physical address . RISC-V In Chinese, it means SATP register .

MMU Used to complete the conversion from virtual address to physical address

Address partition

Page (page) Divide memory into units . RISC-V Middle page (page) by 4KB.

The virtual address is divided into index and offset Two parts . RISC-V in , Virtual address 64 position , The number of effective address digits is 39 bits : 27 position index, 12 position offset

Physical memory address 56 position : 44 Bit is the physical page number (Physical Page Number, PPN), 12 Bit is the intra page offset (offset)

RISC-V Page table implementation - Three level page table structure

- Virtual address : 64bit: 27bit Indexes (L2, L1, L0), 12bit Page offset

- Physical address : 64bit: 10bit Retain , 44bit Indexes ( Physical page number PPN), 10bit Sign a

27bit Of index Divided into 3 individual 9bit The index of (L2, L1, L0).

Divided into top-level page directory (Top Level Page Directory), Intermediate page directory (Middle Level Page Directory) and The lowest level page directory ( A page table ).

An entry in the page directory is called a page table entry (Page Table Entry, PTE), 8Bytes. A page directory 4KB, Yes 512 individual PTE. Every PTE There is 44bit PPN and 10 bit Flags. The physical address stored in the page directory (SATP The register is also a physical address ).

The top-level page directory consists of L2 Do the index , L1 Make an offset ; The intermediate page directory consists of L1 Do the index , L0 Make an offset .

Sign a :

- Valid: Express PTE Whether it works . Invalid indicates that it cannot be used to obtain the virtual address .

- Readable/Writable: Is it readable? / Write this page

- Executable: Whether the instructions in this page can be executed

- User: Whether the page can be accessed by processes in user space

Page table cache (TLB)

Page table cache (Translation Lookaside Buffer, TLB)

When switching page tables , TLB Will be emptied .

MMU and TLB It exists in every CPU Nuclear . According to the processor Cache Whether it is indexed by physical address , To decide on TLB After or before the address translation .

3 The level page table is implemented by hardware . MMU It's hardware . XV6 Medium walk() Function also implements the page table lookup function , Return a corresponding PTE. walk() The reasons why functions exist include : Used to set the initial page table for the operating system ; Used to copy data from kernel space to user space .

Kernel page table distribution

- notes : yes Page table of kernel

On the left is the virtual address space distribution of the kernel . The upper right is the physical memory space (DRAM), At the bottom right is I/O Device address space .

- boot ROM: Boot read-only memory . When the motherboard is powered on, it is initially executed , Boot and load the operating system .

- PLIC: Interrupt controller (Platform-Level Interrupt Controller)

- CLINT: Core Local Interruptor, Interrupt part . ( In the latest xv6 In the instruction , This part does not appear in the virtual address space )

- UART0: Universal Asynchronous Receiver/Transmitter, Copy and Console Interact with the monitor .

- VIRTIO disk: Interact with disk .

new edition xv6 Kernel address space distribution ( The difference is CLINT Part removed in virtual space ):

Kernel stack (Kstack) The corresponding physical address is mapped 2 Time , There was another time when Kernel data in . But usually use the top belt Guard page Of . Different processes have different kernel stacks .

Guard page Generally, it is not mapped to physical memory , Its PTE Of Valid Bit is not set , Used to judge whether the kernel stack is out of bounds .

In virtual memory "Free memory" Part will store the page table of the user process , text and data.

Virtual address space distribution of user process :

XV6 Page table code

kernel/main.c-main()

-> kvminit() Create page table

-> kvminithart() Set up SATP register , After that, all memory addresses are virtual addresses , Address translation starts

边栏推荐

- [MIT 6.S081] Lab 11: networking

- 《华为是谁》纪录短片集登陆BBC:曝光大量任正非不为人知经历

- Deep learning: installation package records

- 又一个时代的终结!

- 3. opencv几何变换

- 【学习笔记】热点账户问题的解决方案

- Super practical! After reading the kubernetes study notes hidden by Alibaba P9, call NB directly

- 力压谷歌、英伟达!阿里含光800芯片再获权威测试世界第一

- Local development using LWC in salesforce

- Marvell announced the roadmap of its arm server chip, and the performance of the next generation will be twice that of thunderx2

猜你喜欢

【学习笔记】MySQL数据库高级版 - 索引优化、慢查询、锁机制等

![[MIT 6.S081] Lab 5: xv6 lazy page allocation](/img/f6/8b619412bc6ba425d0f04629917e80.png)

[MIT 6.S081] Lab 5: xv6 lazy page allocation

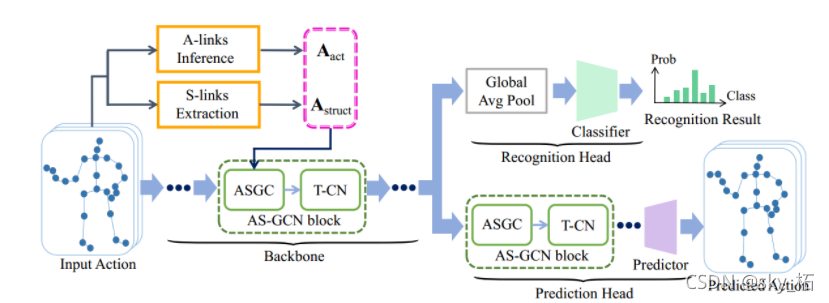

Deep learning - paper reading: action structural graph convolution network as-gcn

![[MIT 6.S081] Lec 9: Interrupts 笔记](/img/b6/a8d39aa7ede4eb1c5a74e6d15b3b1c.png)

[MIT 6.S081] Lec 9: Interrupts 笔记

Binary tree concept

zabbix6.0的安装部署

二叉树概念

![[MIT 6.S081] Lec 5: Calling conventions and stack frames RISC-V 笔记](/img/1f/6384f4831718477f0567540250f352.png)

[MIT 6.S081] Lec 5: Calling conventions and stack frames RISC-V 笔记

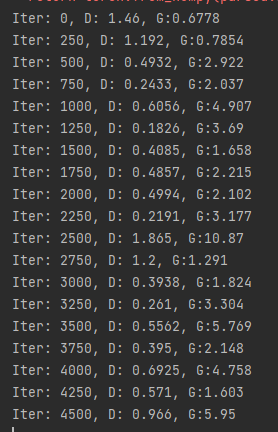

深度学习:GAN案例练习-minst手写数字

Deep learning: GCN diagram classification case

随机推荐

展锐鲜苗:赋能全场景应用,海量数据需要AI与IoT融合

被“赶出”比特大陆之后,詹克团首度发声:将通过法律途径尽快回归!

Deep learning - VIDEO behavior recognition: paper reading - two stream revolutionary networks for action recognition in videos

[MIT 6.S081] Lab 3: page tables

小米CC9 Pro拆解:后置五摄成本是骁龙855数倍!

查看端口PID及结束进程

[MIT 6.S081] Lab 9: file system

Deep learning: GCN (graph convolution neural network) theory learning summary

[MIT 6.S081] Lab 7: Multithreading

"Who is Huawei" documentary film series landing on BBC: exposing a large number of Ren Zhengfei's unknown experience

Technology sharing | quick intercom integrated dispatching system

Disassembly of Xiaomi cc9 Pro: the cost of rear five shots is several times that of Xiaolong 855!

[learning notes] the implementation principle of the ordered set Zset in redis - skip table

1542. 找出最长的超赞子字符串 哈希+状态压缩

Nowcoder (5 choices)

[MIT 6.S081] Lec 5: Calling conventions and stack frames RISC-V 笔记

Deep learning: gat

Together with Samsung, vivo will promote exynos980 dual-mode 5g mobile phone!

深度学习:行为识别综述

2. Change color space and color detection