当前位置:网站首页>FPGA - 7系列 FPGA内部结构之Clocking -04- 多区域时钟

FPGA - 7系列 FPGA内部结构之Clocking -04- 多区域时钟

2022-07-03 00:13:00 【Vuko-wxh】

前言

本文节选UG472进行整理翻译,用于介绍时钟资源的跨多个时钟区域的时域说明和注意要点。

文章目录

简介

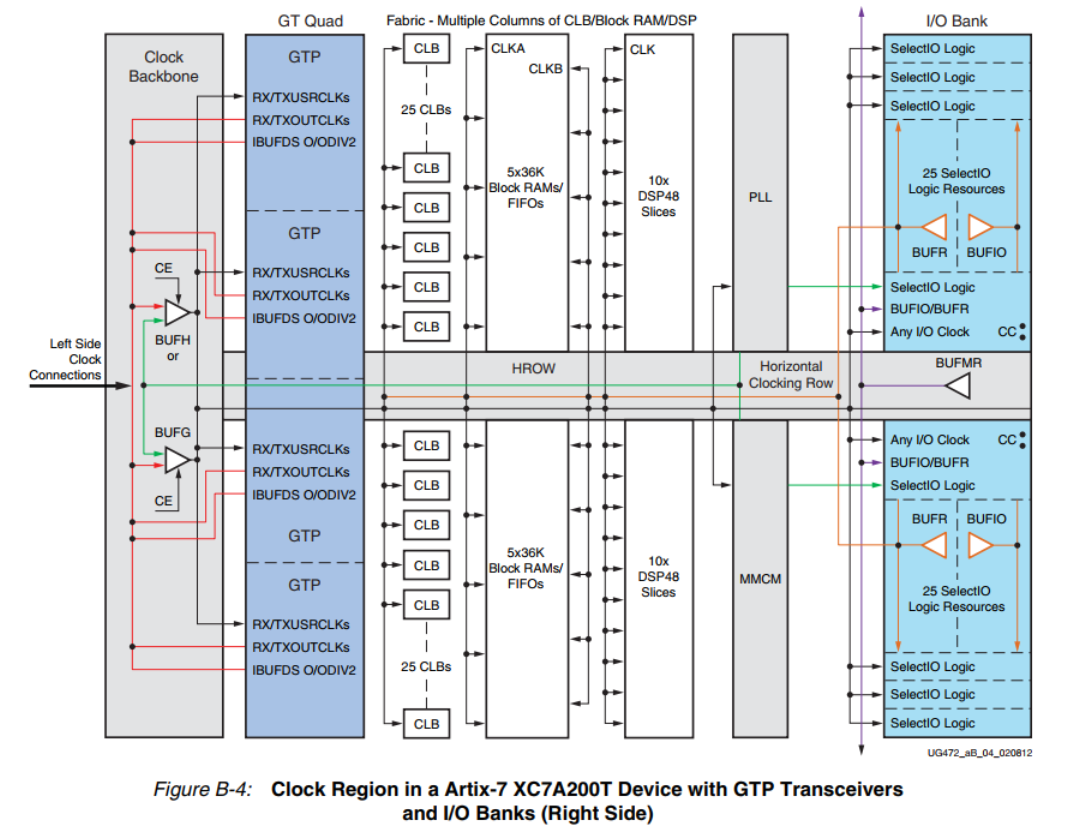

7 系列 FPGA 中跨多个时钟区域的时钟和 I/O 互连逻辑不同于前几代赛灵思 FPGA 中的实现方式。 虽然时钟区域中 I/O 和逻辑资源的增加减少了跨越多个时钟区域的时钟信号的需求,但这些相同的宽 I/O 接口仍然需要能够在多个时钟区域中驱动互连和 I/O 逻辑 时钟区域。 7 系列 FPGA BUFMR/BUFMRCE 原语使具有时钟功能的输入引脚能够驱动输入所在区域以及上方和下方区域中的 BUFIO 和 BUFR。

本附录详细介绍了使用 BUFIO 和 BUFR 时钟缓冲器来驱动跨多个时钟区域的时钟信号。

所有 7 系列 FPGA 都被划分为称为时钟区域的区域。 时钟区域从器件中心的全局时钟列跨越到器件的左边缘或右边缘,高 50 行 CLB。

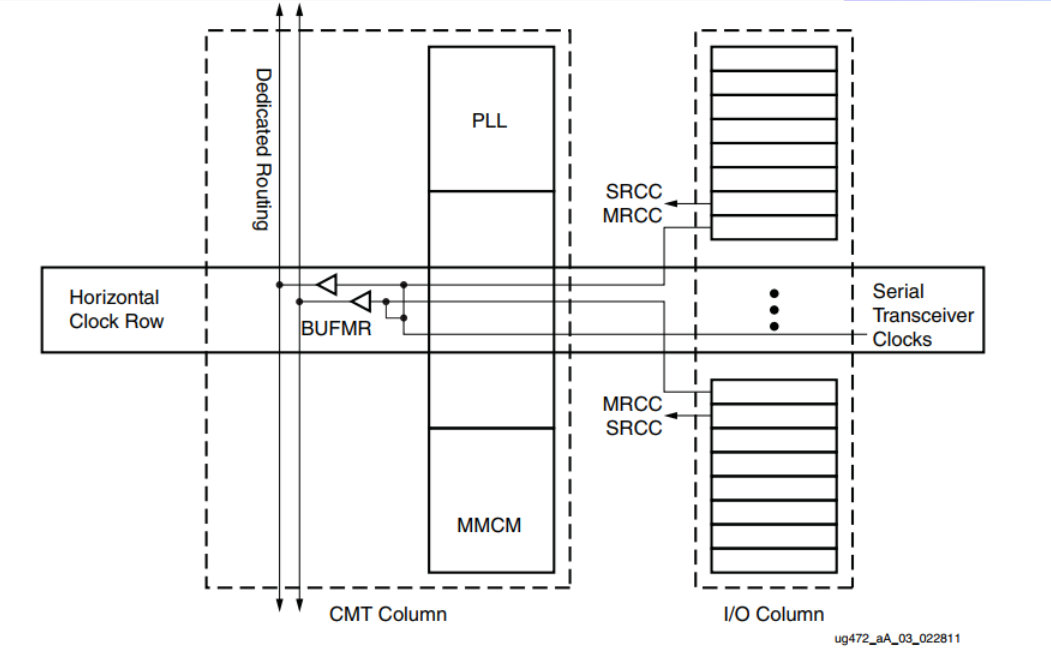

每个时钟区域都有自己的资源。 水平时钟行(图 A-2)位于时钟区域的中间,上面有 25 行 CLB,下面有 25 行 CLB。 驻留在每个时钟区域中的 I/O 列是 50 个 I/O 高,并且正好是一个 I/O bank。每个时钟区域内的 I/O bank 中有四个具有时钟能力的输入 (CCIO) 引脚,两个在水平时钟行上方,两个在下方。

跨多个区域的时钟

虽然时钟区域内逻辑和 I/O 资源的增加减少了设计跨越多个时钟区域的需求,但一些设计仍然需要更大的 I/O 接口来驱动来自多个输入源的相同时钟信号 时钟区域。 在不使用任何其他原语的情况下,通过 CCIO 引脚进入器件的时钟信号只能驱动同一区域内的 BUFR 和/或 BUFIO。 某些设计要求输入时钟信号以多个时钟为互连逻辑(例如 slice 触发器、块 RAM 和 DSP slice)和 I/O 逻辑(例如 ISERDES、OSERDES、ILOGIC、OLOGIC、IDELAY 和 ODELAY)提供时钟 地区。 为此,必须使用 BUFMR 原语。

BUFMR 原语

BUFMR 原语是一个多区域时钟缓冲器,它允许时钟信号访问时钟信号进入器件的区域上方和下方的区域中的 BUFR 和 BUFIO。 BUFMR 可以跨越多个时钟区域。

每个时钟区域有两个 BUFMR。 BUFMR 驱动位于 CMT 列中的专用低偏差时钟资源,确保在将时钟信号驱动到多个区域时插入尽可能少的偏差。

每个 BUFMR 都能够驱动同一区域以及正上方和下方区域中的 BUFR 和 BUFIO。 BUFMR 由同一时钟区域中的 CCIO 或千兆位收发器 (GT) 输出驱动。 这允许 CCIO 和 GT 输出时钟使用相同的电路拓扑跨越多个区域。 在每个时钟区域中存在的四个 CCIO 中,两个可以驱动 BUFMR。 这些引脚被标记为 MRCC 以表示它们的多区域能力。 不能驱动 BUFMR 的两个 CCIO 被标记为 SRCC 用于单区域 CCIO。 每个 MRCC 引脚都有一个主机或 P 侧和一个从机或 N 侧。 使用 MRCC 引脚驱动 BUFMR 时,仅使用主端或 P 端。 要识别主端或 P 端,请在引脚名称中查找 P(例如:IO_LxxP_Tx_MRCC_xx)。

Virtex-6 FPGA BUFR 的 GT 输入在 7 系列 FPGA 架构中不可用。 但是,BUFMR 可以从时钟区域内的任何一个 GT 时钟获取其输入。 这允许 GT 时钟使用相同的电路拓扑跨越多个区域,如上图所示。 此外,BUFMR 不能跨越使用堆叠硅互连技术的设备上的超级逻辑区域 (SLR) 之间的边界。

使用示例

当使用 BUFMR 驱动多个区域中的逻辑时,将由多个 BUFR 或 BUFIO 驱动的逻辑分组为(最多三个)子集,每个子集都有一个单独的 BUFR 或 BUFIO。 使用 Vivado 设计工具对设计进行布局规划和约束,以便将逻辑分配给各个 BUFR 和 BUFIO。

出于说明目的,以下时钟方案使用 MRCC 作为输入; 但是,可以使用 GT 时钟。 此外,其中一些示例显示了使用 BUFR 的内置分割功能时的拓扑。 BUFR 可以以整数步长除以 1 到 8。 除值由设计期间的 BUFR_DIVIDE 属性指定。此外,BUFR 有一个 BYPASS 设置,它可以关闭除法功能和禁用输出时钟使能 (CE) 和除法逻辑 (CLR) 的异步清零。

跨时钟区域的时钟对齐

尽管使用 BUFR_DIVIDE=BYPASS 或 BUFR_DIVIDE=1 属性时 BUFR 原语的行为相似,但使用 BUFR_DIVIDE=BYPASS 时通过 BUFR 的延迟小于使用 BUFR_DIVIDE=1 时的延迟。 但是,当使用 BUFR_DIVIDE=1 属性或 BUFR_DIVIDE=2、3…8 时,通过 BUFR 的延迟是相同的。 因此,当使用具有分频功能的 BUFR 时,非分频 BUFR 应将 BUFR_DIVIDE 设置为 1 而不是 BYPASS,以确保在时钟区域内实现最佳时钟对齐。

每个时钟区域的单个缓冲器

驱动多个BUFIO

当只驱动跨三个时钟区域的 I/O 逻辑时,BUFMR 可以驱动三个 BUFIO。 尽管 BUFR 可以执行此功能,但 BUFIO 提供最高性能的操作并驱动 I/O 列中的专用时钟网络。 将三个 BUFIO 的 I/O 逻辑分组为三个独立的子集,每个子集由其自己的 BUFIO 提供时钟1。

驱动多个 BUFR

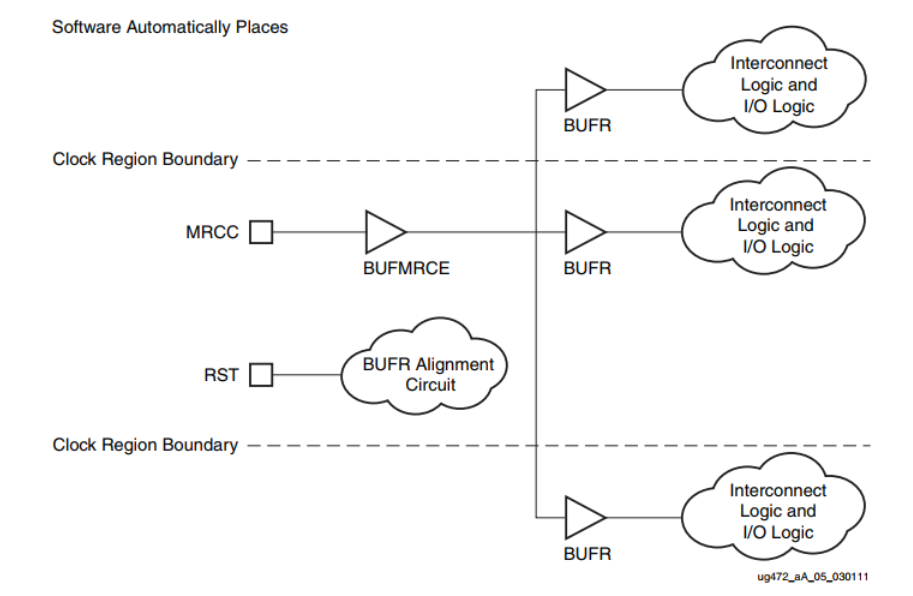

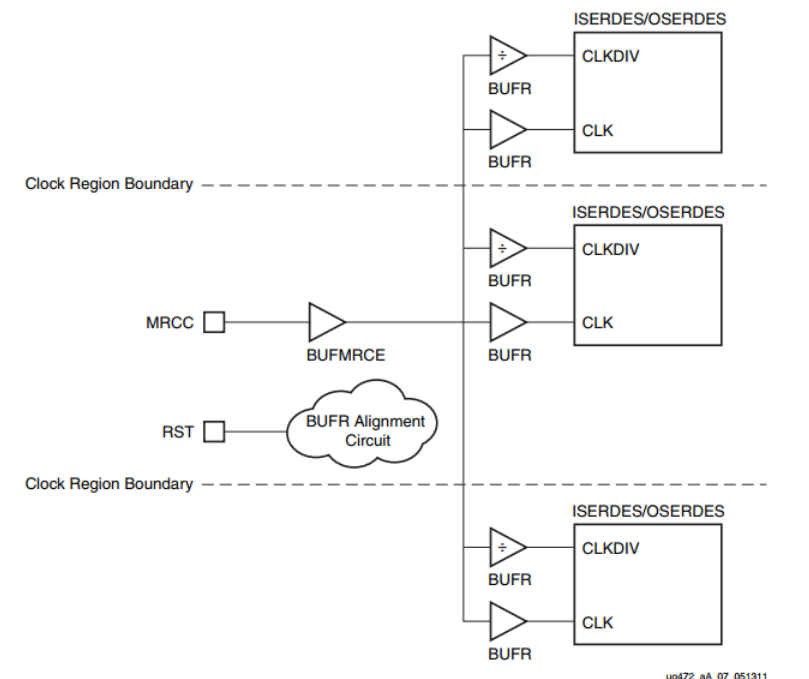

在跨三个时钟区域以相同时钟速率从相同时钟源驱动互连逻辑和 I/O 逻辑时,请使用 BUFMRCE 原语(带时钟使能的多区域时钟缓冲器)。 一个 BUFMRCE 可以驱动三个 BUFR,而这三个 BUFR 又驱动互连逻辑和 I/O 逻辑。 将由三个 BUFR 计时的逻辑分组为单独的子集,每个子集由其自己的 BUFR 驱动。

如果正在使用 BUFR 中的分频值,则必须在禁用 BUFMRCE 时重置所有 BUFR 实例。布局器软件会自动将缓冲区放置在适当的位置。

每个时钟区域的多个缓冲器

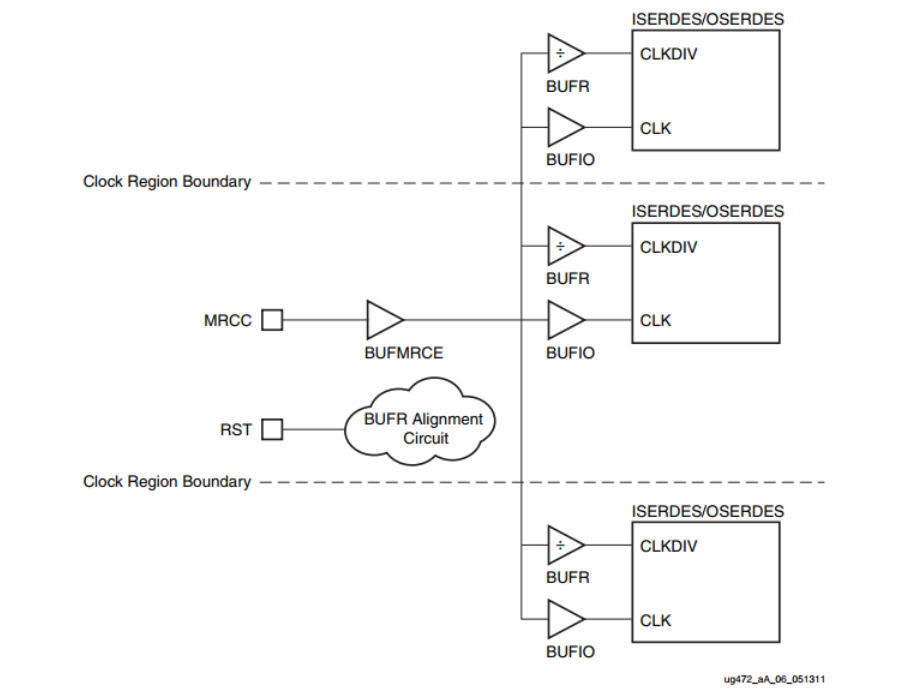

驱动多个 BUFR(带分频)和 BUFIO

驱动 ISERDES/OSERDES CLK 和 CLKDIV 引脚时,将 BUFIO 与已激活分频功能的 BUFR 结合使用。 BUFIO 为 ISERDES/OSERDES 的 CLK 端口驱动干净、低偏差的时钟,而 BUFR 驱动较慢的 CLKDIV 输入。

例如在下图中,当 250 MHz 输入时钟通过 MRCC 引脚进入 FPGA 时,BUFIO 以 250 MHz 的全速率驱动 CLK 输入,BUFR_DIVIDE=2 的 BUFR 驱动 CLKDIV 输入 125 MHz的半速率。

以这种方式驱动多个缓冲区时,手动放置具有 LOC 约束的缓冲区。 由缓冲器驱动的逻辑会自动放置在适当的位置。

驱动多个 BUFR(有和没有分频)

与上图中的示例类似,如果 BUFIO 不可用(用于其他目的),则 ISERDES/OSERDES 的 CLK 输入可以由 BUFR 驱动。

当一个 BUFMR 驱动三个以上的 BUFR 时,手动放置带有 LOC 约束的 BUFR。 由 BUFR 驱动的逻辑会自动放置在适当的位置。

BUFR 对齐

当使用 BUFR 的内置分频功能时,时钟必须在 BUFMR 处停止并将复位信号应用于 BUFR,以在多个 时钟区域。这将需要使用 BUFMRCE 原语,它允许您在复位期间禁用 BUFMR 的输出。要成功对齐相邻区域中的 BUFR,必须遵循以下程序:

- 将时钟使能连接到 CE 端口 BUFMRCE

- 将 BUFMRCE 的 CE 引脚保持在其无效状态以禁用 BUFMRCE 的输出

- 通过向 BUFR 的 CLR 引脚施加复位信号来复位所有 BUFR

- 在 BUFR 复位/CLR 后重新启用 BUFMRCE 信号被施加

- 释放BUFR 上的reset/CLR 信号 所有BUFR 必须在同一个时钟周期内释放,以确保所有BUFR 输出时钟的相位对齐

要在电路操作期间关闭时钟,即在解除置位 BUFR 的复位/CLR 信号后,请使用其 CE 引脚禁用 BUFMRCE。 这可确保在时钟信号恢复时 BUFR 继续对齐。 BUFMRCEs CE 引脚应至少在一个输入时钟周期内有效。

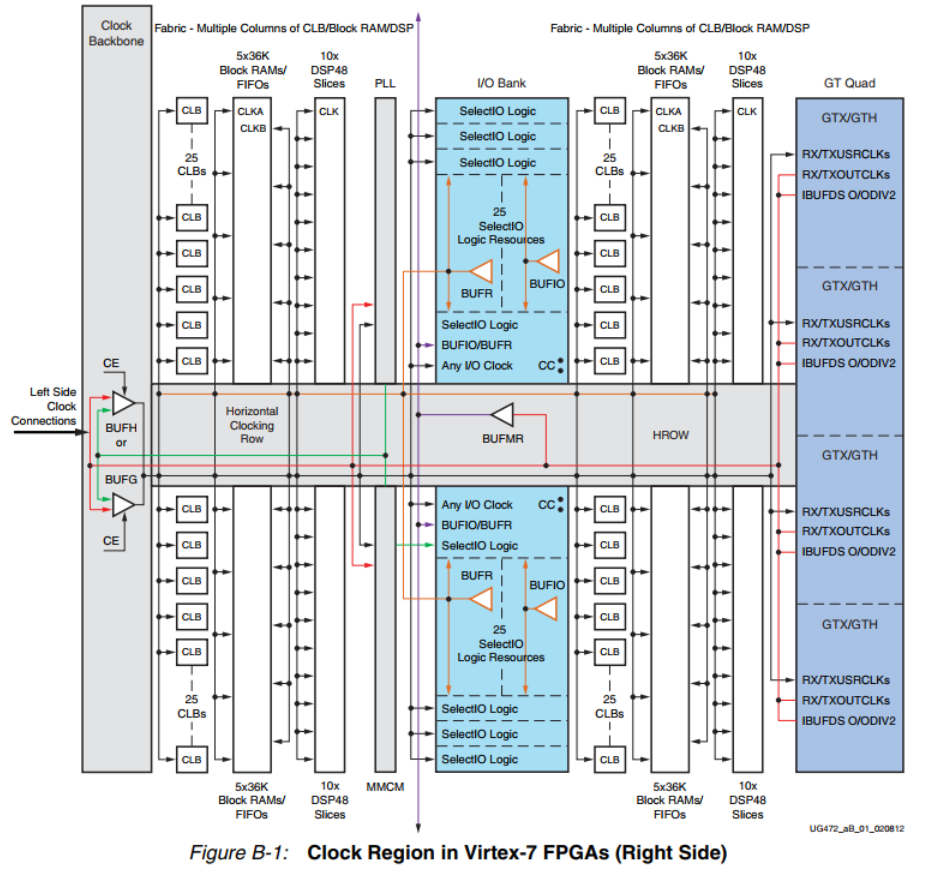

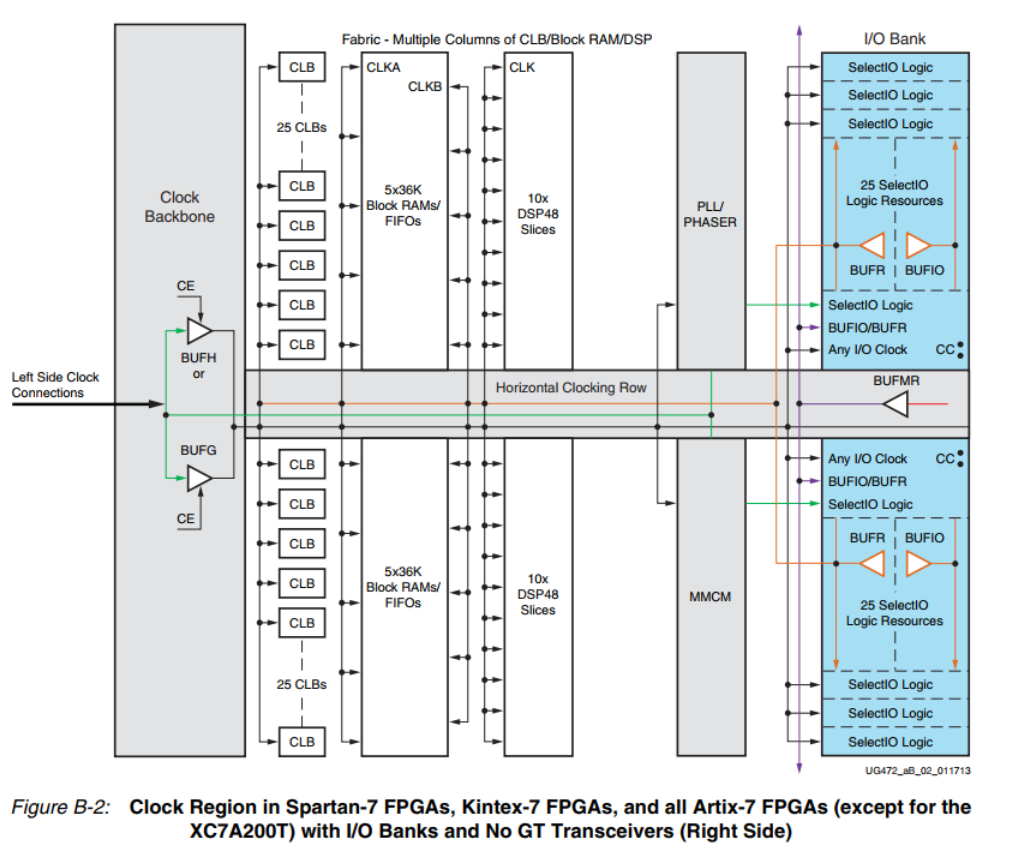

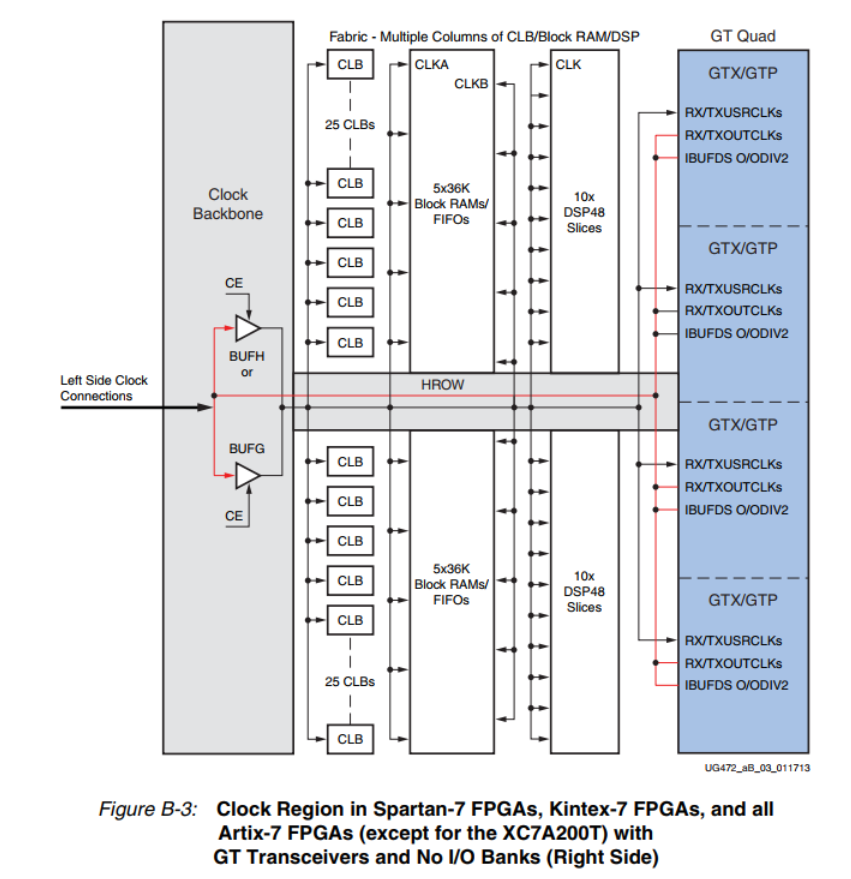

每个时钟区域的时钟资源和连接变化

下面几个图显示了不同型号的器件时钟区域的时钟资源和连接。

reference

- UG472

边栏推荐

- Shell implements basic file operations (SED edit, awk match)

- 基于ARM RK3568的红外热成像体温检测系统

- 飞凌搭载TI AM62x的ARM核心板/开发板首发上市,亮相Embedded World 2022

- 瑞萨RZ/G2L ARM开发板存储读写速度与网络实测

- Vulkan performance and refinement

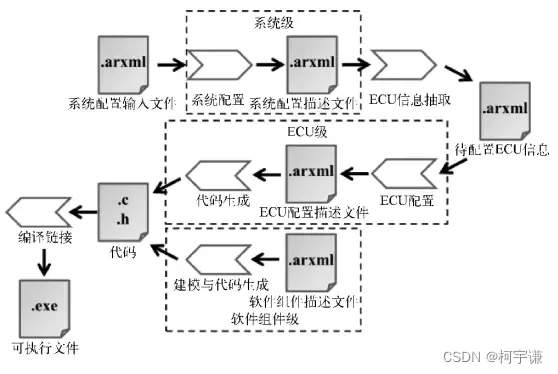

- 【AutoSAR 七 工具链简介】

- leetcode-241:为运算表达式设计优先级

- [golang syntax] map common errors golang panic: assignment to entry in nil map

- 全志A40i/T3如何通过SPI转CAN

- [AUTOSAR twelve mode management]

猜你喜欢

【AutoSAR 五 方法论】

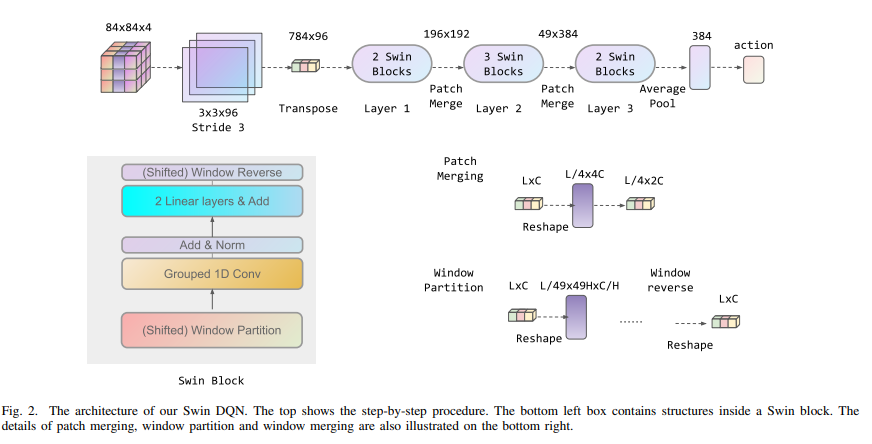

奥斯陆大学:Li Meng | 基于Swin-Transformer的深度强化学习

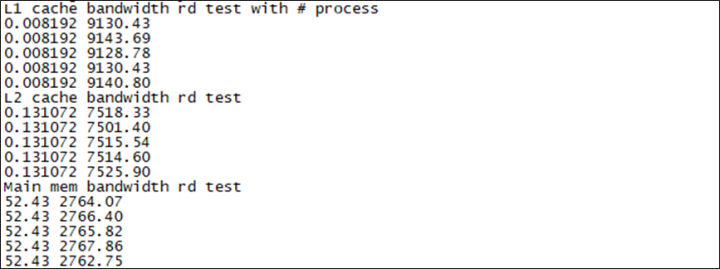

瑞萨RZ/G2L ARM开发板存储读写速度与网络实测

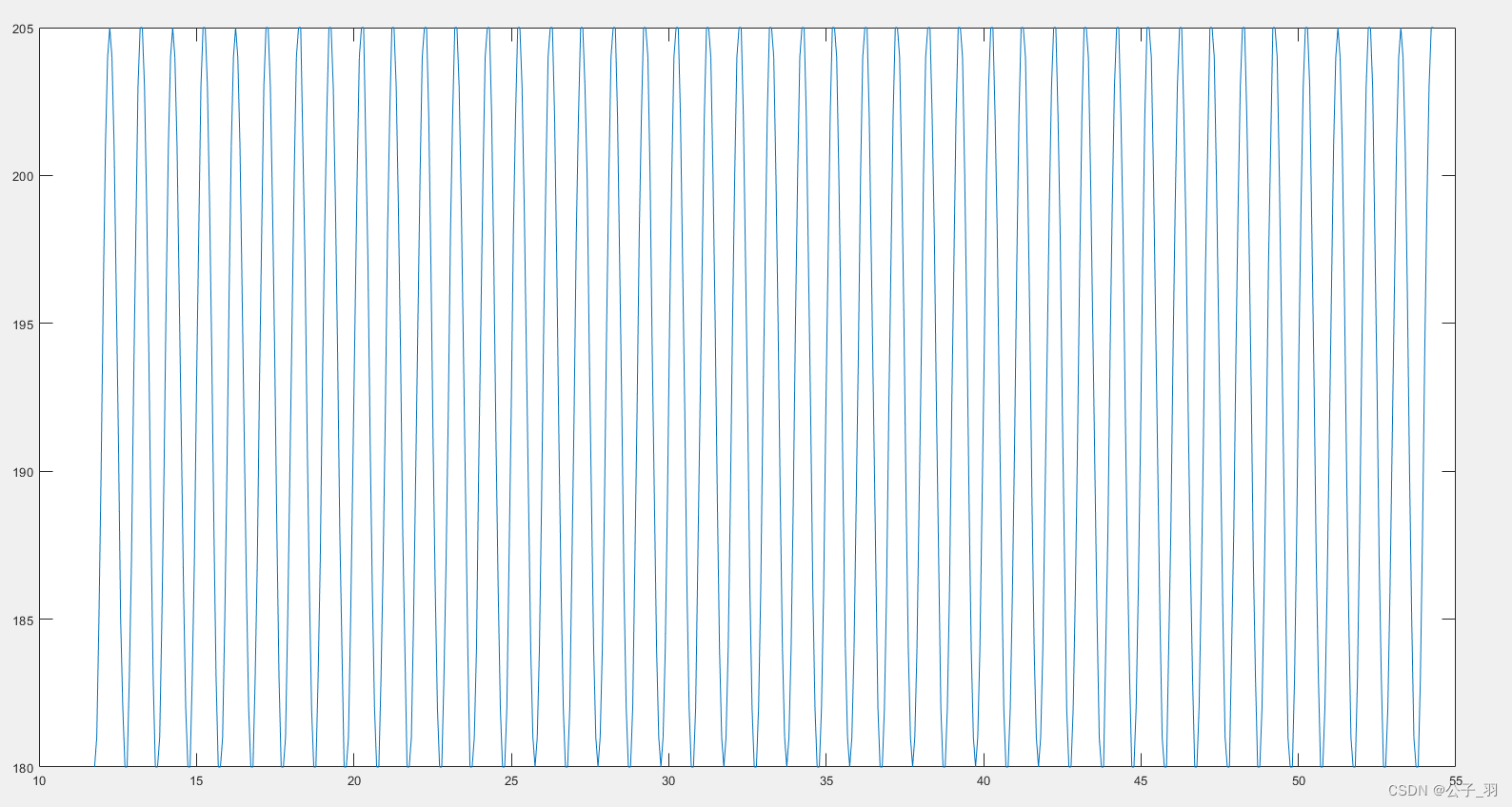

Key detection and sinusoidal signal output developed by Arduino

RK3568开发板评测篇(二):开发环境搭建

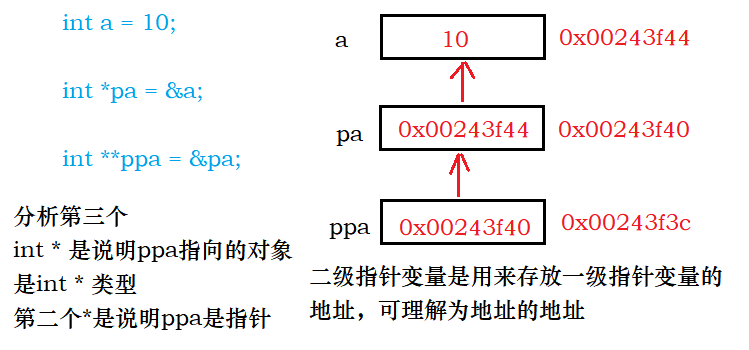

Deep analysis of data storage in memory

数学建模之线性规划(含MATLAB代码)

指针初阶(基础)

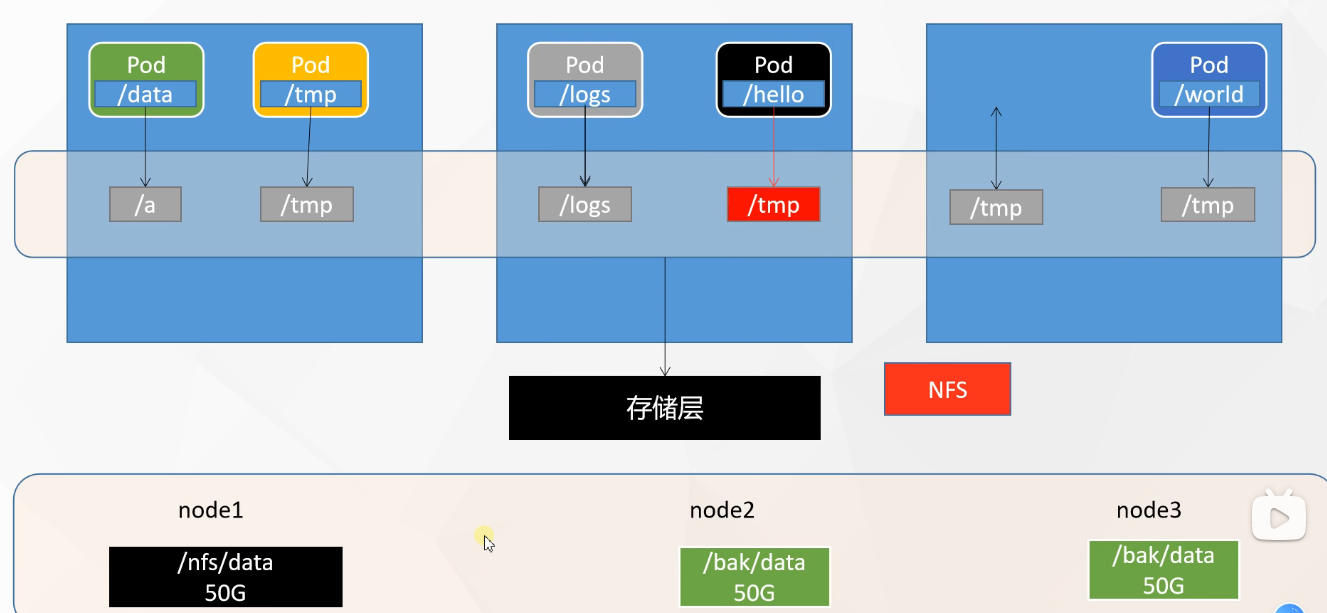

Kubernetes resource object introduction and common commands (V) - (NFS & PV & PVC)

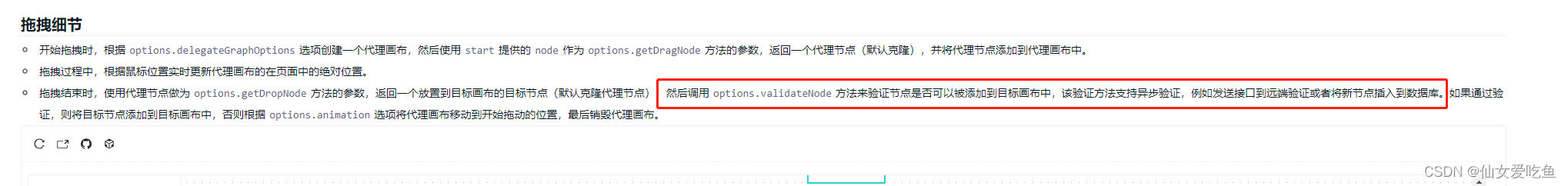

antv x6节点拖拽到画布上后的回调事件(踩大坑记录)

随机推荐

Array common operation methods sorting (including ES6) and detailed use

Win10 多种方式解决无法安装.Net3.5的问题

[AUTOSAR twelve mode management]

【AutoSAR 五 方法论】

【AutoSAR 七 工具链简介】

Vulkan-实践第一弹

Shell 实现文件基本操作(切割、排序、去重)

Leetcode 294. Flip game II (game theory)

KingbaseES ALTER TABLE 中 USING 子句的用法

瑞萨电子RZ/G2L开发板上手评测

MySQL multi table joint deletion

Initial order of pointer (basic)

数组与集合性能比较

University of Toronto: Anthony coach | the conditions of deep reinforcement learning can induce dynamic risk measurement

Web2.0的巨头纷纷布局VC,Tiger DAO VC或成抵达Web3捷径

[overview of AUTOSAR four BSW]

leetcode-224:基本计算器

Machine learning: numpy version linear regression predicts Boston house prices

Leetcode-934: the shortest Bridge

Vulkan-性能及精细化