当前位置:网站首页>Verilog除法器的设计总结

Verilog除法器的设计总结

2022-06-21 20:40:00 【吉大秦少游】

Verilog除法器的设计总结

1 概述

Verilog实现除法器需要根据实际使用场景进行调整,但整体来说实现的算法有两类:

- 基于减法和移位实现除法

- 基于乘法和移位实现除法

下面将对两类算法的实现过程和原理进行总结,并给出基本的实例。

2 基于减法和移位实现除法

2.1 组合逻辑实现的实例

对于32的无符号除法,被除数a除以除数b,他们的商和余数一定不会超过32位。首先将a转换成高32位为0,低32位为a的temp_a。把b转换成高32位为b,低32位为0的temp_b。在每个周期开始时,先将temp_a左移一位,末尾补0,然后与b比较,是否大于b,是则temp_a减去temp_b将且加上1,否则继续往下执行。上面的移位、比较和减法(视具体情况而定)要执行32次,执行结束后temp_a的高32位即为余数,低32位即为商

/*

* module:div_rill

* file name:div_rill.v

* syn:yes

* author:network

* mo边栏推荐

- GDB debugging practice (10) multi thread debugging

- 【深入理解TcaplusDB技术】如何实现Tmonitor单机安装

- Use for, while and do while to find the sum of 1-100 circularly

- 采样器合集

- 力扣刷題集結4(mysql版本)

- IP guard printing control to prevent information disclosure of printing channels

- fork-join线程池

- mafft|多序列比对工具

- 电脑屏幕分辨率怎么调?电脑屏幕修改分辨率SwitchResX

- [deeply understand tcapulusdb technology] one click installation of tmonitor background

猜你喜欢

Dragon lizard community established cloud native SIG and introduced three core technologies

MitoZ|Multi-Kmer mode

![[deeply understand tcapulusdb technology] tcapulusdb import data](/img/a8/04c4c6703a6137d17666f211d7988d.png)

[deeply understand tcapulusdb technology] tcapulusdb import data

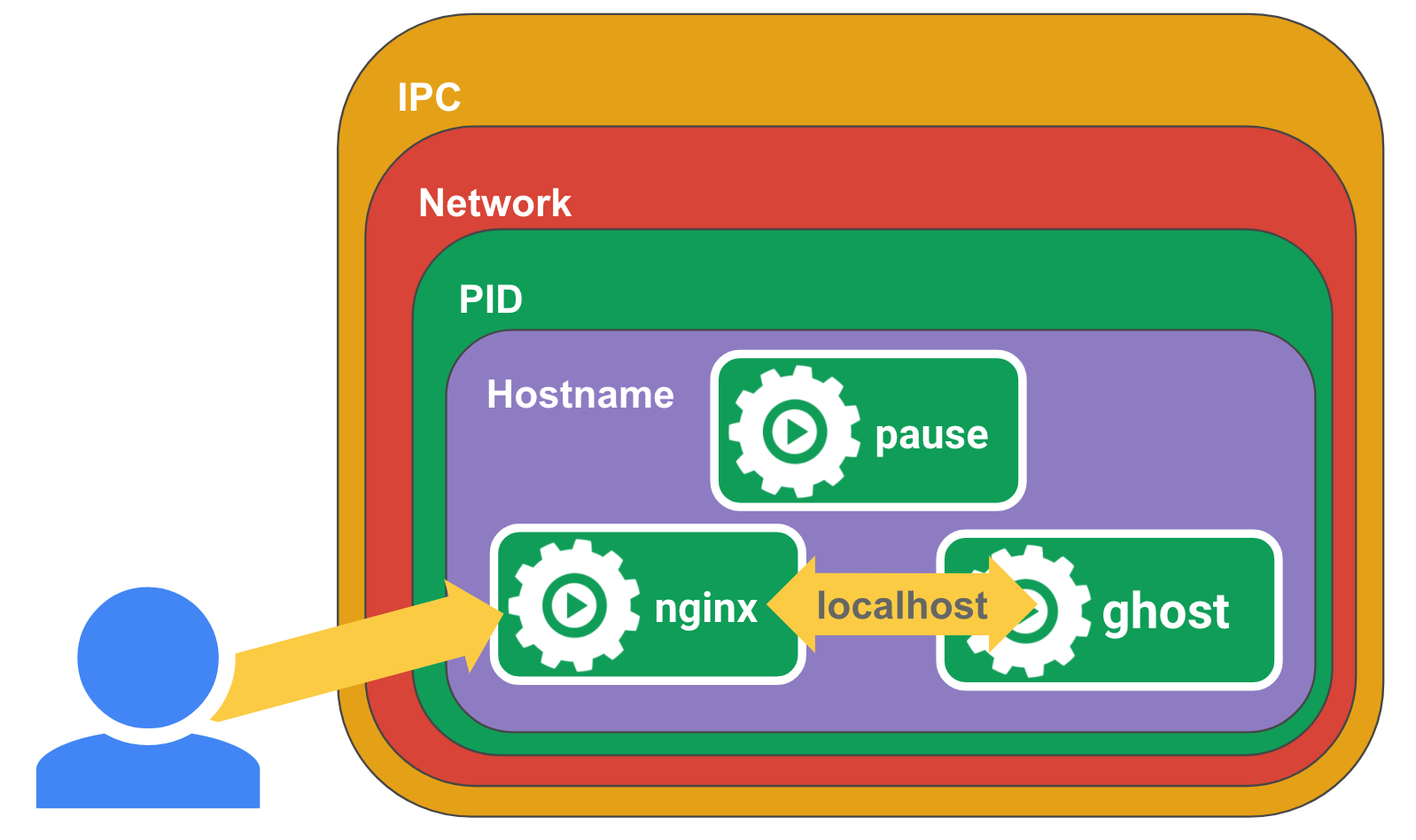

技术分享 | kubernetes pod 简介

迅为iTOP-3568开发板安装 RKNN Toolkit Lite2

Notes on topic brushing (16) -- binary tree: modification and construction

刷题笔记(十六)--二叉树:修改与构造

Leetcode question brushing: SF Technology Smart logistics Campus Technology Challenge

【深入理解TcaplusDB技术】TcaplusDB构造数据

HIC Pro | HIC data processing tool

随机推荐

UEFI 双系统+双硬盘安装

翻译软件Bob安装教程

University of Virginia: ingy Elsayed aly | logic based reward formation in Multi-Agent Reinforcement Learning

实验二 栈和队列

左手代码,右手开源,开源路上的一份子

利用for循环,分别计算1-100中奇数的和、偶数的和【方法一】

【深入理解TcaplusDB技术】TcaplusDB构造数据

Anaconda添加channels

HIC Pro | HIC data processing tool

001 new construction project based on opencvsharp

采样器合集

【深入理解TcaplusDB技术】Tmonitor系统升级

【深入理解TcaplusDB技術】TcaplusDB構造數據

Use the do while loop to calculate the odd and even sums in 1-100 [method 2]

可乐与凉茶加速互卷

专业字体设计编辑Glyphs 3

promise错误捕获处理——Promisifying技术

实践 DevOps 时,可能面临的六大挑战

[in depth understanding of tcapulusdb technology] tcapulusdb construction data

Iqtree| software for constructing evolutionary tree