当前位置:网站首页>PCIE电路设计

PCIE电路设计

2022-08-02 03:29:00 【Hzy_520】

PCIE接口

PCIE分有X1,X2,X4,X8,X16,对应PC、服务器设计来说,使用这些座子,支持插入的PCIE设备,连接到CPU,或者南桥,实现其功能。

典型设计上,还有MINI-PCIE座子,但是走的信号都是一样的,只是座子规格不一致。

下图是PCIEX4的电路设计:

时钟

PCIE有一对100M的差分时钟提供给PCIE设备。一般由CPU提供,或者单独的时钟发生器产生,与data信号可以是独立的,即data从CPU出来,clk可以使用另外的时钟发生器提供。

DATA

X4意味着有四对差分对,X16有16对差分对,其他同理。

以CPU举例,将其引出X4的PCIE,一般是需要连续的,比如取0-3,或者4-7,以此类推,需要看CPU PCIE控制器规格书,看其控制器的分布,对Inter来说,为PDG,EDS。

下图实例(此实例较特殊,其首个PCIE序号是1而不是0,懂意思即可)

系统管理总线时钟

SMCLK,SMDAT,直连即可,其总线形式意味着可以像IIC一样,共联多个PCIE设备。

热拔插信号

PRSNT1,PRSNT2。电路设计来说,会将PRSNT1直接接地,在PCIE设备端,PRSNT1和PRSNT2是直连的,因为我们PC端只要检测到PRSNT2为低电平(接上拉电阻),认定为插入了PCIE设备,此信号用在CLKREQ上,对于CPU的PCIE时钟发生来说,当CLKREQ为低电平,其对应的时钟启动输出,否则不输出。这是热拔插的信号意义,也可以不使用REQ功能,直接在任何情况下都拉低。

复位信号

PWRGD,就是power good。只有PWRGD正常,PCIE才会工作,因此可以当作复位来使用。

唤醒信号

wake,低电平有效。

电源

需要提供12V和3.3V输出。

测试信号

JTAG,调试使用,不接也可以。

M.2接口

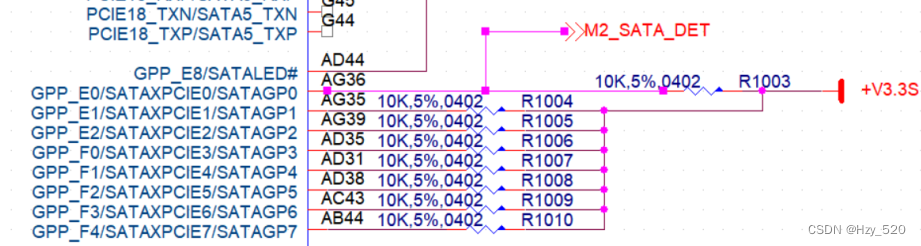

这个接口走的是PCIE或者SATA信号,第一组PCIE通道要支持SATA,见图二的PCIE9,PCIE10,就支持SATA协议。

PEDET是用来区分插入的设备是PCIE设备还是SATA设备,需要使用固定的IO,高电平为PCIE设备,低电平为SATA设备。如果插入设备固定,可以直接硬上下拉。

对比来说还多了一个LED,需要注意的是,M.2设备只对这个LED信号进行拉高拉低操作,我们电路上需要设计VCC,通常是3.3V,限流电阻,通常是330R,LED也是在我们板子上设计的。

边栏推荐

猜你喜欢

随机推荐

远程调试PLC,到底如何操作?

umi3 权限路由PrivateRoute未执行

Two-Stream Convolutional Networks for Action Recognition in Videos双流网络论文精读

【霍尔效应传感器模块与 Arduino】

网站开发方案研究

工业边缘网关究竟强大在哪里?

Cadence allegro导出Gerber文件(制板文件)图文操作

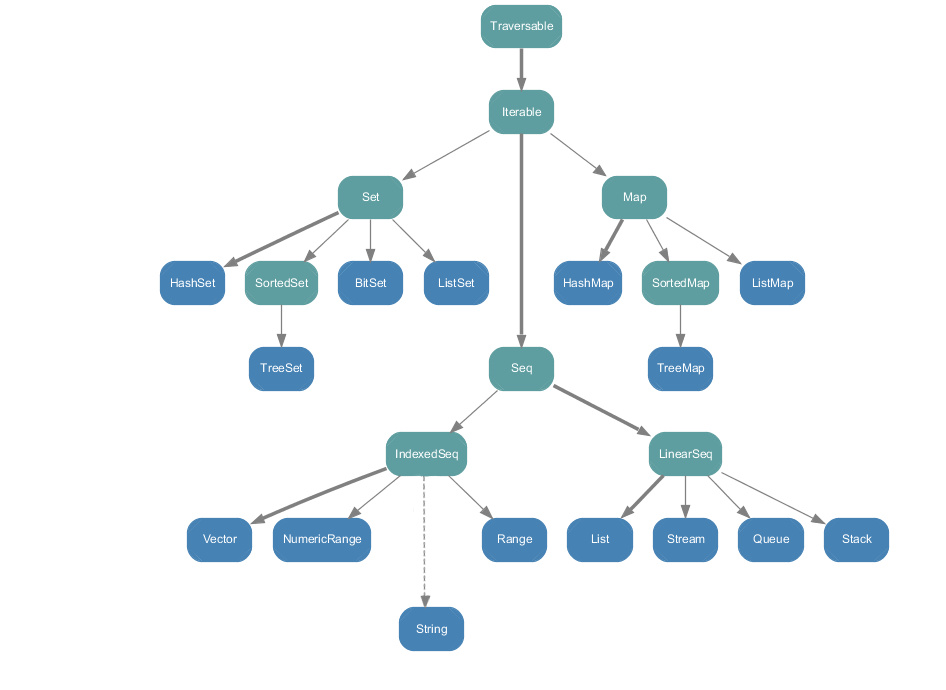

《scala 编程(第3版)》学习笔记2

MPU6050 加速度计和陀螺仪传感器与 Arduino 连接

【nRF24L01 与 Arduino 连接实现无线通信】

【心率传感器与Arduino连接读取心率数据】

Go 程序太大了,能要个延迟初始化不?

关于我的项目-微信小程序2(uniapp->wx小程序)

【Arduino 连接GP2Y1014AU0F 灰尘传感器】

3D建模作品

uniCloud使用

阿里云华为云对比分析

【Arduino 连接DHT11 湿度和温度传感器】

VS2017报错:LNK1120 1 个无法解析的外部命令

【Arduino 连接 SD 卡模块实现数据读写】

![[Spark]-协同过滤](/img/18/8129e96758160b7e5cc9814d50d882.jpg)