当前位置:网站首页>i. MX - rt1052 boot start

i. MX - rt1052 boot start

2022-06-21 12:12:00 【Summer foam and light rain】

Write it at the front :

The purpose of this article is to summarize backup 、 For future reference , Because it's a personal summary , If there is any wrong , Welcome to correct ; in addition , Most of the content comes from the Internet 、 Books 、 And all kinds of manuals , In case of infringement, please inform , Immediately delete the post and apologize .

Catalog

sketch

You can know from the reference manual i.MX RT1052 guide ROM The following boot devices are supported :

these BOM It is mainly used for the following functions :

1、Serial NOR/NAND Flash via FlexSPI

stay BOM The first two can be combined on the boot device , They all use FlexSPI The peripheral interface is externally connected , Only one is NOR Flash, The other is NAND Flash; Some of their introductions can be referred to :https://www.cnblogs.com/henjay724/p/12375942.html

that EVKB It's expensive to die on the board HyperFlash Namely NOR Flash, The interfaces connected are as follows ( notes :FLEXSPI_B_SCLK Here is GPIO_SD_B1_04 Pin ):

stay boad There is another one on the NOR Flash Series of 64M QSPI Flash, utilize FlexSPI NOR Flash - QSPI Inside 6 root FLEXSPI_A_xxx The signal wire connects four wires QSPI Flash

2、Parallel NOR Flash via SEMC

Reference resources :https://www.cnblogs.com/henjay724/p/9188252.html

3、RAWNAND Flash via SEMC

Reference resources :https://www.cnblogs.com/henjay724/p/9173425.html

4、SD/MMC

Just as the name suggests , It's using SD card perhaps eMMC

5、SPI NOR/EEPROM via LPSPI

Reference resources :https://www.cnblogs.com/henjay724/p/9286385.html

Inside ROM/RAM Memory mapping

You can see from the picture above ,ROM The starting address is 0x200000, The size is 96KB.

On chip storage

1、I - Cache and D - Cache

Chip functional architecture block diagram :

You can see from the picture above that RT1052 There is... In the chip I - Cache and D - Cache Each one , Their sizes are all 32KB.

I - Cache

ICache, Instruction cache (Instruction Cache), The kernel accesses this memory at a very high speed . Its function is to cache the instructions to be executed , That is, the kernel depends on the operation of the code , From other memory in advance ( Such as external Flash, external SDRAM etc. ) Load code that may be executed and store it in ICache; According to official statistics ,ICache The hit rate of instruction cache can reach 98% above , That's why i.MX RT The serial chip code is stored externally FLASH, The running speed is still so fast , And because of ICache The existence of , Programs are stored in SD card 、NAND FLASH Etc. not supported XIP Memory has also become possible .

D - Cache

DCache, Data cache (Data Cache), It is associated with ICache Similar function of , Play the role of cache , The difference is only ICache Dedicated to storing instructions ,DCache Dedicated to storing data .

2、FlexRAM

First look at i.MX - RT Features of the series :

You can see from the above picture that RT1050 The series is configured with 512 kB SRAM Of ; Look at the picture below :

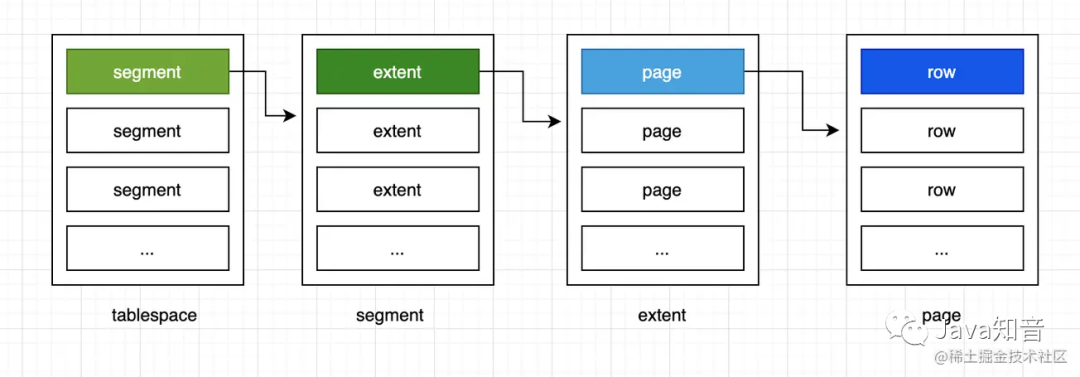

FlexRAM, Flexible RAM, stay RT1052 The size of the chip is 512KB, It can be understood as tradition MCU Internal SRAM Memory , It just adds the configuration of divisible functional areas , Respectively, we can put this inside SRAM Divided into... Dedicated to storing instructions ITCM, Dedicated to storing data DTCM And general functions OCRAM.

Its block diagram is as follows :

The following figure shows this FlexRAM bank Detailed configuration of :

- First of all ITCM,ITCM yes Instruction Tightly-Coupled Memory Abbreviation , Instruction tightly coupled memory . Tight coupling means that the memory is closely connected with the kernel , Very high access speed , and ” Instructions “ Indicates that the memory is dedicated to caching instructions . For code that we want to have very high execution speed , We can ask the kernel to turn on the corresponding code from the outside FLASH Load to ITCM, So at runtime , The execution speed of the code will not be affected by external factors FLASH There is a bottleneck in the access speed .

- DTCM, yes Data Tightly-Coupled Memory Abbreviation , Data tightly coupled memory , It goes with ITCM similar , It has extremely high access speed , But it is specially used to store program data , That is, the storage location of variables in the code .

- OCRAM, It is On-chip RAM Abbreviation , On chip memory , It can be fully understood as tradition MCU Internal SRAM, It has no image. ITCM and DTCM Special restrictions for , Can be used to store instructions and data ( General purpose )

3、 The speed ranking of each memory access

among ICache and DCache It is used automatically by the kernel , Users cannot access . and ITCM、DTCM And OCRAM The user can access according to the specific address , Programs should be developed to take advantage of their characteristics .

for example , hold FlexRAM bank The configuration is as follows :

Boot device support

The chip supports the following boot flash devices ( There is a brief introduction at the beginning , But here's a little more consolidation ):

- adopt FlexSPI Serial interface NOR Flash memory

- adopt FlexSPI Serial interface NAND Flash memory

- With intelligent external memory controller (SEMC) Parallel of NOR Flash memory , be located 16 Bit bus width CS0 On .

- have SEMC Interface NAND Flash memory , be located CS0 On , The bus width is 8 position / 16 position .

- adopt uSDHC Interface SD / MMC / eSD / SDXC / eMMC4.4, Supports large capacity cards

- adopt LPSPI Serial NOR / EEPROM guide

The type of external boot device is selected by BOOT_CFG1 [7:4] eFUSE control :

BOOT Mode Pin settings

The device has four boot modes ( One reserved for NXP Use ). According to the interior BOOT_MODE The binary value stored in the register selects the boot mode .

By means of POR_B On the rising edge of BOOT_MODE0 and BOOT_MODE1 Input for sampling to initialize BOOT_MODE. After sampling these inputs , Their subsequent status does not affect BOOT_MODE Contents of internal registers . Inside BOOT_MODE The state of the register can be changed from SRC Boot mode register (SRC_SBMR2) Of BMOD [1:0] Read... In the field . The available boot modes are : from Fuses guide , adopt USB Serial boot and internal boot . Here's the picture :

Boot From Fuses Pattern (BOOT_MODE[1:0] = 00b) :

When BOOT_MODE[1:0] The register is 00b yes , Select from Fuses Start in mode . This mode is very similar to the internal startup mode , It's just a little different : In this mode ,GPIO The start overload pin is ignored .

Fuse There are some and BOOT Relevant information , Can pass Fuse About BOOT The configuration of determines from which external storage BOOT. If configured from Fuses start-up , Start the flow (boot flow) Will receive BT_FUSE_SEL eFUSE Value control .

BT_FUSE_SEL eFUSE The value of determines the behavior in this mode :

BT_FUSE_SEL = 0: Indicates that there is no... In all external memory Application, here Boot From Fuses Pattern is equivalent to Serial Downloader Pattern .

BT_FUSE_SEL = 1: Indicates that there is a valid... In the external memory Application, here BootROM Will be based on Fuse In the other Boot The configuration information further selects the specified external memory (Boot Device) Go to Boot.

Serial Downloader Pattern (BOOT_MODE[1:0] = 01b) :

Serial download mode , In this mode ,BootROM By the appointed USB perhaps UART To receive from PC Terminal Application data , And store the data in SRAM In the implementation of . This model is actually from SRAM start-up , But if you use this model Boot Application The disadvantages are obvious , Every time you power on, you need to turn Application Download it again SRAM, Can't do offline automatic Boot, So obviously the main purpose of this model is not to SRAM start-up Application, It is mainly used to learn from SRAM Start in Flashloader, NXP officially provided Flashloader Program ,Flashloader The program can be used to put your Application Download into i.MX RT In all external nonvolatile memory supported , Prepare for subsequent boot from external memory ; in addition to Serial Downloader Patterns can also be used to view Fuse value .

Internal Boot Pattern (BOOT_MODE[1:0] = 10b) :

BOOT_MODE[1:0] The value of the register is 10b when , Select as internal (Serial NOR /NAND、Parallel NOR /NAND、SD /eMMC All external nonvolatile memory supported by ) Boot mode . In this mode , The processor will continue to boot internally ROM Execute boot code .

Start code to perform hardware initialization , Load the program image from the selected boot device , Use HAB Perform mirror validity check , Then jump to the program image address . If there are any errors in the internal startup , The startup code will jump to the serial downloader . In three modes , Safe start can be used HAB. When using internal boot mode , Start the flow (boot flow) By eFuse Configuration and GPIO heavy load Fuse Controlled by a combination of the two .

Internal Boot The pattern is actually the same as Boot From Fuses The pattern is very similar , It's just that in this mode BT_FUSE_SEL It's a little different :

BT_FUSE_SEL = 0: have access to GPIO Pin instead of eFUSE To set specific boot configuration parameters . In the picture below Boot eFUSE Stated GPIO In the column , Indicates which... Can be overridden in this mode Fuse.

in addition , Below GPIO boot overrides The list provides GPIO Pin details :

BT_FUSE_SEL = 1: All boot options are booted by eFUSE Described in the description eFUSE control .

BOOT choice

i.MX RT series MCU Of Flash, except i.MX RT 1064 Have internal NOR Flash, Other models don't have an interior Flash, This means that we need to expand Flash To store Application, According to the expanded Flash class Different types , It is divided into NOR Flash And non NOR Flash,NOR Flash Sure XIP, Not NOR Flash must not XIP.

stay MIMXRT1050 EVKB board Upper Boot Mode selection via switch SW7 Set up ; switch (SW7-3 and SW7-4) For choosing MIMXRT1050 EVKB Startup mode on board . As shown in the figure below :

Normal startup usually selects internal startup , Through the outside BOOT_CFG GPIO To configure . The following figure shows typical startup modes and startup device settings .

Boot Start downloading the instance diagram :

The relevant address of the startup

| Start Address | End Address | Size | Description |

|---|---|---|---|

| 0x80000000 | 0xDFFFFFFF | 1.5GB | SEMC External memory interface (SDRAM, parallel NOR Flash,PSRAM, parallel NAND Flash) |

| 0x60000000 | 0x7F7FFFFF | 504MB | FlexSPI |

| 0x20200000 | 0x2027FFFF | 512KB | OCRAM |

| 0x20000000 | 0x2007FFFF | 512KB | DTCM |

| 0x00000000 | 0x0007FFFF | 512KB | ITCM |

other

In addition to the links cited above for reference , There are also the following reference links :

https://ebf-imxrt1052-tutorial.readthedocs.io/zh/latest/doc/chapter5/chapter5.html#id5

https://www.cnblogs.com/henjay724/p/9034563.html

https://www.wpgdadatong.com/cn/blog/detail?BID=B0619

https://blog.csdn.net/likeping/article/details/101028117

https://blog.csdn.net/metersun/article/details/52022233

边栏推荐

猜你喜欢

Travel does not heal the soul

harmonyos培訓一

Rename all files in the folder with one click

Introduction to common source oscilloscope software and RIGOL oscilloscope upper computer software ns-scope

第八章 Web项目测试

站在数字化风口,工装企业如何“飞起来”

异质化社群量化研究4丨RATE OF CHANGE WITH BANDS

使用Huggingface在矩池云快速加载预训练模型和数据集

100w的数据表比1000w的数据表查询更快吗?

2022 special operation certificate examination question bank and online simulation examination for safety management personnel of hazardous chemical business units

随机推荐

1108. IP 地址无效化

WPF 使用 MAUI 的自绘制逻辑

Embedded struct and embedded interface

动手学数据分析 数据可视化

RPC(远程过程调用协议)

STM32笔记之 PWM(脉宽调制)

What are the precautions for PCB design?

Ansible 配置首次ssh免认证的操作说明

Transaction

RPC (remote procedure call protocol)

Related codes of findpanel

i.MX - RT1052 SDCard操作(SDIO接口)

Corrigendum to 138 sets of reference solutions to the real problems of Higher Algebra in 2022

Tensorflower使用指定的GPU和GPU显存

2022 safety officer-b certificate retraining question bank and simulated examination

2022 HV electrician judgment questions and answers

Knowledge points: several special wiring methods for PCB

Customization of power aging test system | overview of charging pile automatic test system nsat-8000

STL basic container test

MySQL-DDL