当前位置:网站首页>基于断言的验证

基于断言的验证

2022-06-22 05:33:00 【傻童:CPU】

基于断言的验证

断言的概念十分简单。只要在程序中声明,我们相作言某事情必定为真,若不为真,则在屏幕上打印错误信息即可。在 SystemVerilog语言中,断言可以用立即(immediate)和并发(concurrent)两种不同形式的断言来表示。立即断言十分简洁,可以用if、else等语句表示。而并发断言的功能十分强大,所以本节用大部分篇帽福讲解如何编写并发断言。

在 always过程块中可以把这个事实声明为立即断言(该立目即断言相当于一个always_comb过程块,但是为了避免概念混淆,我们只在可综合的RTL模块中使用always_comb)。

always @*

assert(~(dispense&&ready))

else $error("dispense and ready both lit!");

上面这个断言每当dispense或者ready信号变化时,就检查它们是否同时为1。但是最好在时钟的正跳变沿检测这个条件,因为我们检查的是一个同步系统。首先把这个条件编写为如下属性property:

property NotDispenseAndReady;

@(posedge clock)(~(dispense && ready));

endproperty

然后,作为并发断言的一部分,对这个属性进行测试,其代码如下:

assert property(NotDispenseAndReady);

可以把属性定义和断言声明合并在一起编写。但是常用的编程风格建议,为了属性的重复使用,最好将属性定义和断言声明分成两部分编写。

通常,并发断言

边栏推荐

- Grabcut analysis

- 机器学习笔记 八:Octave实现神经网络的手写数字识别

- Report on global and Chinese direct coupled actuator market demand and future development planning recommendations 2022-2027

- 给仍在「 选品 」的跨境卖家提个醒!

- Current market situation analysis and investment analysis prospect report of global and Chinese ceramic capacitor industry 2022-2027

- vscode极简安装教程

- Parameter serialization

- From "platform transformation" to "DTC brand going to sea", what is the trend of 2021?

- Performance analysis and test of interprocess communication methods under dual core real-time system

- C指针的理解

猜你喜欢

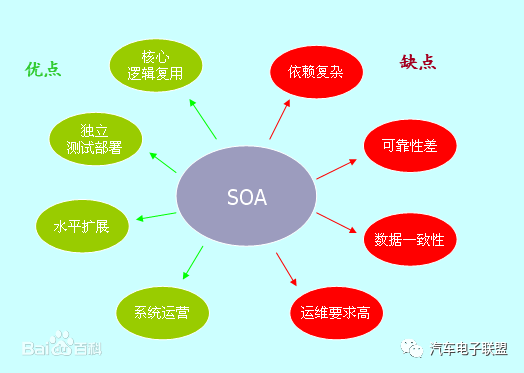

AUTOSAR从入门到精通100讲(150)-SOA架构及应用

C指针的理解

大厂晋升学习方法四:Play 学习法

想投放Facebook广告却不知从何入手?此文带你深入了解

Independent station optimization list - how to effectively improve the conversion rate in the station?

网络、IO流、反射、多线程、异常

u盘作为启动盘重装win10系统(无需其他软件)

Delete the packaging use of pop-up components

Machine learning Note 6: number recognition of multiple classification problems in logistic regression

Throw away electron and embrace Tauri based on Rust

随机推荐

Introduction to golang Viper Library

参数序列化

QEMU ARM interrupt system architecture

Remove then add string from variable of Makefile

基于WebUploader实现大文件分片上传

open source hypervisor

Analysis report on market demand trend and investment prospect of global and Chinese pulse transistor industry 2022-2027

Gerrit Code Review Setup

线性回归:最小二乘、泰尔森估计、RANSAC

机器学习笔记 六:逻辑回归中的多分类问题之数字识别

U disk as startup disk to reinstall win10 system (no other software required)

n个整数的无序数组,找到每个元素后面比它大的第一个数,要求时间复杂度为O(N)

Adaboost

删除弹窗组件的封装使用

想投放Facebook广告却不知从何入手?此文带你深入了解

Someone always asks me: how to play independent station? Three cases, you will understand after reading

Learning method 4 for promotion of big factories: play learning method

大厂晋升学习方法三:链式学习法

Tensorflow 2.x(keras)源码详解之第十四章:keras中的回调及自定义回调

Report on global and Chinese direct coupled actuator market demand and future development planning recommendations 2022-2027