当前位置:网站首页>Inverter Simulink model -- processor in the loop test (PIL)

Inverter Simulink model -- processor in the loop test (PIL)

2022-07-02 09:38:00 【Quikk】

List of articles

inverter simulink Model —— Processor in the loop test (PIL)

1 Basic idea of processor in the loop testing

1.1 Basic introduction of simulation model

During the simulation of normal power electronic system , The structure is mainly divided into main circuit + Control circuit ; The control circuit is generally divided into acquisition circuit and control core .

Take the inverter control system as an example :

DC side voltage source , Three phase inverter unit , filter , The load belongs to the main circuit ;

take 220V The voltage level is converted to the control unit ADC Collectable 0-3.3V Low voltage conditioning circuit is called acquisition circuit ;

take 0-3.3V pulse PWM The signal is converted to IGBT Driving signal (0-24V) The driving circuit of ;

The control core is generally composed of system on chip , Such as STM32、2833X And other basic computing cores ;

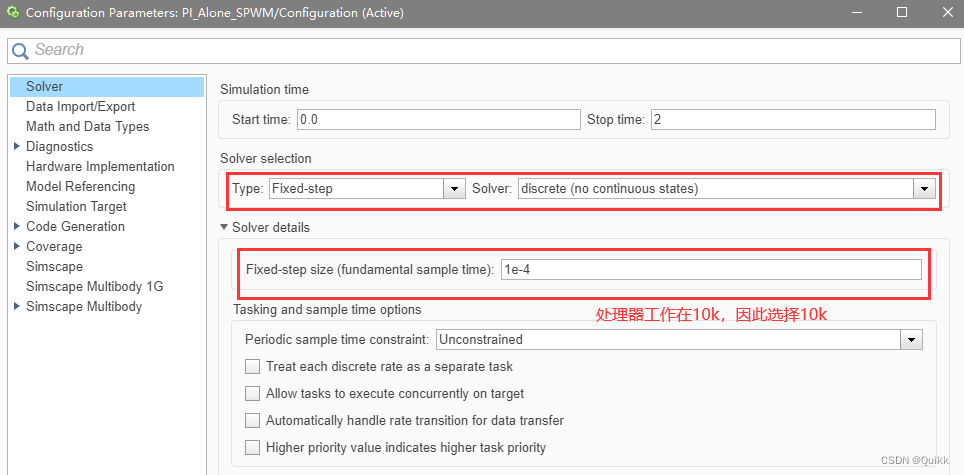

Next, let's introduce the basic principle of simulation , Whether the control circuit or the main circuit is simulink in They are all obtained by numerical calculation . And in the actual system : The main circuit is a real circuit , The control circuit is generally 10k,50k And other fixed frequency control units . In order to realize the simulation of this situation , It is necessary to minimize the calculation step of the main circuit , In order to achieve the purpose of simulating continuous system , And the control system must maintain Normal sampling frequency . Take a particle : If take Slover In steps of 10e-7; Then the external main circuit is represented by 10e-7 The step size is calculated once ; The control unit is 10e-4(10k); You need to 1000 An external step is calculated once for the internal element .

1.2 Processor in the loop test concept

In the actual simulation process , A large number of controllers and external main circuits are PC Terminal CPU To do the operation on . But the actual situation is that the dominant frequency of microprocessors is often much lower than that of computers CPU, The output results may be different from the real situation . However, it often needs lot of time , So you can build ** Processor in loop (PIL)** The test plan of the bottom layer MCU Analyze the operation .

Processor in the loop test , It is to calculate the main circuit in CPU On the implementation , The control circuit operation will be at the bottom MCU On the implementation . The basic process is :

PIL After starting ,MCU Received by PC All kinds of data transmitted ;

MCU Calculate according to the data to get PWM Output the signal and transmit it to PC End ;

PC Termination received PWM After the signal , Apply it to the main circuit , The state of the main circuit changes , Continue to repeat the second step (1) Step

The specific implementation of this scheme will be introduced below ;

2 Processor in the loop test process

2.1 Test model introduction

The test model uses the off grid inverter control model ; Model links : Model links

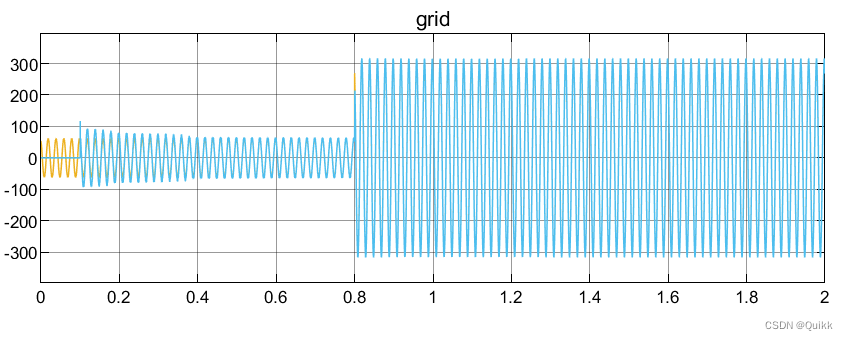

The output voltage waveform under the normal off grid state is shown in the figure ,0.1s Turn on the load supply switch ;0.8s Perform power step ;

2.2 Introduction to basic structure

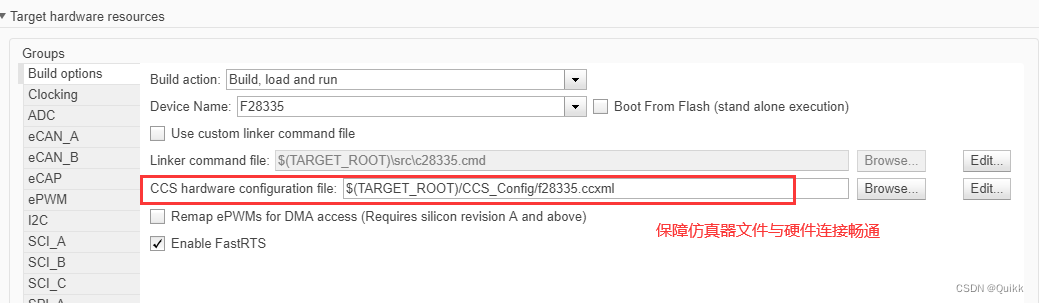

PIL The system composition needs to ensure the system connection :1) Bottom hardware download port and matlab Keep connected 2) Bottom hardware serial port and matlab Keep connected ; Build the hardware platform shown in the figure below

2.3 Model settings

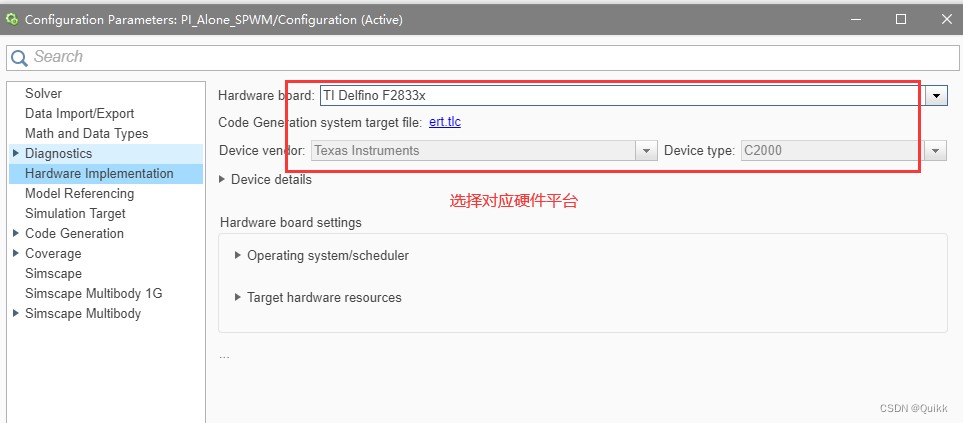

The model needs to be configured before setting MCU Code generation environment , Please refer to : Environment building

1) Create a processor in the loop model

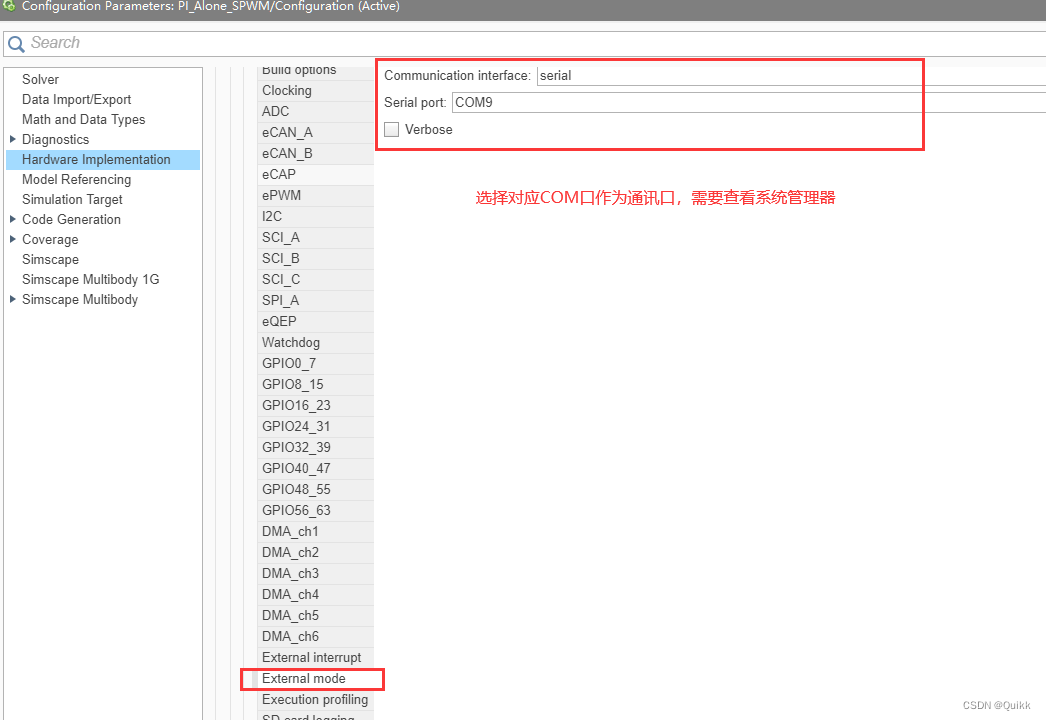

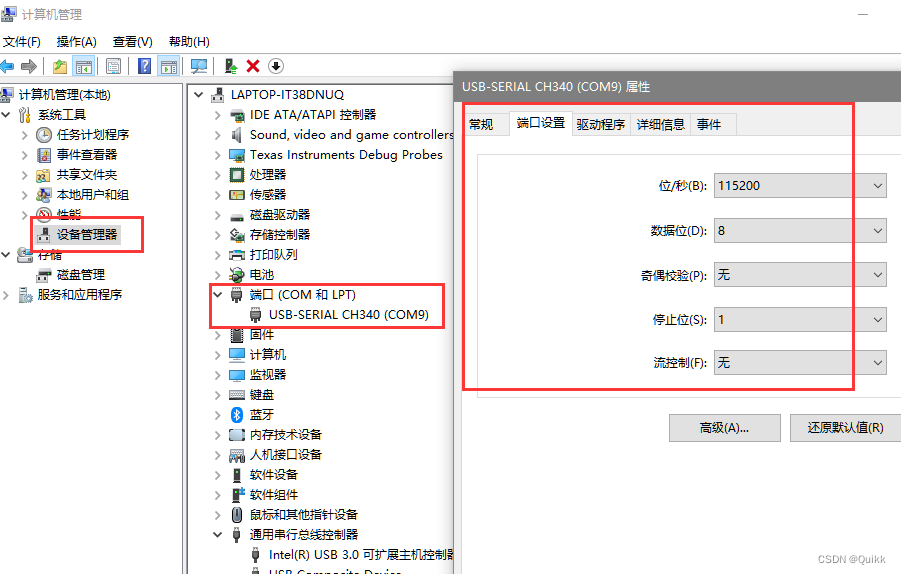

notes : Make sure that COM9, Baud rate , Etc , Ensure smooth communication , Prevent in ring test failure .

2.4 In loop test module generation

Package the control module into subsystems , Post generation PIL modular ; At this time, we need to slover step and Powergui Step size of It's also set to 10e-4; And set up Initial communication status , Enter the following code on the command line and execute , Be sure to pay attention to The serial port information corresponds to the information in the device management ;

setpref('MathWorks_Embedded_IDE_Link_PIL_Preferences','COMPort','COM9');

setpref('MathWorks_Embedded_IDE_Link_PIL_Preferences','BaudRate',115200);

setpref('MathWorks_Embedded_IDE_Link_PIL_Preferences','enableserial',true);

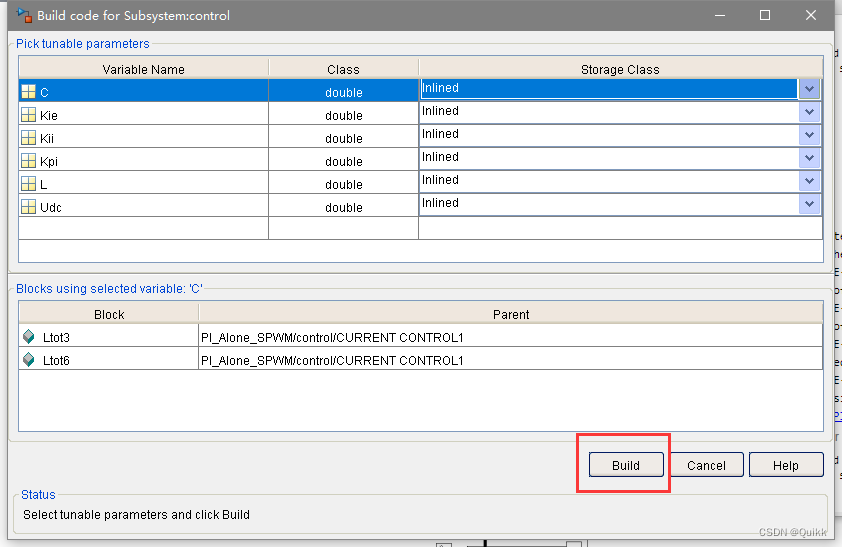

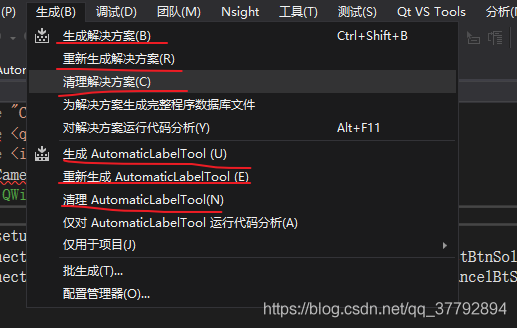

Pop up the dialog box and click build that will do ( We need to pay attention to ,MCU It can only run Single Type variable , The variables in the control module need to be changed to single type ):

Pop up the generated PIL Model , Copy the model to the original file .

2.5 Model test

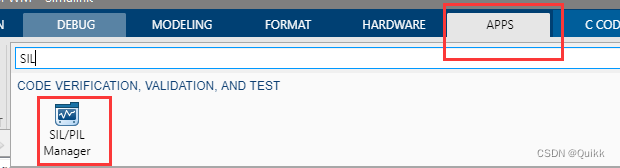

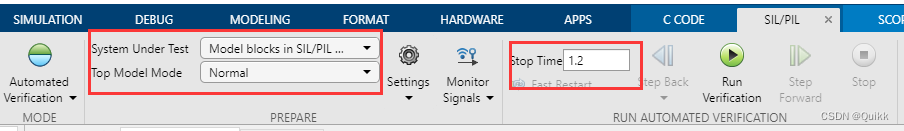

Get into SIL/PIL manager

Modify the simulation step size to 10e-6;

Set up PIL Parameters :

Click on run Verification

3 test result

After the test, get the above results , The result is divided into a software simulation result , One PIL In loop test results . At this point, you can compare the differences . compare You can also compare the differences between the two under the column .

Hardware :dsp28335

PC:simulink r2019b

Use serial port SCIA communicate

simulation model , I need to take it myself :PIL In loop model

The above process effectively realizes PIL test , The specific steps are generally shown in the figure , It should be noted that the generation PIL The test module must modify the model step size ( Change to controller execution step ). When testing , Be sure to change back to the original step .

边栏推荐

- VIM操作命令大全

- Idea view bytecode configuration

- Activity的创建和跳转

- 2837xd 代码生成——StateFlow(4)

- Chrome video download Plug-in – video downloader for Chrome

- 分布式锁的这三种实现方式,如何在效率和正确性之间选择?

- Probability is not yet. Look at statistical learning methods -- Chapter 4, naive Bayesian method

- Typora安装包分享

- The channel cannot be viewed when the queue manager is running

- Matplotlib swordsman - a stylist who can draw without tools and code

猜你喜欢

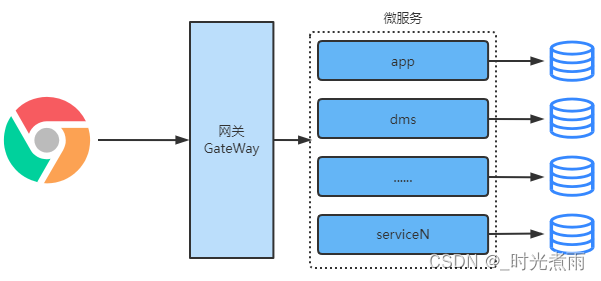

微服务实战|微服务网关Zuul入门与实战

图像识别-数据标注

In depth analysis of how the JVM executes Hello World

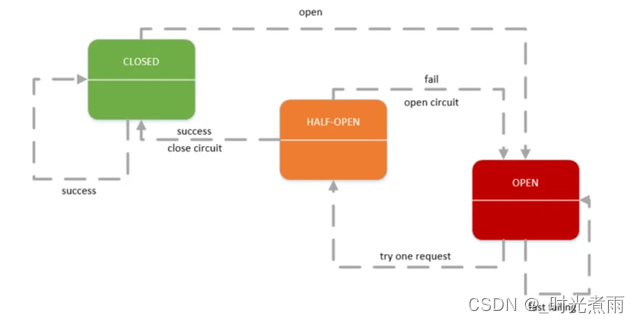

Microservice practice | fuse hytrix initial experience

每天睡前30分钟阅读Day6_Day6_Date_Calendar_LocalDate_TimeStamp_LocalTime

vs+qt 设置应用程序图标

企业级SaaS CRM实现

Insight into cloud native | microservices and microservice architecture

自定义Redis连接池

Don't look for it. All the necessary plug-ins for Chrome browser are here

随机推荐

自定义Redis连接池

Actual combat of microservices | discovery and invocation of original ecosystem implementation services

Mathematics in machine learning -- point estimation (I): basic knowledge

Learn combinelatest through a practical example

Discussion on improving development quality and reducing test bug rate

Say goodbye to 996. What are the necessary plug-ins in idea?

Number structure (C language) -- Chapter 4, compressed storage of matrices (Part 2)

Knife4j 2. Solution to the problem of file control without selection when uploading x version files

Chrome browser tag management plug-in – onetab

微服务实战|手把手教你开发负载均衡组件

Typeerror: X () got multiple values for argument 'y‘

每天睡觉前30分钟阅读_day3_Files

道阻且长,行则将至

Chrome browser plug-in fatkun installation and introduction

Difference between redis serialization genericjackson2jsonredisserializer and jackson2jsonredisserializer

Watermelon book -- Chapter 5 neural network

Microservice practice | fuse hytrix initial experience

Mysql 多列IN操作

Read Day5 30 minutes before going to bed every day_ All key values in the map, how to obtain all value values

Long summary (code with comments) number structure (C language) -- Chapter 4, string (Part 1)