当前位置:网站首页>Mpc5744p clock module

Mpc5744p clock module

2022-07-27 16:56:00 【Tritium】

MPC5744p

refMPC5744P-Reference Manual.pdf

overview

- MPC5744 from 16MHz Internal RC oscillator (IRCOSC) start-up , And in PLL Or take it as the backup clock in case of oscillator failure

- There are three ways to provide clock sources : External oscillator , External crystal oscillator , IRCOSC

- Then go through PLLs(PLL0&PLL1 or PLL0_PHI&PLL1_PHI) Generate internal clock

- Two clocks are connected XOSC and IRCOSC, Can be selected to drive system peripherals

- from PLL0 Output PHI1 Can be used as PLL1 The clock source of

- 7 A clock selector allows developers to choose PLL The reference clock of , Use an independent clock source to drive various system peripherals , Select clock source drive to generate off chip signal ; An additional clock selector is dedicated to the system clock

- Each module clock selector output has up to three frequency dividers , Allow more clock frequency granularity , Given a set of peripherals, the frequency division coefficient is as high as 64

- On the selected output of the clock divider CMU(Clock Monitor Units), Used to test clock integrity , Ensure that the frequency is maintained within the necessary operating limits

- if 5 individual CMU Any one of the detected clock signal problem , An interrupt or system reset will be generated , Depending on CMU Configuration of

The clock produces

- To ensure that the clock branches of different systems are synchronized , There is a frequency limit

- Startup time , IRCOSC As the default clock of the whole system , All system clock dividers are set to double frequency

PLL

- Provide dual... Of discrete system and peripheral clock PLL

- Prohibit after startup , Must be enabled by software

- PLL0: Lord PLL, Provide a non frequency modulated clock for the module , PLL1 The reference clock of

- Input : XOSC, IRCOSC, Bypass channel (EXTAL pin), from AUX Clock selector 3 choice

- Output : PHI, PHI1, After being selected PHI The output clock drives different peripherals and system clocks , PHI1 Output provides PLL One of the inputs to

- PLL1: FMPLL(Frequency Modulated)

- Input : XOSC, PLL0_PHI, Bypass channel (EXTAL pin), AUX Selectors 4 choice

- Output : PHI, Including decimal divider , Can be used for PLL Loop frequency division

XOSC External oscillator

- On chip PLL Provides a reference , Can be used as ADCs, SGEN, Motor control module , LFAST and PLL The reference of , System clock source

- Can be in any CLKOUT_pin Upper observation , For calibration IRCOSC The reference of

- The external oscillator allows a crystal oscillator / The external clock acts as MCU The reference of

- function :

- PLL0 and PLL1 The reference clock of

- CMU0 The reference clock of

- Choose directly from XOSC drive CAN and FlexRay Protocol clock

- Provide 8-44MHz Crystal input support

IRCOSC 16MHz Inside RC oscillator

- mcu There is one 16MHz Internal RC oscillator , Always enable , be used for PLLs The clock source of

- Used as a MC_RGM, FCCU, PIT, SWT, SIUL2 Input filtering , ADCs, SGEN, motor Control module , The clock source of the system clock

- IRCOSC Is the default system clock after reset

- Internal interface : The device has a special digital interface for IRCOSC, Fine tune the frequency , Read the temperature sensor , Voltage regulator , Setting of capacitor trimmer

- fine-tuning : IRCOSC Fine tuning is needed to match the accuracy requirements , After startup or destructive reset, it operates at an unadjusted frequency , The trim value determined by the factory test is stored in flash, Load on reset

Peripheral clock

LFAST clocking

- MPC5744p There is one LFAST Module to support high-speed device communication ,

- A single LFAST PLL need 10~20MHz The reference clock of , Support LFAST High speed operation ,

- For low speed LFAST operation , LFAST The module can directly use the reference clock

- LFAST need 20MHz The reference of , The clock source can be PLL0_PHI / XOSC / Input pin

FlexRay

- FlexRay Protocol clock from non FM Of PLL0_PHI The clock / XOSC

- If you use XOSC, Need one 40MHz Crystal oscillator

- If you use PLL0_PHI, You have to configure

MC_CGM_AC1_DC0Register to provide 80MHz- PLL The frequency must be XOSC Source 2 times , because PLL The duty cycle is unstable

- FlexRay The module of PLL Frequency division of , Provide a stable 50 Duty cycle ,40MHz The internal clock of

- When

FR_MCR[CLKSEL]Set up 1, The internal frequency divider is automatically enabled , Users cannot change it or treat it as XOSC Source

FlexCAN clocking

- CAN Clock from XOSC / PLL0_PHI The clock produces , PLL0_PHI The clock can be divided

- The frequency divider outputs (CAN_PLL_CLK) Drive one of the two inputs of a multiplexer

- Other inputs are provided by XOSC drive

Clock monitoring

- For all safety critical clocks , MCU Detect lost clock / Error frequency

- Every CMU Independent configuration , IRCOSC Used as a CMU The reference of

- These signals are connected inside the chip , But not through pins obtain

- IRCOSC It's all CMU The reference of , only CMU0 use IRCOSC measurement XOSC Is it too low , Also available XOSC To calibrate IRCOSC

- other CMUs Are configured independently

- XOSC monitor: If measured XOSC The frequency is below the limit , A flag is set , Interrupt generation

- IRCOSC monitor: With XOSC Fine tune for reference IRCOSC frequency

- System clock monitor: One CMU Assigned to monitor core frequencies and peripheral bridges , Motor control , ADC, SENTclocks

Clock lost

- PLL/XOSC loss: PLL Each unlock signal & XOSC The fault signal is FCCU monitor , When clock failure occurs , FCCU Configurable to generate short / Long reset / interrupt ( There is only unpredictable PLL Free clock provided ).

- No automatic clock switching , Users need to configure

- Therefore, it is strongly recommended to be PLL When used for system clock, interrupt response is not selected .

- When short / Long reset is selected , PLL, XOSC, MC_ME, MC_CGM Reset to initial state , The system clock ->IRCOSC

- IRCOSC loss: CMU0 monitor , When IRCOSC invalid , nothing FCCU Automatically triggered error condition , Its failure is catastrophic

- PLL loss: Always to PLL0CR[LOLIE] and PLL1CR[LOLIE] Write 1 To keep the unlock interrupt enabled

边栏推荐

- Interpretation of C basic syntax: summarize some commonly used but easily confused functions (i++ and ++i) in the program (bit field)

- The class declared by the scala object keyword directly calls methods and associated objects

- C语言之数组

- Servlet中文乱码setContentType设置无效

- Process control statement

- Json数据的格式使用

- Servlet Chinese garbled setcontenttype setting is invalid

- LNMP environment - deploy WordPress

- C语言之枚举和联合体

- C语言之动态内存分配

猜你喜欢

![[paper reading] single- and cross modality near duplicate image pairsdetection via spatial transformer compare](/img/33/8af12d58f4afeb807ebf9a90a2ea47.png)

[paper reading] single- and cross modality near duplicate image pairsdetection via spatial transformer compare

Insert pictures in word to maintain high DPI method

什么是jsp?

UML图介绍

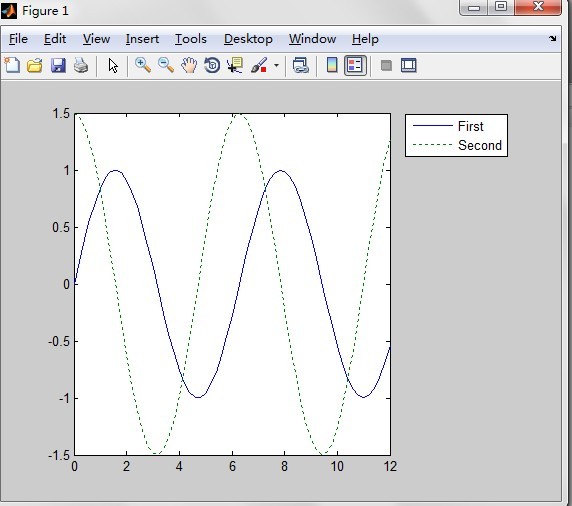

Matlab legend usage

D3.js create a cool arc

Simulation generate report

HowNet and Wanfang database download papers for free ----- several times faster than connecting to the school intranet (some schools Wanfang database does not support downloading)

【pytorch】|transforms.FiveCrop

清晰的认识Torchvision(思维导图版)

随机推荐

Servlet用Cookie实现用户上次登录时间

牛客题目——用两个栈实现队列、包含min函数的栈、有效括号序列

Quadratic programming based on osqp

Apache

合工大苍穹战队视觉组培训Day7——视觉,jetson naon与D435i

LNMP环境--部署wordpress

【pytorch】|transforms.FiveCrop

Simulation generate report

密码学系列之:PKI的证书格式表示X.509

mvc和mvp和mvvm的区别

Random number formula random

T5 learning

Fast Planner - detailed explanation of kinetic astar

Jerry's book can't find Bluetooth solutions [article]

C语言之指针进阶

Rotate the whole model in ADAMS

C language output string in reverse order

Bean: Model: Entity的区别

MPC_ ORCA

CDQ divide and conquer and whole dichotomy learning notes