当前位置:网站首页>LLVM TargetPassConfig

LLVM TargetPassConfig

2022-06-25 01:06:00 【Hui's Sutra Pavilion】

TargetPassConfig

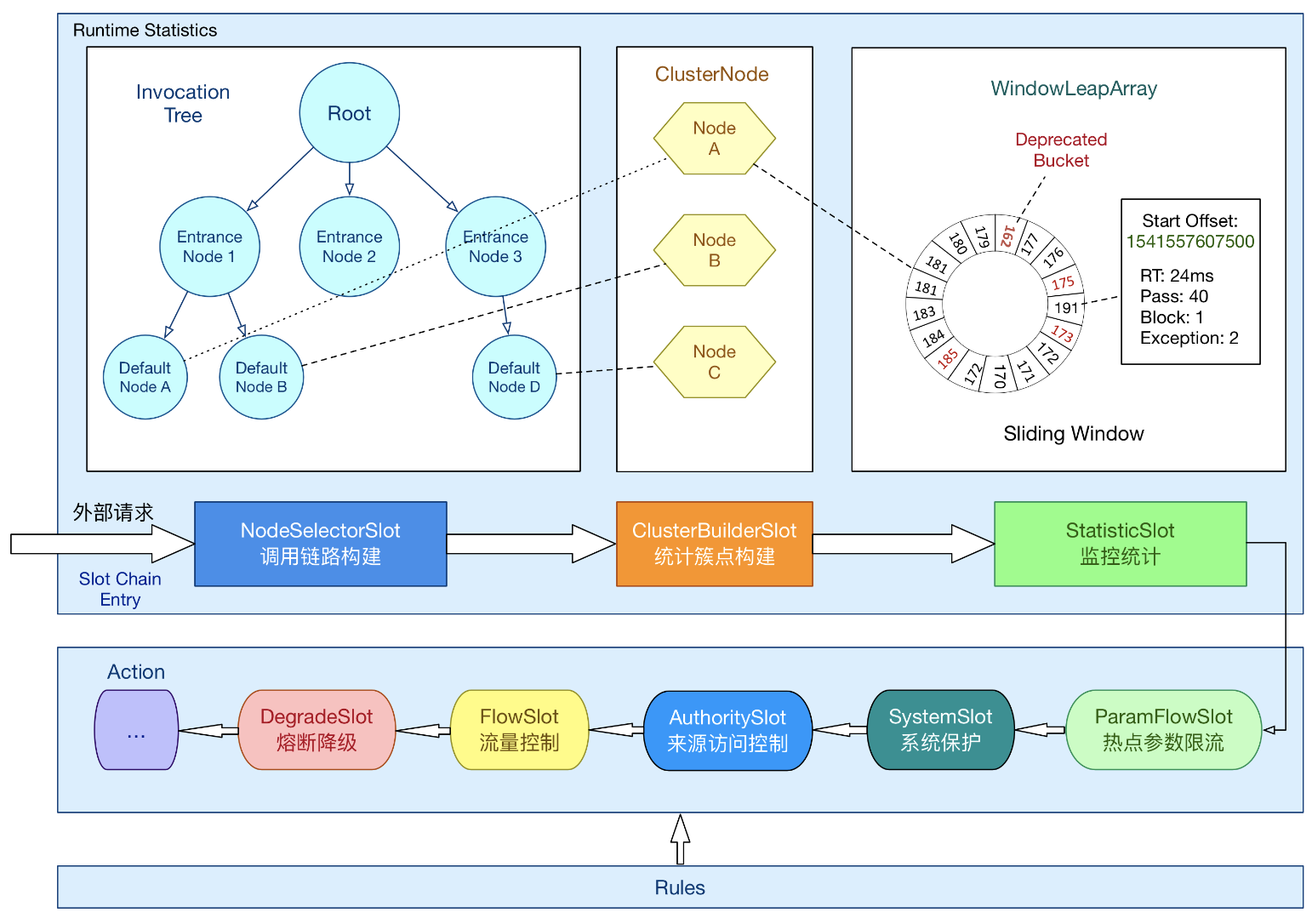

TargetPassConfig Class is LLVM Back end add pass entrance ,LLVM The framework divides the whole back end into instruction selection 、 Instruction scheduling , Register allocation, etc ,, Here's the picture :

Each of these phases contains one or more pass,LLVM One of the most important processes in the backend is compatibility and modularity , To add to these back ends pass Conduct management ,LLVM The back end encapsulates the interfaces for the above important stages , Each interface basically represents one Important stage , Every target You can add as many as you need pass,

TargetPassConfig The class for codegen Various interfaces are provided for each stage in , The main interfaces provided are as follows :

Interface | explain |

addISelPasses | Add all necessary from llvm IR Convert to generation MI Of pass |

addIRPasses | Add pair llvm IR->IR The optimization of the pass |

addPassesToHandleExceptions | Add various exceptions at lower levels pass, these pass Main treatment CodeGen Various exceptions generated in |

addCodeGenPrepare | stay LLVM IR Add... To this level CodeGen I've been preparing for pass, these pass At this time, only IR, So you need to addPassesToHandleExceptions Before adding |

addISelPrepare | Add some optimizations before instruction selection IR Of pass, This stage is also in IR Stage , Not converted to DAG, Main optimization IR |

addInstSelector | Add instruction selector selector And if necessary pass |

addIRTranslator | add to IR Convert to machine code related pass, When calling a relationship addIRTranslatoràaddInstSelector |

addMachinePasses | Add a set CodeGen Required by the standard pass |

addMachineSSAOptimization | SSA Optimization needs to add pass |

addPreRegAlloc/addPostRegAlloc | Before register allocation / You need to add pass |

addFastRegAlloc | To quickly allocate registers, you need to add pass |

addPassesToGenerateCode

addPassesToGenerateCode Function to add CodeGen Pass The main entrance :

/// addPassesToX helper drives creation and initialization of TargetPassConfig.

static TargetPassConfig *

addPassesToGenerateCode(LLVMTargetMachine &TM, PassManagerBase &PM,

bool DisableVerify,

MachineModuleInfoWrapperPass &MMIWP) {

// Targets may override createPassConfig to provide a target-specific

// subclass.

TargetPassConfig *PassConfig = TM.createPassConfig(PM);

// Set PassConfig options provided by TargetMachine.

PassConfig->setDisableVerify(DisableVerify);

PM.add(PassConfig);

PM.add(&MMIWP);

if (PassConfig->addISelPasses())

return nullptr;

PassConfig->addMachinePasses();

PassConfig->setInitialized();

return PassConfig;

}

- createPassConfig : according to PM Create the corresponding target Of TargetPassConfig , Every target Will be based on this class , Re implement the important interfaces in the phase to add unique pass, It doesn't affect the others target

- PassConfig->addISelPasses: Add what is required in the instruction selection phase pass The main entrance

- PassConfig->addMachinePasses(): Instructions from IR After converting to machine code , Added pass, Including register allocation , And machine code level optimization pass etc.

AMDGPU TargetPassConfig

When writing a new backend , An important content is to realize this target Add as needed pass, With AMDGPU For example TargetPassConfig The inheritance relationship is as follows :

- AMDGPUPassConfig: It's all AMDGPU The backend must be added pass

- GCNPassConfig and R600PassConfig They are aimed at GCN and R600 platform .

边栏推荐

- 热力图展示相关矩阵

- Working principle analysis of kubernetes architecture core components

- JSON file of China's provincial boundaries

- 2022 crane driver (limited to bridge crane) examination question bank simulated examination platform operation

- Danish Technical University pioneered the application of quantum computing to power flow modeling of energy system

- 【无标题】

- 移动安全工具-apktool

- QT (35) - operate excel qxlsx qaxobject

- 2021-11-07

- ros(25):rqt_ image_ View reports an error unable to load plugin for transport 'compressed', error string

猜你喜欢

【微服务|Sentinel】Sentinel快速入门|构建镜像|启动控制台

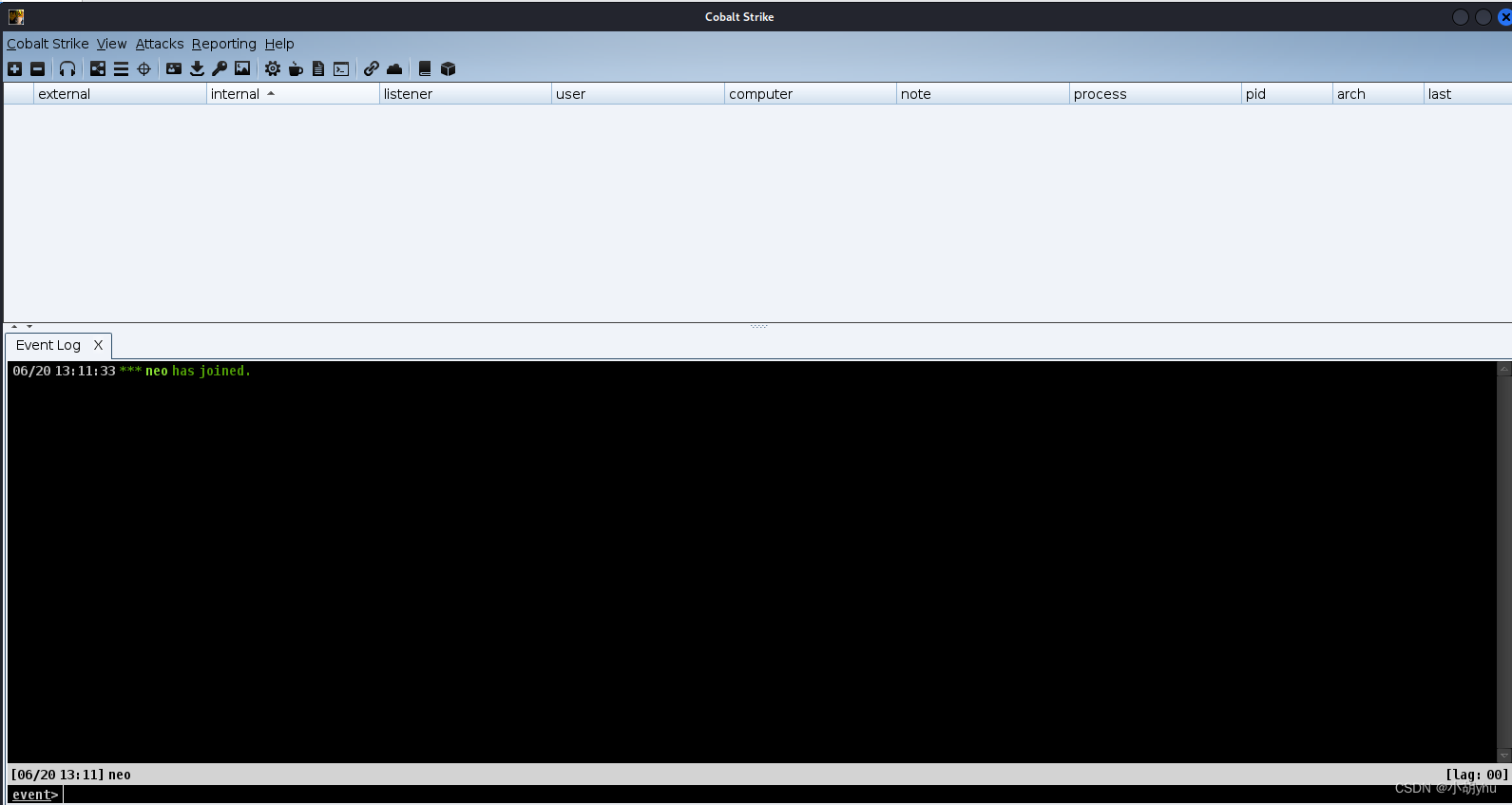

Cobalt Strike安装教程

2022熔化焊接与热切割复训题库模拟考试平台操作

Tiktok wallpaper applet source code

Simulation questions and answers of the latest national fire facility operator (senior fire facility operator) in 2022

QT (35) - operate excel qxlsx qaxobject

在企业级开发过程中我发现有位同事用select * from where 条件 for update

Single blind box removal, social blind box and friend blind box program source code

最新QQ微信域名防红PHP程序源码+强制跳转打开

打卡smart精灵#1,品牌不缺吸引力,产品本身实力如何?

随机推荐

2021-11-05

activity生命周期

Text editor of QT project practice ---------- episode 8

Custom control - round dot progress bar (imitating one key acceleration in security guard)

The interview questions and answers for the high-frequency software test of Dachang help you prepare for the golden nine silver ten

Scala IO read by character

ros(25):rqt_image_view报错Unable to load plugin for transport ‘compressed‘, error string

Mobile security tool jar

Scala trait construction mechanism

2022年起重机司机(限桥式起重机)考试题库模拟考试平台操作

打卡smart精灵#1,品牌不缺吸引力,产品本身实力如何?

bindservice方法实现音乐播放暂停

使用 Loki 微服务模式部署生产集群

我想问一下兴业证券怎么开户?通过链接办理股票开户安全吗

Distinguish between i++ and ++i seconds

最新QQ微信域名防红PHP程序源码+强制跳转打开

QT (36) -rapidjson parsing nested JSON

Realization of MNIST handwritten numeral recognition

Text editor for QT project practice -- Episode 9

[micro service sentinel] real time monitoring | RT | throughput | concurrency | QPS