当前位置:网站首页>5. PCIe official example

5. PCIe official example

2022-08-05 00:44:00 【jjinl】

官方提供3个使用PCIe的例子.第一个比较简单,I left out the instantiation parameter,整个文件结构如下:

module top_basic (/*AUTOARG*/

// Outputs

hdoutp, hdoutn, pll_lk, poll, l0, dl_up, usr0, usr1, usr2, usr3,

na_pll_lk, na_poll, na_l0, na_dl_up, na_usr0, na_usr1, na_usr2,

na_usr3, led_out, dp, TP,

// Inputs

rstn, FLIP_LANES, LED_INV, refclkp, refclkn, hdinp, hdinn,

dip_switch

);

....

led_status led (....); // Templated

pcie2_core pcie (..... );

ip_rx_crpr #(.c_DATA_WIDTH (c_DATA_WIDTH)) cr (....);

ip_crpr_arb crarb (.....); // Templated

UR_gen #(.c_DATA_WIDTH (c_DATA_WIDTH)) ur (.......); // Templated

ip_tx_arbiter #(.c_DATA_WIDTH (c_DATA_WIDTH)) tx_arb (.....);

wb_tlc #(.c_DATA_WIDTH(c_DATA_WIDTH)) wb_tlc (.....); // Templated

wb_arb #(.c_DATA_WIDTH(c_DATA_WIDTH),

.S0_BASE (32'h0000),

.S1_BASE (32'h4000),

.S2_BASE (32'h1000),

.S3_BASE (32'h5000))

wb_arb (.....);

wbs_gpio gpio (......); // Templated

wbs_32kebr #(.c_DATA_WIDTH(c_DATA_WIDTH),

.init_file("none"))

ebr (......); // Templated

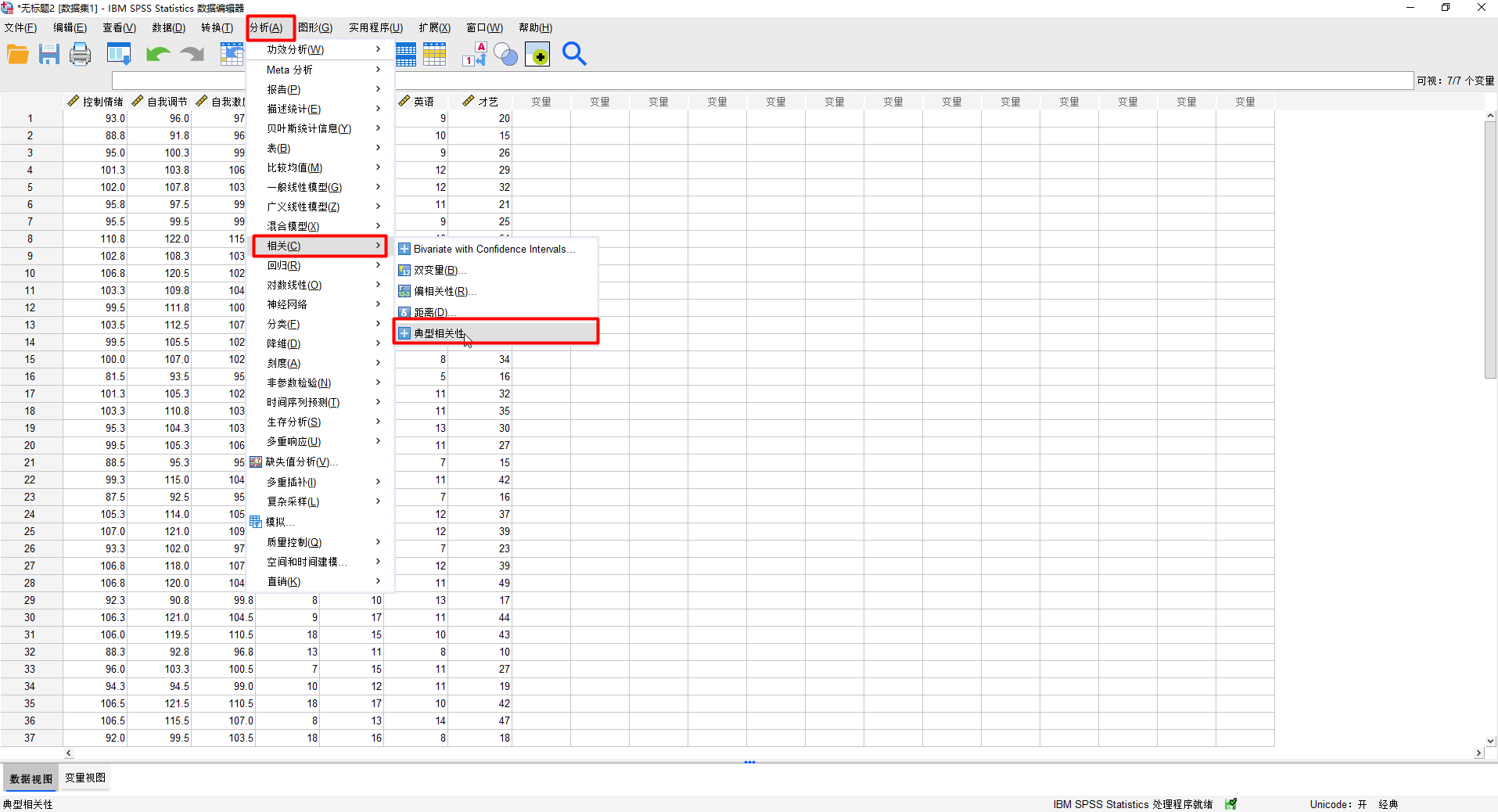

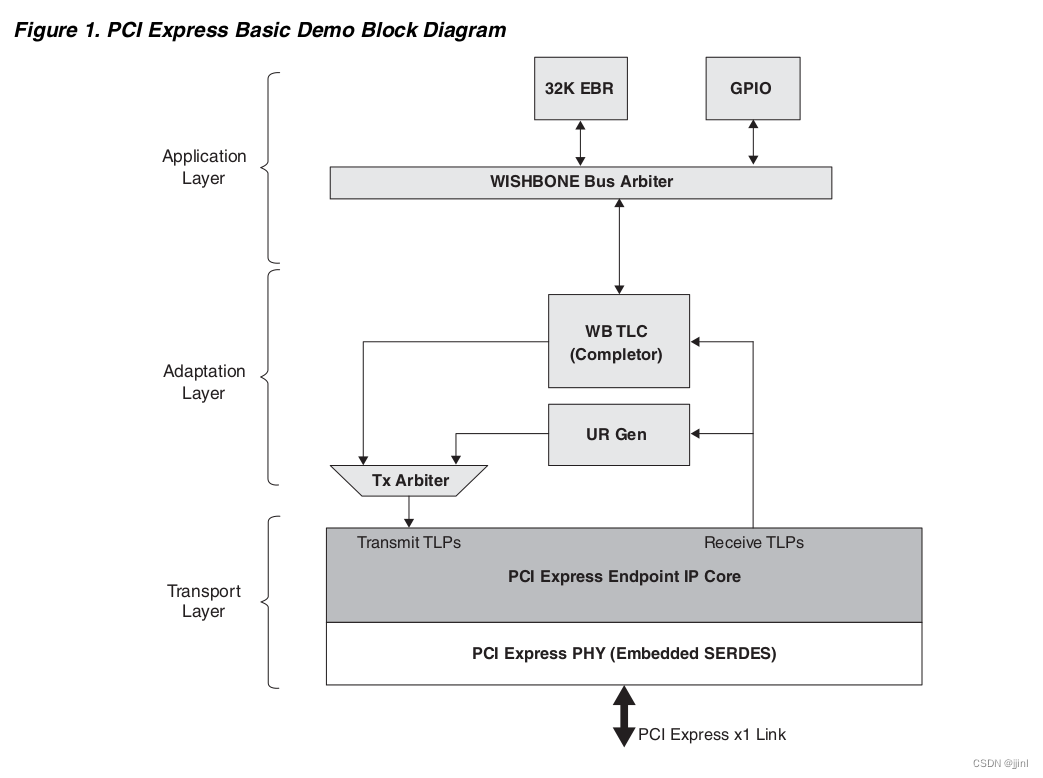

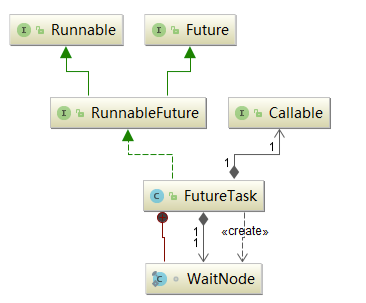

endmoduleThere are several calls in this fileIP,分别是led_status、pcie2_core、ip_rx_crpr、ip_crpr_arb、UR_gen、ip_tx_arbiter、wb_tlc、wb_arb、wbs_gpio、wbs_32kebr.The connection diagram is as follows:

上图中PCIe发来的TLP包送到UR Gen模块和WB TLC模块,WB TLCReceive packages that interest you,并转换为wishbone总线接口,Generate read and write timing towishboneBus Arbitration Modulewishbone bus arbiter,The arbiter operates the corresponding data according to the address of the read and write datawishbone从设备,The data returned from the device passes throughwb tlc打包成tlp包,再通过tx arbiter发送到PCIe EP,Then upload to the host computer.UR GenModules are mainly dealt with herewb_tlcModules are not interested in packages,Reply to the completion message and identify the unsupportedTLP包.

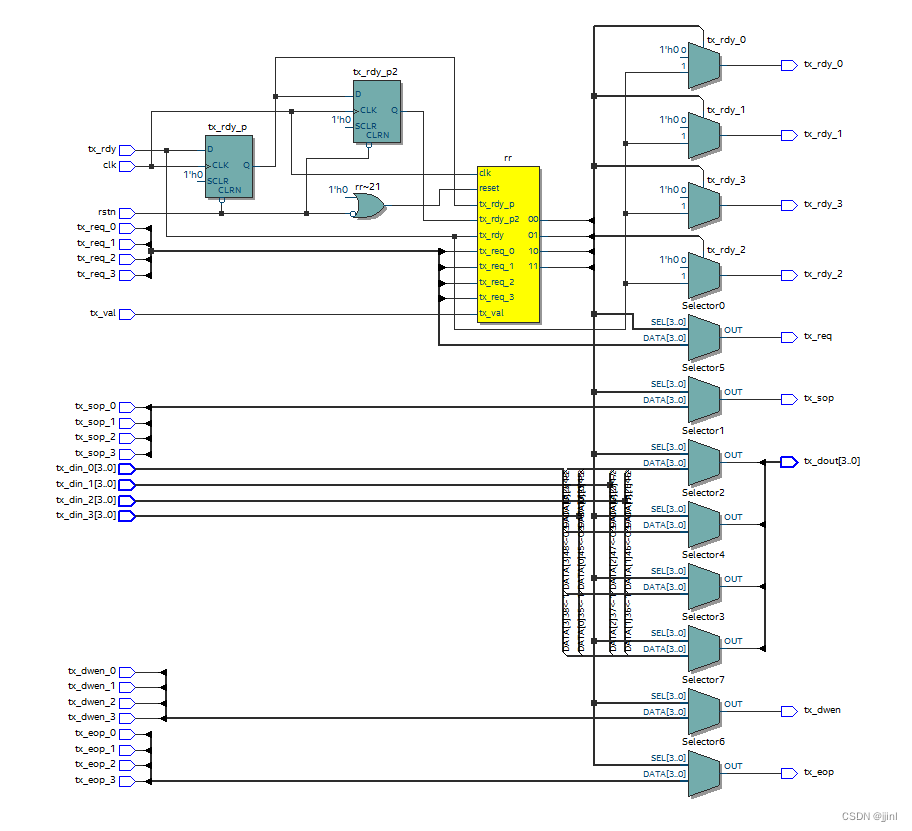

Pick a simple file first,打开Tx Arbiter文件ip_tx_arbiter.v,内容如下:

// $Id: ip_tx_arbiter.v,v 1.1.1.1 2008/07/01 17:34:22 jfreed Exp $

module ip_tx_arbiter #(parameter c_DATA_WIDTH = 64) (/*AUTOARG*/

// Outputs

tx_rdy_0, tx_rdy_1, tx_rdy_2, tx_rdy_3, tx_req, tx_dout, tx_sop,

tx_eop, tx_dwen,

// Inputs

clk, rstn, tx_val, tx_req_0, tx_din_0, tx_sop_0, tx_eop_0,

tx_dwen_0, tx_req_1, tx_din_1, tx_sop_1, tx_eop_1, tx_dwen_1,

tx_req_2, tx_din_2, tx_sop_2, tx_eop_2, tx_dwen_2, tx_req_3,

tx_din_3, tx_sop_3, tx_eop_3, tx_dwen_3, tx_rdy

);

input clk;

input rstn;

input tx_val;

input tx_req_0;

input [c_DATA_WIDTH-1:0] tx_din_0;

input tx_sop_0;

input tx_eop_0;

input tx_dwen_0;

output tx_rdy_0;

input tx_req_1;

input [c_DATA_WIDTH-1:0] tx_din_1;

input tx_sop_1;

input tx_eop_1;

input tx_dwen_1;

output tx_rdy_1;

input tx_req_2;

input [c_DATA_WIDTH-1:0] tx_din_2;

input tx_sop_2;

input tx_eop_2;

input tx_dwen_2;

output tx_rdy_2;

input tx_req_3;

input [c_DATA_WIDTH-1:0] tx_din_3;

input tx_sop_3;

input tx_eop_3;

input tx_dwen_3;

output tx_rdy_3;

output tx_req;

output [c_DATA_WIDTH-1:0] tx_dout;

output tx_sop;

output tx_eop;

output tx_dwen;

input tx_rdy;

reg tx_req;

reg [c_DATA_WIDTH-1:0] tx_dout;

reg tx_sop;

reg tx_eop;

reg tx_dwen;

reg tx_rdy_0;

reg tx_rdy_1;

reg tx_rdy_2;

reg tx_rdy_3;

reg [1:0] rr;

reg tx_rdy_p;

reg tx_rdy_p2;

always @(/*AUTOSENSE*/rr or tx_din_0 or tx_din_1 or tx_din_2

or tx_din_3 or tx_dwen_0 or tx_dwen_1 or tx_dwen_2

or tx_dwen_3 or tx_eop_0 or tx_eop_1 or tx_eop_2

or tx_eop_3 or tx_rdy or tx_req_0 or tx_req_1 or tx_req_2

or tx_req_3 or tx_sop_0 or tx_sop_1 or tx_sop_2

or tx_sop_3)

begin

case (rr)

2'b00: begin // Service 0

tx_req <= tx_req_0;

tx_dout <= tx_din_0;

tx_sop <= tx_sop_0;

tx_eop <= tx_eop_0;

tx_dwen <= tx_dwen_0;

tx_rdy_0 <= tx_rdy;

tx_rdy_3 <= 1'b0;

tx_rdy_2 <= 1'b0;

tx_rdy_1 <= 1'b0;

end

2'b01: begin // Service 1

tx_req <= tx_req_1;

tx_dout <= tx_din_1;

tx_sop <= tx_sop_1;

tx_eop <= tx_eop_1;

tx_dwen <= tx_dwen_1;

tx_rdy_1 <= tx_rdy;

tx_rdy_3 <= 1'b0;

tx_rdy_2 <= 1'b0;

tx_rdy_0 <= 1'b0;

end

2'b10: begin // Service 2

tx_req <= tx_req_2;

tx_dout <= tx_din_2;

tx_sop <= tx_sop_2;

tx_eop <= tx_eop_2;

tx_dwen <= tx_dwen_2;

tx_rdy_2 <= tx_rdy;

tx_rdy_3 <= 1'b0;

tx_rdy_1 <= 1'b0;

tx_rdy_0 <= 1'b0;

end

2'b11: begin // Service 3

tx_req <= tx_req_3;

tx_dout <= tx_din_3;

tx_sop <= tx_sop_3;

tx_eop <= tx_eop_3;

tx_dwen <= tx_dwen_3;

tx_rdy_3 <= tx_rdy;

tx_rdy_2 <= 1'b0;

tx_rdy_1 <= 1'b0;

tx_rdy_0 <= 1'b0;

end

default: begin

end

endcase

end // always @ (...

// mux control

always @(posedge clk or negedge rstn)

begin

if (~rstn) begin

rr <= 2'b00;

tx_rdy_p <= 1'b0;

tx_rdy_p2 <= 1'b0;

end

else begin

tx_rdy_p <= tx_rdy; // use pipe of tx_rdy to account for getting the tx_end through

tx_rdy_p2 <= tx_rdy_p;

if (tx_val && ~tx_rdy_p2 && ~tx_rdy_p && ~tx_rdy) begin

if (tx_req_0 && ~tx_req) rr <= 2'b00;

else if (tx_req_1 && ~tx_req) rr <= 2'b01;

else if (tx_req_2 && ~tx_req) rr <= 2'b10;

else if (tx_req_3 && ~tx_req) rr <= 2'b11;

end

end // else: !if(~rstn)

end // always @ (posedge clk or negedge rstn)

endmodule

这个文件实现4Select an output function

Originally wanted to use the synthesis tool 查看RTL,生成的RTL太复杂,I put the bus width from 64改为4后生成RTL视图如下:

边栏推荐

- Software testing interview questions: How many types of software are there?

- Lattice PCIe 学习 1

- 软件测试面试题:BIOS, Fat, IDE, Sata, SCSI, Ntfs windows NT?

- 【Unity编译器扩展之进度条】

- 软件测试面试题:一套完整的测试应该由哪些阶段组成?

- Matlab uses plotting method for data simulation and simulation

- 2022 Hangzhou Electric Power Multi-School Session 3 Question B Boss Rush

- Software testing interview questions: What stages should a complete set of tests consist of?

- The principle of NMS and its code realization

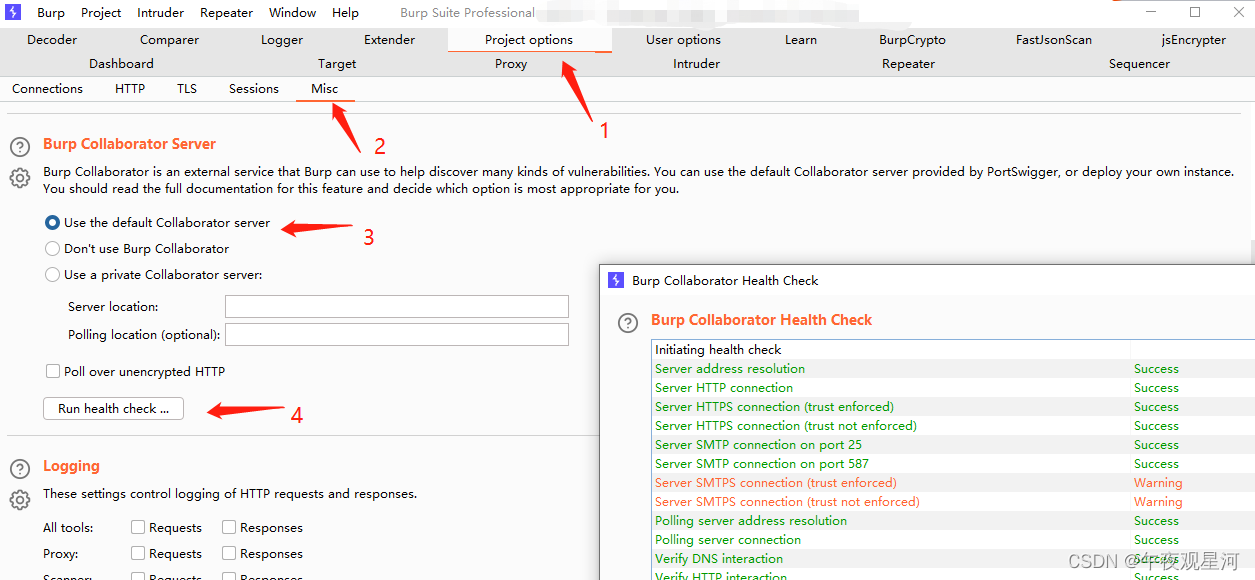

- 《WEB安全渗透测试》(28)Burp Collaborator-dnslog外带技术

猜你喜欢

随机推荐

Software Testing Interview Questions: What do you think about software process improvement? Is there something that needs improvement in the enterprise you have worked for? What do you expect the idea

Software Testing Interview Questions: What is Software Testing?The purpose and principle of software testing?

About I double-checked and reviewed the About staff page, returning an industry question

僵尸进程和孤儿进程

2022 The Third J Question Journey

Lattice PCIe 学习 1

SV class virtual method of polymorphism

EL定时刷新页面中的皕杰报表实例

tiup status

2022牛客多校第三场 A Ancestor

leetcode: 267. Palindromic permutations II

2022杭电多校 第三场 B题 Boss Rush

QSunSync Qiniu cloud file synchronization tool, batch upload

Raw and scan of gorm

tensor.nozero(), mask, [mask]

2022 Hangzhou Electric Multi-School 1004 Ball

leetcode:267. 回文排列 II

oracle创建用户

canvas Gaussian blur effect

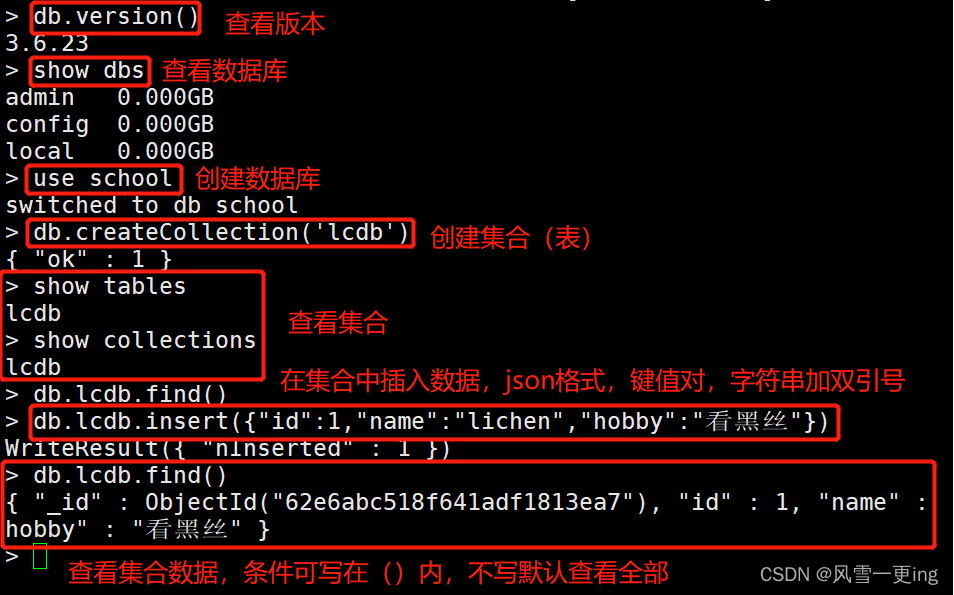

MongoDB construction and basic operations

](/img/4d/2d81dc75433c23c5ba6b31453396f0.png)