当前位置:网站首页>Adder - Notes

Adder - Notes

2022-06-28 03:51:00 【Jiangnan small workshop】

adder

- An adder is a unit that performs the addition function , It has two or three data input ports and two output ports .

- For binary addition operation , Such as

0+0=0,0+1=1,1+1=0, Carry is 1. - Depending on the number of input ports , Adders are divided into half adders and full adders .

Half adder

- Two input ports , Addend and addend ; Two output ports , Carry and result .

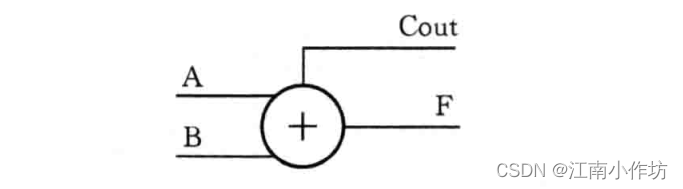

- Common symbols

- Logical expression F = A ⋅ B ˉ + B ⋅ A ˉ = A ⊕ B F=A\cdot\bar{B}+B\cdot\bar{A}=A\oplus B F=A⋅Bˉ+B⋅Aˉ=A⊕B C o u n t = A ⋅ B Count=A\cdot B Count=A⋅B

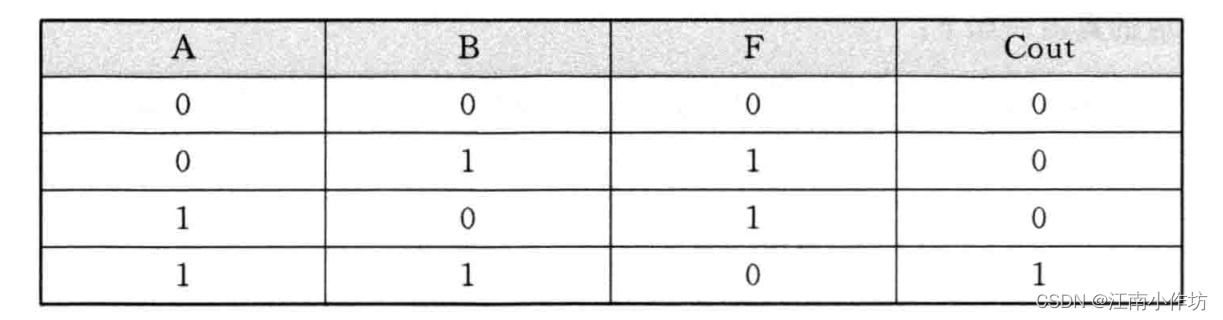

- Corresponding truth table

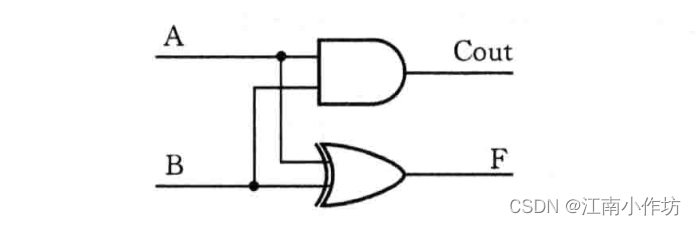

- You can find , F F F And A . B A.B A.B The relation of is XOR gate , C o u n t Count Count And A . B A.B A.B The relationship between and gate . Therefore, a semi adder can be composed of an XOR gate and an and gate .

- Verilog describe

module half_adder( input A, input B, output F, output Cout ); assign F = A ^ B; assign Cout = A & B; endmodule - RTL View

Full adder

On the basis of half adder , Consider the carry of low order operations , So the full adder has three input ports .

Logical expression F = A ⊕ B ⊕ C i n F=A\oplus B\oplus Cin F=A⊕B⊕Cin C o u t = A ⋅ B + C i n ( A ⊕ B ) Cout = A\cdot B+Cin(A\oplus B) Cout=A⋅B+Cin(A⊕B)

Corresponding truth table

Verilog grammar

module full_adder( input A, input B, input Cin, output F, output Cout ); assign F = A^B^Cin; assign Cout = A&B|(Cin&(A^B)); endmoduleRTL View

Another method is to realize full adder , Using two half adders

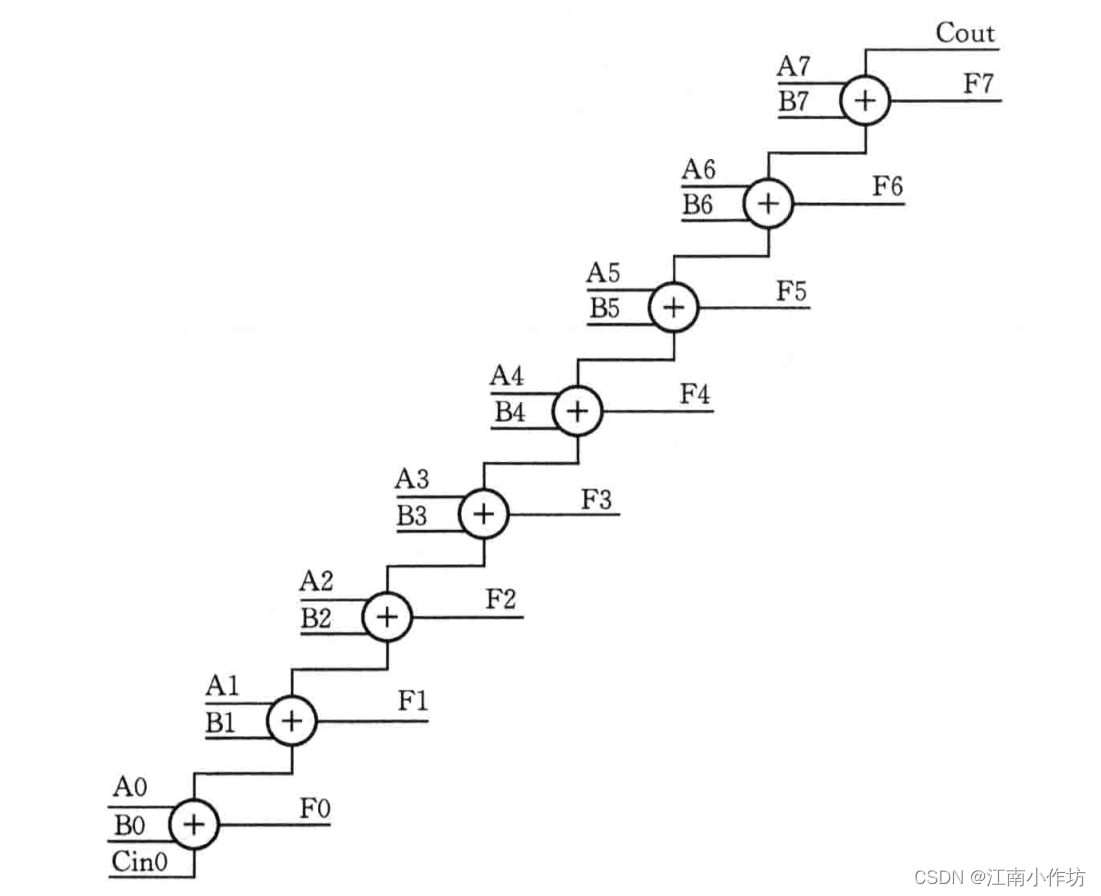

Since the full adder takes into account the carry of the low order operation , Thus, we can easily add multi bit data by cascading multiple full adders , Such as 8 Bit data

This cascade method is also called traveling wave carry adder , If there is carry , Like a ripple from low to high . This adder , Because each full adder needs to wait for the carry output of its previous full adder to complete the calculation , So it takes a long time 、 Low efficiency . In order to improve the time efficiency of addition , Carry select adder and carry ahead adder are introduced .

HDLBits There is a question about adder above : Give a 16 Bit adder add16, To design a 32 Bit adders .

This 16 Bit adders , It can be formed by cascading traveling wave carry , Its internal structure can be free from entanglement , On how to form 32 Bit adder for understanding .

Verilog Realization

module top_module( input [31:0] a, input [31:0] b, output [31:0] sum ): // Define the internal connection line wire [15:0] a_1, a_2; wire [15:0] b_1, b_2; wire [15:0] sum_1, sum_2; wire cin_1, cin_2, cout_1; // Be careful , Here you can see that the following carry has no output , therefore , Can not define . // Connect the cable to the port data assign cin_1 = 0; assign a_1 = a[15:0]; assign a_2 = a[31:16]; assign b_1 = b[15:0]; assign b_2 = b[31:16]; assign sum = { sum_2,sum_1}; // call add16 modular add16 add16_inst_1(.a(a_1),.b(b_1),.cin(cin_1),.cout(cout_1)); add16 add16_inst_2(.a(a_2),.b(b_2),.cin(cin_2)); endmoduleAs mentioned earlier , For addition of multi bit bus data , If traveling wave carry is used , It has a long carry chain and key path , Time consuming , Low efficiency . Therefore, several adders based on the carry derivation of traveling wave are introduced .

Carry select adder

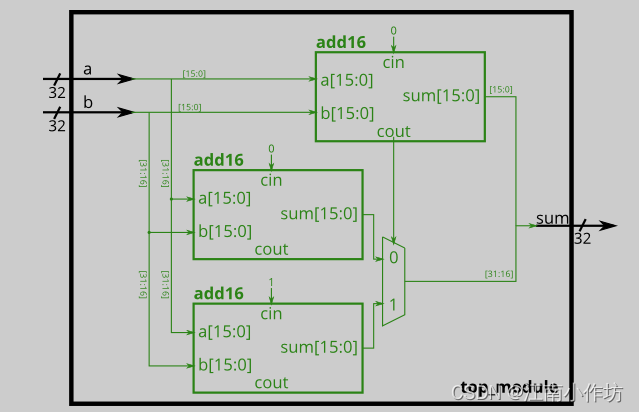

- I have learned about multiplexers , Can multiplexers be added to improve the efficiency of traveling wave carry ? Take the above as an example , Give a 16 Bit adder add16, To design a 32 Bit adders .

- By means of carry selection , The block diagram is as follows

- Use 3 individual 16 Bit adders : Build two high 16 Bit adders , A carry to 0, A carry to 1. Through low 16 The carry signal of the bit adder is used to select which adder value to output .

- Verilog Realization

- Simulation results

- Advantages and disadvantages :

- High and low bits can be operated at the same time , Reduce time ;

- Large circuit area ( Pictured above , Use more than one adder and selector );

边栏推荐

猜你喜欢

applicationContext.getBeansOfType 获取一个接口下所有实现类 执行方法或者获取实现类对象等 操作应用场景学习总结

门级建模—学习笔记

django. core. exceptions. ImproperlyConfigured: mysqlclient 1.3.13 or newer is required; you have 0.9.3

A pit filling trip based on LNMP to build a personal website

How does the open-ended Hall current sensor help the transformation of DC power distribution?

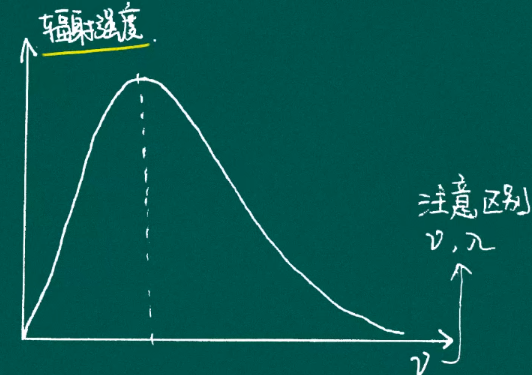

A Preliminary Study of Blackbody radiation

Anaconda command usage

Solution to not displaying logcat logs during debugging of glory V8 real machine

数据库系列之InnoDB中在线DDL实现机制

云应用、服务的“5层”架构

随机推荐

Cannot edit in read-only editor if it appears in vscode

What is the core problem to be solved in the East and West?

Unity C# 网络学习(十一)——自定义协议生成工具

使用信号分析器

How the uni app automatically switches the requested address according to the environment

云应用、服务的“5层”架构

__ getitem__ And__ setitem__

小程序输入框闪动?

电学基础知识整理(一)

《Go题库·12》slice和array区别?

A pit filling trip based on LNMP to build a personal website

Research and arrangement of electronic map coordinate system

"Five layer" architecture of cloud applications and services

小程序的防抖节流怎么写?

第14章 AC-DC电源前级电路 笔记一

Circular sliding auto adsorption UI tool that monkeys can use

Huawei equipment WLAN basic service configuration command

Resource management, high availability and automation (medium)

Paging query optimization in MySQL of database Series

Go 数据类型篇(四)之浮点型与复数类型