当前位置:网站首页>FPGA state machine

FPGA state machine

2022-06-10 19:56:00 【Tarbet】

FPGA State machine

One 、 State machine implementation

State machine : Implement a test process , This process includes starting the preparation state 、 Start the test 、 Stop test 、 Query test results 、 Display test results 、 After the test, return to initialization 6 Status ; Use time to control the process ,90 Complete the process in seconds

Describe the state jump time

- State machine state

- s0: Ready to go

- s1: Start state

- s2: Stop state

- s3: Query test results

- s4: Display test results

- s5: Return to the initial state after the test

- Staged jump

- s0 -> s1 The first 1s Jump to s1

- s1 -> s2 The first 25s Jump to s2

- s2 -> s3 The first 55s Jump to s3

- s3 -> s4 The first 60s Jump to s4

- s4 -> s5 The first 75s Jump to s5

- s5 -> s0 The first 90s Jump back to the initial state

- State machine state

coded .

module fsm(

input clk,

input rst_n,

output result

);

reg[5:0] state;

reg[27:0] ctn;

parameter max_time=28'd49_999_999;

wire[63:0] timer;

parameter s0 = 6'b100000;

parameter s1 = 6'b010000;

parameter s2 = 6'b001000;

parameter s3 = 6'b000100;

parameter s4 = 6'b000010;

parameter s5 = 6'b000001;

// Counter

[email protected](posedge clk or negedge rst_n)begin

if(!rst_n)begin

ctn <= 28'd0;

end

else if(ctn == max_time)begin

ctn <= 28'd0;

end

else ctn <= ctn +1'b1;

end

always @(posedge clk or negedge rst_n)begin

if(rst_n)begin

state <= s0;

end

else

case(state)

s0:begin

if(timer == 1)

state <= s1;

else state <= s0;

end

s1:begin

if(timer == 25)

state <= s2;

else state <= state;

end

s2:begin

if(timer == 55)

state <= s3;

else state <= state;

end

s3:begin

if(timer == 60)

state <= s4;

else state <= state;

end

s4:begin

if(timer == 75)

state <= s5;

else state <= state;

end

s5:begin

if(timer == 90)

state <= s0;

else state <= state;

end

default:sr=state <= s0;

endcase

end

endmodule

Two 、 testing 10010 strand

- Draw a picture that can detect 10010 State diagram of string

- verilog Programming to realize

module Ce_Top(

input clk,

input rst_n,

input data,

output result

);

reg result_r;

reg[4:0] state;

parameter IDLE = 5'b10000;

parameter S1 = 5'b01000;

parameter S10 = 5'b00100;

parameter S100 = 5'b00010;

parameter S1001= 5'b00001;

[email protected](posedge clk or negedge rst_n)begin

if(!rst_n)begin

state <= IDLE;

result_r <= 1'b0;

end

else

case(state)

IDLE: begin

if(data==0)begin

state <= IDLE;

result_r <= 0;

end

else begin

state <= S1;

result_r <= 0;

end

end

S1:begin

if(data ==0)begin

state <= S10;

result_r <= 0;

end

else begin

state <=S1;

result_r <= 0;

end

end

S10:begin

if(data ==0)begin

state <= S100;

result_r <= 0;

end

else begin

state <=S1;

result_r <= 0;

end

end

S100:begin

if(data==0)begin

state <= IDLE;

result_r <= 0;

end

else begin

state <= S1001;

result_r <= 0;

end

end

S1001:begin

if(data==0)begin

state <= IDLE;

result_r <= 1;

end

else begin

state <= S1;

result_r <= 0;

end

end

default: state <= 5'bx;

endcase

end

assign result =result_r;

endmodule

3、 ... and 、 summary

The main experiment jumps the state of the experiment through the state machine , Enter different logical sequences , In the code is online, only ideas are written , No board verification test .

边栏推荐

- Apicloud visual development - one click generation of professional source code

- Trilogy to solve the problem of playing chess first and then

- APICloud可视化开发新手图文教程

- Bit operation topic

- 2022.05.29 (lc_6078_rearranges characters to form target string)

- 面试中经常问到的几个问题,快来看看能答对几道吧

- 2022.05.27 (lc_647_palindrome substring)

- How to add aggregation hotspots in VR panorama? How to add a content module?

- C (pointer 02)

- 一文带你了解J.U.C的FutureTask、Fork/Join框架和BlockingQueue

猜你喜欢

Go language learning notes - cross domain configuration, global exception capture | web framework gin (IV)

专项测试之「 性能测试」总结

【C语言进阶】指针的进阶【上篇】

![[6.4-6.10] wonderful review of Blog](/img/66/0cfc97bf4bc0c2b6e66c0419690ce5.png)

[6.4-6.10] wonderful review of Blog

Looking for a room in the graduation season of college students, VR panoramic viewing helps you screen Online

如何在VR全景作品中添加独立热点?

My first work: tensorflow2 x

It is forbidden to throw away rotten software. A guide for software test engineers to advance from elementary level to advanced level will help you promote all the way

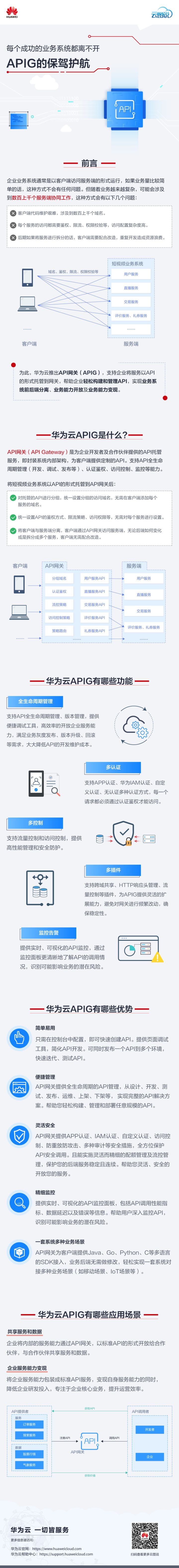

Yuntu says that every successful business system cannot be separated from apig

How to increase the monthly salary of software testing from 10K to 30K? Only automated testing can do it

随机推荐

Routine solution - the problem of horse walking on the chessboard

【C语言进阶】指针的进阶【上篇】

Before we learn about high-performance computing, let's take a look at its history

China pufuteng hotels and resorts launched new spa products to celebrate the global health day on June 11

2022.05.26 (lc_1143_longest common subsequence)

How do big factories write data analysis reports?

Writing technical articles is a fortune for the future

618大促将至,用AI挖掘差评,零代码实现亿级评论观点情感分析

【6.4-6.10】博客精彩回顾

【 Web 】 page d'accueil personnelle 】 Programme d'études 】 albums de photos 】 babillard d'information 】

Tencent libco collaboration open source library source code analysis full series summary blog

Source code analysis and practical testing openfeign load balancing

Complete knapsack problem and optimization tips

frp reverse proxy

基于改进SEIR模型分析上海疫情

深入理解LightGBM

Mongodb unique index

Only three steps are needed to learn how to use low code thingjs to connect with Sen data Dix data

2022 software test interview strategy for the strongest version of fresh students to help you get directly to the big factory

It is forbidden to throw away rotten software. A guide for software test engineers to advance from elementary level to advanced level will help you promote all the way