当前位置:网站首页>Section VI UART of zynq

Section VI UART of zynq

2022-06-28 07:35:00 【youbin2013】

ZYNQ Of UART

1 UART Characteristics

ZYNQ The serial port module is a full duplex asynchronous receiver and transmitter , Support a wide range of software programmable modules , Support programming to configure baud rate and data format , At the same time, it provides automatic parity check and error detection scheme , Besides , Also for APU Provides receive and send FIFO.

ZYNQ There are two UART device , It has the following characteristics :

- Programmable baud rate transmitter ;

- 64 Bytes received and sent FIFO;

- Data bits 6,7 perhaps 8 A bit ;

- p. , accidentally , Space , Marked or not verified ;

- 1,1.5 perhaps 2 Stop bits ;

- Support verification , Frame and overrun error detection ;

- Support automatic response , Local loop and remote loop channel modes ;

- Support interrupt generation ;

- stay EMIO On , A modem can be used to control the signal CTS,RTS,DSR,DTR,RI and DCD;

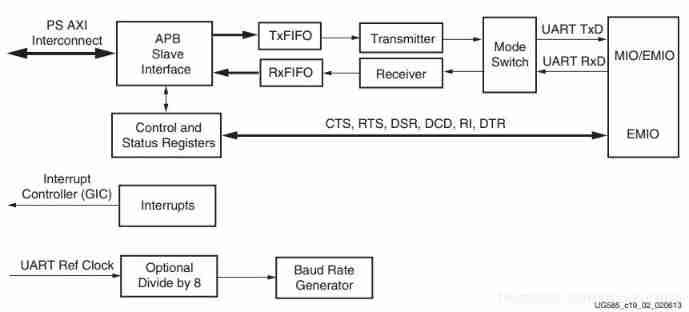

Its structural frame is shown in the figure 1 Shown :

chart 1 UART The structure of

APB Interface :

adopt APB Interface ,PS It can be done to UART Read and write the internal registers of the controller ;

Tx FIFO

Tx FIFO Used to save data from APB Interface write data , Until the transmitter module takes it out and sends it to the transmit shift register ,Tx FIFO Control the flow through the full and empty flags , Besides , You can also set Tx FIFO Trigger level of ;

Rx FIFO:

Rx FIFO Used to save data from the receive shift register ,Rx FIFO The full and empty flag of is used to receive data flow control , Besides , You can also set Rx FIFO Trigger level of ;

transmitter :

The transmitter takes out the transmitter FIFO Data in , And load it into the transmit shift register , Serialize parallel data ;

Receiver :

UART Continuous sampling ua_rxd The signal , When a low level change is detected , Indicates the beginning of receiving data ;

Control and status module :

The control register is used to enable , Disable and issue software resets to receiver and transmitter modules , You can also configure features such as receive timeout and send disconnection ; The mode register selects the clock through the baud rate generator , It is also responsible for selecting the length of bits of data sent and received , Parity bit and stop bit , You can also choose UART Working mode of , Include automatic responses , Local loop, remote loop, etc ;

Interrupt control :

Through channel interrupt status register and channel status register , And the interrupt control module detects from other UART Module events ; By using the interrupt enable register and interrupt disable register , Enable or disable interrupts , The interrupt enable or disable status is reflected in the interrupt mask register ;

Baud rate generator :

chart 2 The principle of baud rate generator is given , In the figure CD Is a bit field of the baud rate generator , Used to generate sample rate clock band_sample.

chart 2 Baud rate transmitter

The final baud rate generation mainly includes the following 3 A step :

- UART Clock selection , It can be directly UART Ref clock, It can also be done by bypass 8 frequency division , The setting is in uart.mode_reg0[0] In the middle of ;

- Yes UART Divide the clock , produce band_sample The frequency calculation formula is as follows :

baud_sample = sel_clk/CD

- Yes baud_sample Divide the frequency again , produce Rx and Tx Baud rate , This step is done by setting BDIV Value completion , That is to say uart.Baud_rate_Divider_reg0[7:0] Set it up , Baud rate calculation formula is as follows :

baud_rate = sel_clk/(CD*(BDIV + 1))

UART Ref clock,CD and BDIV The value of determines UART Baud rate , If UART_Ref_Clk=50MHz,Uart_ref_clk/8=6.25MHz. chart 3 Indicates the corresponding to the typical baud rate CD and eBDIV value ;

chart 3 CD and eBDIV Corresponding baud rate

2 UART Using examples

Instance content : Good configuration ZYNQ Of UART interrupt , Implement interrupt service function , The received data is passed in the receive interrupt UART Send it out ;

To configure UART The steps are as follows :

- adopt UART The peripherals of ID Find the corresponding peripheral information ;

- fill UART Peripheral register base address and some related information ;

- To configure UART Of course GIC interrupt ;

- To configure UART Interrupt trigger mode ( Receive or send interrupt );

- Set up UART Of FIFO Trigger level ;

- Can make UART peripherals ;

To configure UART Of GIC The interrupt steps are as follows :

- Connect to hardware , Map the corresponding interrupt to GIC Interrupt request ;

- find GIC interrupt , fill GIC Interrupt register base address and some related information ;

- find UART Interrupt source , Fill in timer interrupt register base address and some related information ;

- take UART The interrupt is mapped to the interrupt service function of the timer interrupt ;

- Can make GIC interrupt ;

- Enable the mapping of interrupt vector table and interrupt vector table ;

Program source code :

//UART Of GIC initialization

void Init_Gic_Uart(void)

{

XScuGic_Config *IntcConfig;

//connect hardware

Xil_ExceptionInit();

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT,

(Xil_ExceptionHandler)XScuGic_InterruptHandler,

(void *)&Intc);

//find XScuGic device

IntcConfig = XScuGic_LookupConfig(INTC_DEVICE_ID);

//config XScuGic data

XScuGic_CfgInitialize(&Intc,IntcConfig,IntcConfig->CpuBaseAddress);

//GIC Connect to handler function

XScuGic_Connect(&Intc,UART_IRPT_INTR,(Xil_InterruptHandler)UartIntrHandler, (void *)&Uart);

//enable XScuGic

XScuGic_Enable(&Intc,UART_IRPT_INTR);

//enable exception

Xil_ExceptionEnable();

Xil_ExceptionEnableMask(XIL_EXCEPTION_IRQ);

}

//UART initialization

void Init_Uart(void)

{

XUartPs_Config * UartConfigPtr;

//fined uart device

UartConfigPtr = XUartPs_LookupConfig(UART_DEVICE_ID);

//config XUartPs data

XUartPs_CfgInitialize(&Uart,UartConfigPtr,UartConfigPtr->BaseAddress);

//set uart mask

XUartPs_SetInterruptMask(&Uart,XUARTPS_IXR_RXOVR);

XUartPs_SetFifoThreshold(&Uart,10);

//enable uart

XUartPs_EnableUart(&Uart);

}

//UART Interrupt service function

void UartIntrHandler(void *CallBackRef)

{

XUartPs *InstancePrt = (XUartPs *)CallBackRef;

u32 IsrStatus;

u32 ReceivedCount = 0;

u32 CsrRegister;

IsrStatus = XUartPs_ReadReg(InstancePrt->Config.BaseAddress,XUARTPS_IMR_OFFSET);

IsrStatus &= XUartPs_ReadReg(InstancePrt->Config.BaseAddress,XUARTPS_ISR_OFFSET);

if((IsrStatus & ((u32)XUARTPS_IXR_RXOVR | (u32)XUARTPS_IXR_RXEMPTY | (u32)XUARTPS_IXR_RXFULL)) != (u32)0)

{

CsrRegister = XUartPs_ReadReg(InstancePrt->Config.BaseAddress,XUARTPS_SR_OFFSET);

while((CsrRegister & XUARTPS_SR_RXEMPTY) == (u32)0)

{

XUartPs_WriteReg(InstancePrt->Config.BaseAddress,XUARTPS_FIFO_OFFSET,XUartPs_ReadReg(InstancePrt->Config.BaseAddress,XUARTPS_FIFO_OFFSET));

ReceivedCount++;

CsrRegister = XUartPs_ReadReg(InstancePrt->Config.BaseAddress,XUARTPS_SR_OFFSET);

}

}

// printf("thistimeReceivedCount=%d\r\n",ReceivedCount);

XUartPs_WriteReg(InstancePrt->Config.BaseAddress,XUARTPS_ISR_OFFSET,IsrStatus);

}

边栏推荐

- LeetCode+ 51 - 55 回溯、动态规划专题

- 剑指offer II 091.粉刷房子

- Block transmission by golang gin framework

- Path alias specified in vite2.9

- XML序列化向后兼容

- Investment transaction and settlement of the fund

- Application of XOR. (extract the rightmost 1 in the number, which is often used in interviews)

- Real time database - Notes

- R语言绘制 ggplot2 季节性图

- 实时数据库 - 笔记

猜你喜欢

A gadget can write crawlers faster

Devtools implementation principle and performance analysis practice

Sword finger offer|: linked list (simple)

8 figures | analyze Eureka's first synchronization registry

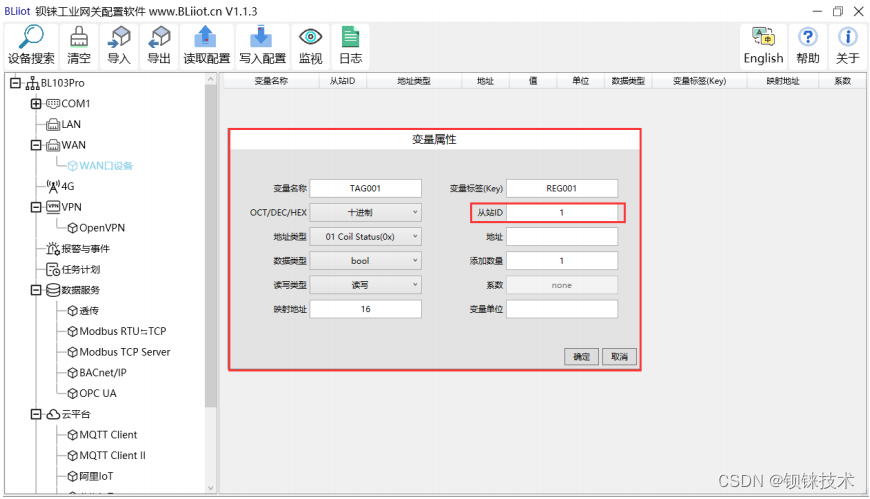

How bacnet/ip gateway collects data of building centralized control system

Modifying MySQL user name root under Linux

8 张图 | 剖析 Eureka 的首次同步注册表

Source code analysis of kubernetes' process of deleting pod

Modifying MySQL port number under Linux

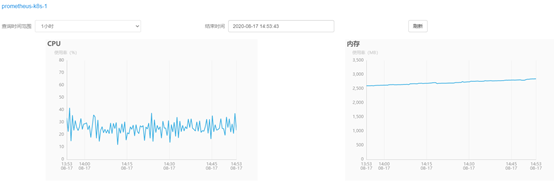

扩展Prometheus的解决方案thanos的简介和几个月使用心得

随机推荐

同花顺网上开户安全吗

QT -- 通讯协议

es6箭头函数中return的用法

7-2 芬兰木棋 结构体排序

Makefile

安全培训是员工最大的福利!2022新员工入职安全培训全员篇

XML序列化向后兼容

Kubernetes cluster lossless upgrade practice

网传互联网公司加班表,排名第一的没悬念

SQL statement optimization steps (1)

Sword finger offer|: linked list (simple)

[thanos source code analysis series]thanos query component source code analysis

DBeaver 22.1.1 发布,可视化数据库管理平台

DOM parsing of XML file case code sentence by sentence analysis

ABAP skill tree

Dbeaver 22.1.1 release, visual database management platform

Face to face experience --- test engineer web side automation --- interview questions for large factories

剑指offer II 091.粉刷房子

QT -- communication protocol

kubernetes部署thanos ruler的发送重复告警的一个隐秘的坑