当前位置:网站首页>Summary of UVM knowledge points

Summary of UVM knowledge points

2022-07-23 05:37:00 【IC fragmentary thoughts】

UVM Summary of knowledge points

Tags: protocol

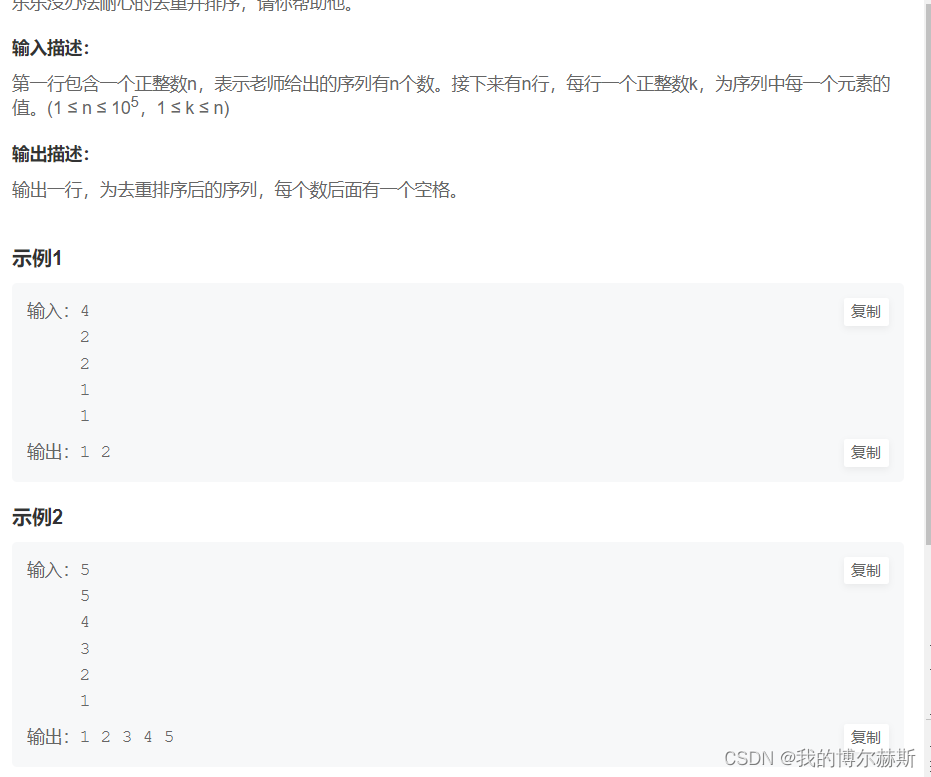

When UVM After starting , Automatically build_phase( Simulation 0 moment )UVM adopt run_test Statement instantiates a break away top_tb Examples of hierarchies , A new hierarchy is established in UVM Verify that... Is in the platform , As long as one class uses uvm_component_utils Register and this class is instantiated , So this kind of main_phase Will automatically be called in each phase in , UVM Will check if there is objection Be mentioned ( raise_objection) , If there is , So wait for this objection Revoked ( drop_objection) Then stop the simulation ; without , It will be over immediately phase. Simulated packets , There is a life cycle , At some point in the simulation , And in check End after comparison

All components in the verification platform should be derived from UVM Class in .

factory Mechanism : You must use macros uvm_component_utils,uvm_object_utils, uvm_object_utils_begin … end Only after registration can you use .

UVM factory The mechanism will maintain a registry , These macros can register user-defined classes into the table .

stay uvm_top Use in run_test(“your_test_name”), It will automatically create and run classes , The name of the object is uvm_test_top. It can also be in run Add :+UVM_TESTNAME=my_case To specify to run a case.

config_db Mechanism : because UVM adopt run_test Statement instantiates a break away top tb Examples of hierarchies , It has established a software world separated from the hardware world , In order to configure the signals in this world ,UVM Introduced config_db Mechanism .

config_db It is divided into set and get Two part operation .

stay main_phase in ,raise_objection() It should be placed before the first time consuming statement , Otherwise it won't work . Of course , The standard is based on uvm Of testbench It should only be in the sequence in raise/drop objection.

stay build_phase From root to leaf , Yes, the creation of subordinate nodes is not started until the creation of each level node is completed . At the same level component The order of creation is uncertain . stay connect_phase Time is the order from leaves to roots .

interface stay class Using in will cause compilation errors . In order to be in class Use in ,SystemVerilog Created virtual interface.

Use UVM The end of a macro statement can be done without a semicolon , Such as uvm_info, uvm_fatal, uvm_component_utils etc. .

UVM test The three main functions of classes : Instantiate the top-level verification environment 2. adopt factory overrides or config db Configure the authentication environment 3. By introducing Sequence To complete test Specific test content .

UVM env class : One soc top env There may be many dedicated Of env, Such as PCIe Env, USB env, Memory controller Env etc. .

filed automation Mechanism : Provide copy(),compare(),print() Such as function , as well as pack_bytes(),unpack_bytes() etc. .

pack_bytes(data_q) take tr All fields in become byte Stream put data_q in , The placing order is based on uvm_filed The writing order of the series of macros is arranged .

unpack_bytes(data_array) Function will data_array Array byte Flow is transformed into tr Has been used in filed automation Registered fields

In defining component When using the name of the parameterized definition transcation type , In this way, you can use its predefined member variables , Such as driver Medium req

sequence Not part of the validation platform .sequence Like a clip , The bullets inside are transcation, and sqeuencer It's a gun . It's useless to throw away the clip after it's used up , But the gun will not be used until the battle is over .

uvm_macros.svh File by include Statements are included . This is a UVM A file in , It contains many macro definitions , Only need to include once .

import Statement will be the whole uvm_pkg Import into the verification platform . Only after importing this library , The compiler is compiling my_driver.sv Only when you read the document uvm_driver Class name .

matters needing attention : stay UVM In the definition , Component or object The registration of should be placed after the declaration of variables .

matters needing attention :uvm_driver There are member variables in seq_item_port, And in the uvm_sequencer There are member variables in seq_item_export, Between the two, a “ passageway ”, Passing through the channel transaction A type is a definition my_sequencer and my_driver When the specified transaction type .

matters needing attention :uvm_top Is a global variable , You can use it directly uvm_top. It is uvm_root An example of , Get its pointer :top=uvm_root::get()

uvm_do Macro does the following :

- Create a transcation Example .

- Randomize it .

- Finally give it to sequencer.

- driver from sequencer In order to get item Methods :

- get_next_item(req) It's blocked

- try_next_item(req) It's non blocking

- try_next_item Your behavior is closer to the real driver act , When it comes to data, it drives data to the bus , Otherwise, the bus will be idle .

- adopt set default_sequence Way to start sequence.

- starting_phase yes uvm_sequence In the base class uvm_phase A member variable of type .sequencer Start up default_sequence when , Will be their own phase Assign a value to starting_phase. therefore sequence Can be used in starting_phase Conduct raise/drop objection.

uvm_transaction and uvm_sequence_item What's the difference? ?

- uvm_transaction It's from uvm_object Derived base class for modeling transactions .

- sequence item Is in uvm_transaction Some other information classes are added based on , for example :sequence id. It is recommended to use uvm_sequence_item Implementation is based on sequence Motivation of

sequencer and driver Handshake agreement between

stay sequence End :

- start_item(): request sequencer visit driver

- finish_item(): send driver receive sequence item, This is a blocking call , stay driver call item_done() Method before returning to .

stay driver End :

- get_next_item(req): This is a driver One of the blocking methods in , Until received sequence item,driver It can be converted into a pin level protocol signal .

- item_done(req): towards sequencer Signal , Show that it can accept new sequence request , bring sequence Release right finish_item() Method blocking .

backdoor and frontdoor What's the difference between visits ?

backdoor visit : adopt RTL Signal path access , No simulation time is consumed

frontdoor visit : Access through data bus protocol , Consume simulation time

Phase Operation of

All that do not consume simulation time phase( namely function phase) All from the bottom up , According to the hierarchy , Sibling structures at the same level are executed in the order of dictionary order .

For different component, The same run_phase( or reset_phase) It's a bottom-up startup , Running at the same time .

For the same component Come on , Its 12 individual run-time Of phase It's sequential . For each component Come on , The overall 12 Small run_phase There may be a gap between , But for , system , all component Of 12 Small run_phase In sequence , The implementation without interval is completed .You can't put my_monitor Medium analysis_port and my_model Medium blocking_get_port Connected ? Need one fifo Well ?

because AP Of writer Functions are non blocking , Return immediately after calling , You need a buffer to store port data

transaction,sequencer And driver The difference between ?

Transaction Inherit and uvm_sequence_item type , yes object type . What is simulated is a packet , Life cycle , From the beginning of generation to the end of comparison .

Driver receive transaction, Responsible for the transaction Level of data into DUT Port level , And drive to DUT,driver Only responsible for driving transaction, And not responsible for producing transaction.uvm_driver It is also a parameterized class , Its parameters are defined transaction type ,component type

Sequencer As sequence And driver The bridge , Arbitrate ,: First of all , Check whether there is a... In the arbitration queue sequence send out transaction Request ;(start_item) second , testing driver Whether to apply for transaction.(get—next_item) .uvm_sequencer Is a parameterized class , Derive from uvm_sequencer. The parameter is my_transaction,component typesequence Not part of the validation platform ,object type , It is also a parameterized class , Its parameters are defined transaction type ,

It is associated with sequencer There is a close connection between , This can be seen from their names . Only in sequencer With the help of the , sequence Produced transaction To finally give to driver; Again , sequencer Only in sequence The value can only be reflected in the situation , without sequence, sequencer It has little effect . sequence It's like a clip , The bullets inside are transaction, and sequencer It's a gun . The clip only makes sense if it is put in the gun , The gun can only exert its power after it is put into the magazine .

every last sequence There is one. body Mission , When one sequence After starting , Automatically body The code in . In the example above , A new macro is used :uvm_do.[`uvm_do(m_trans)] It is used for : ① Create a my_transaction Example m_trans; ② Randomize it ; ③ Finally give it to sequencer.UVM Factory mechanism function

The three functions of the factory , register , establish , heavy load

- convenient component Type generates a tree structure

- by object The type and component Type providing override function

- Provides the copy and clone,compare Other methods

New() and type_id::creat The difference between ? When to do ?

Type_id::creat Will be called indirectly new function , Before calling, it will check whether the target type is overwritten ,

Type_id::creat and new The creation of different will not affect phase Operation of , because , Such as build and connect The implementation of is related to the hierarchical relationship between the organization , The formation of hierarchical relationship is related to the new() Function related . Both methods will call new() functionWhat is a associative array ?

The associative array is SystemVerilog A very useful data type defined in , It is often used in the verification platform .UVM It provides good support , Associated with associative arrays uvm_field Hongyou :

define uvm_field_aa_int_string(ARG, FLAG)define uvm_field_aa_string_string(ARG, FLAG)define uvm_field_aa_object_string(ARG, FLAG)define uvm_field_aa_int_int(ARG, FLAG)

……

Associative arrays have two identification marks , One is the type of data stored , The second is the type of index ,

In this series uvm_field In a series of macros , The first type that appears is the storage data type , The second type is the index type , Such as uvm_field_aa_int_string Used to declare that the stored data is int, And its index is string Associative array of type .m_sequencer and p_sequencer What's the difference? ?

m_sequencer and p_sequencer What's the difference? ?

M_sequence yes uvm_sequence_item Member variables of , It can be understood as a sentence , Point to this sequence Attached to sequencer.m_sequencer yes uvm_sequencer_base type , If you want to access my_sequencer Member variables of , You need to do type conversion , take m_sequence Turn into p_sequence. Use `uvm_declare_p_sequencer Macro declaration p_sequencer, What you actually do is declare p_sequence And realize the conversion of parent class handle to child class handle

边栏推荐

猜你喜欢

随机推荐

How to use fmetp steam V2 (I)

Day7 summary of freshman Summer Internship

C language to realize mine sweeping

Freshman summer internship Day5_ two

VRTK功能教学(一):手柄传送丨手柄瞬移丨触摸板瞬移丨传送

树和二叉树(C语言)

Common libcurl methods post get Download

OpenGL 摄像机 及阶段性复习

FMETP Steam v2 使用方法(二)

Leetcode-204. counting prime numbers

摄像机画面变换和第一人称的移动

PR initial introduction

Print all the words in the string array -- the story of pointer and string

Code random notes_ Array_ 27 remove elements

MySQL

[Err] 1064 - You have an error in your SQL syntax;

How to use fmetp steam V2 (II)

C语言数组,函数,操作符,关键字入门

C语言进阶数据类型详解

L'interface utilisateur 3D ou le modèle dans l'unit é fait toujours face à la caméra et tourne avec l'angle de vue de la caméra 丨 l'angle de vue suit 丨 l'angle de vue fixe