当前位置:网站首页>[write CPU by yourself] implementation of exception related instructions

[write CPU by yourself] implementation of exception related instructions

2022-06-22 06:30:00 【Abaabaababa】

MIPS Exception types defined in the schema

MIPS32 Architecture , Some things interrupt the normal execution process of the program , These things are called interrupt 、 trap 、 System calls and other interruptions in the process of program execution , Collectively referred to as exceptions .

Here OpenMIPS The processor only implements 6 Handling of exceptions in :

- Hardware reset

- interrupt ( Soft interrupt 、 Hard interrupt )

- syscall system call

- Invalid instructions

- overflow

- Exception thrown by self trapping instruction

After the exception , Enter the exception handling routine for specific processing , After processing , Return to the state before the exception and continue to execute .` Hardware reset is a special exception , It is not necessary to return from the exception handling routine , There is no need to protect the site , No need to save the return address , The treatment here is simple and crude : Clear all registers , From address 0x0 Processing instruction execution , It's reset . So this disposal details other 5 An exception handling process .

Precise anomaly

When an exception occurs , The sequential execution of the system will be interrupted , here , Several instructions are in different stages of the pipeline , The processor goes to the exception handling routine , After exception handling, return to the original program to continue execution . When an exception occurs , Because you don't want the exception handling routine to destroy the normal execution of the original program , For instructions that have not been executed , You must remember which stage of the assembly line it is in , So that execution can be resumed after exception handling , This is the exact exception

When an exception occurs , An instruction that is interrupted by an exception is called Abnormal victim , All the instructions preceding this instruction must be executed to the last stage of the pipeline , I.e. normal completion . However, the instruction and the instructions after the instruction must be cancelled .

for example

e.g.1

The second order add An overflow exception occurred during execution , under these circumstances , Instructions 1ori The instructions will be successfully completed , Instructions 2,3,4 Will be canceled . In order to achieve precise exception , The order in which exceptions occur must be the same as the order of instructions . On a pipeline processor , Exceptions occur at different stages of the pipeline , Bring problems .

e.g.2

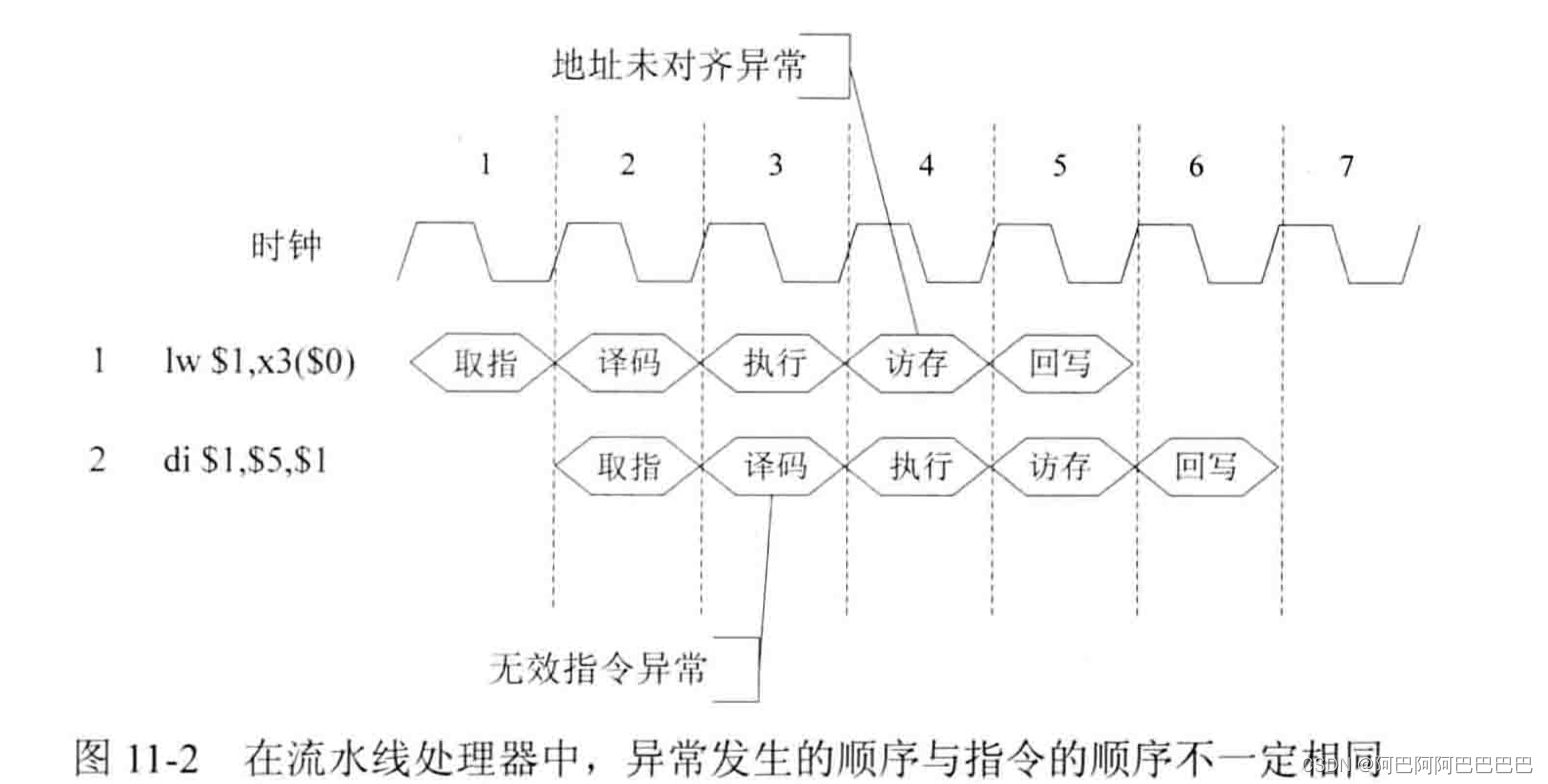

Load instruction lw An address misaligned exception will occur during the memory access phase of the pipeline , The exception will occur in the Four Clock cycles occur , The latter instruction di Is an invalid instruction mips32 Architecture does not have this directive , So it's invalid , An invalid instruction exception is thrown in the pipeline stage , That is the first. 3、 ... and A cycle , here Last load instruction lw It is still in the implementation stage , Not entering the deposit access stage , So the first exception that occurs is an invalid instruction exception . thus The order in which the unsatisfied exception occurs is the same as that of the instruction This requirement .

in order to avoid foregoing circumstances , Exceptions that occur first are not handled immediately , The exception event is simply marked , And continue to run the pipeline , In most processors , Meeting Design a special pipeline stage , Dedicated to handling exceptions , If The exception event of an instruction reaches this stage of the pipeline , Will be Do exception handling , And the exception events of the instructions currently in the rest of the pipeline will be Ignore .

Pictured above is an example , Assume that the processor will be in Handle exceptions in the storage access phase , that di The instruction is abnormal in the third cycle , But not Don't deal with , Just one. Save an exception tag , Wait to In the fifth clock cycle, the instruction will be processed when it enters the memory access phase . But in The fourth clock cycle , The last instruction lw Enter the deposit access stage , and Address misaligned exception occurred , Because it is already in In the stage of visit and deposit , So will Handle the exception , Include Exceptions in the rest of the pipeline, including invalid instruction exceptions, are ignored .

By the above methods , Implementation in pipeline processor Handle exceptions in the order they are executed , Instead of handling exceptions in the order they occur .

Exception handling

EXL by 1, It indicates that it is currently in the process of exception handling , If the current exception type is interrupt , So don't deal with , Ignore , Because interrupts are forbidden during exception handling . If the current exception type is not interrupt , Then save the exception reason to CP0 Medium Cause The register of ExCode Field

If EXL by 0, that Save the exception cause to CP0 Medium Cause The register of ExCode Field , Go to step two

Check occurrence Whether the abnormal instruction is in the delay slot , If in the delay slot , Then set EPC The value of the register is the address of the instruction minus 4, Simultaneous setting Cause The register of BD Field is 1, conversely , Set up EPC The value of the register is at the address of the instruction , Simultaneous setting Cause The register of BD Field is 0.

Set up Status register EXL Field is 1, Express Enter the exception handling process , No interruptions

The processor is transferred to A predefined address , In that address there are often Exception handling routine , Exception handling in it , This address is called Enter address for exception handling routine OpenMIPS The defined exception handling routine entry address table is as follows . Here is the system call 、 Invalid instructions 、 overflow 、 The four types of self trapping exceptions are all set to the same processing routine entry address , It can also be set to different addresses .

Specific exception handling will be performed in the exception handling routine , After processing , You need to return to the state before the exception to continue execution . Exception return instruction eret To finish the work ,eret The command should be cleared Status The register of EXL Field , So as to enable interruption , Try to make EPC The address saved in the register is restored to PC in , So as to return to the place where the exception occurred and continue to execute

After the delay slot is introduced , The order in which the processor executes the branch instructions :

Transfer order -> Delay slot instruction -> Transfer target instruction address

flow chart ( I am too lazy to draw )

Introduction to exception related instructions

Self trapping instruction

According to whether the instruction contains an immediate number , It is divided into 2 class

Self trapping instructions that do not contain immediate numbers

| 31-26 | 25-21 | 20-16 | 15-6 | 5-0 | useage | function |

|---|---|---|---|---|---|---|

| SPECIAL(000000) | rs | rt | code | TEQ(110100) | teq rs,rt | if GPR[rs]=GPR[rt] then trap Address is rs The value and address of the general-purpose register are rt Compare the values of the general-purpose registers of , If the two are equal , Self trapping exception occurs |

| SPECIAL(000000) | rs | rt | code | TGE(110000) | tge rs,rt | if GPR[rs] >= GPR[rt] then trap Address is rs The value and address of the general-purpose register are rt The value of a general-purpose register is compared as a signed number , If the former is greater than the latter , Then a self trapping exception is raised |

| SPECIAL(000000) | rs | rt | code | TGEU(110001) | tgeu rs,rt | if GPR[rs] >= GPR[rt] then trap Address is rs The value and address of the general-purpose register are rt The value of the general-purpose register of is used as nothing Symbol number comparison , If the former is greater than the latter , Then a self trapping exception is raised |

| SPECIAL(000000) | rs | rt | code | TLT(110010) | tlt rs,rt | if GPR[rs] < GPR[rt] then trap Address is rs The value and address of the general-purpose register are rt The value of a general-purpose register is compared as a signed number , If the former Small In the latter , Then a self trapping exception is raised |

| SPECIAL(000000) | rs | rt | code | TLTU(110011) | tltu rs,rt | if GPR[rs] >= GPR[rt] then trap Address is rs The value and address of the general-purpose register are rt The value of the general-purpose register of the nothing · Symbol number comparison , If the former Small In the latter , Then a self trapping exception is raised |

| SPECIAL(000000) | rs | rt | code | TNE(110110) | tne rs,rt | if GPR[rs] != GPR[rt] then trap Address is rs The value and address of the general-purpose register are rt Compare the values of the general-purpose registers of , If the two are not equal , Then a self trapping exception is raised |

A self trapping instruction containing an immediate number

| 31-26 | 25-21 | 20-16 | 15-0 | useage | function |

|---|---|---|---|---|---|

| REGIMM(000001) | rs | TEQI(01100) | immediate | teqi rs ,immediate | if GPR[rs]=sign_extended(immediate) then trap Address is rs The value of the general-purpose register and the instruction 16 The bit immediate sign is extended to 32 position Compare the values after , If the two are equal , That causes a self trapping anomaly |

| REGIMM(000001) | rs | TGEI(01000) | immediate | tgei rs ,immediate | if GPR[rs]=sign>=extended(immediate) then trap Address is rs The value of the general-purpose register and the instruction 16 The bit immediate sign is extended to 32 position Compare the values after , If the former is greater than or equal to the latter , Then a self trapping exception is raised |

| REGIMM(000001) | rs | TGEIU(01001) | immediate | tgeiu rs ,immediate | if GPR[rs]>=sign_extended(immediate) then trap Address is rs The value of the general-purpose register and the instruction 16 The bit immediate sign is extended to 32 The values after bits are compared as unsigned numbers , If the former is greater than or equal to the latter , Then a self trapping exception is raised |

| REGIMM(000001) | rs | TLTI(01010) | immediate | tlti rs ,immediate | if GPR[rs]<sign_extended(immediate) then trap Address is rs The value of the general-purpose register and the instruction 16 The bit immediate sign is extended to 32 The values after bits are compared as signed numbers , If the former is less than the latter , Then a self trapping exception is raised 、REGIMM(000001) |

| REGIMM(000001) | rs | TNEI(01110) | immediate | tnei rs ,immediate | if GPR[rs]!=sign_extended(immediate) then trap Address is rs The value of the general-purpose register and the instruction 16 The bit immediate sign is extended to 32 Compare the values after bits , If the two are not equal , Then a self trapping exception is raised |

Exception return instruction eret

| 31-26 | 25 | 24-6 | 5-0 | useage | function |

|---|---|---|---|---|---|

| COP0(010000) | CO(1) | 0000 0000 0000 0000 000 | ERET(011000) | eret | Returns... From the exception handling routine , Execute the command (1) yes EPC The value of the register is called the new fetch address (2) Set up Status The register of EXL Field is 0, Indicates that it is no longer at the exception level |

System call instructions syscall

| 31-26 | 25-6 | 5-0 | useage | function |

|---|---|---|---|---|

| SPECIAL(000000) | code | SYSCALL(001100) | syscall | System call exception thrown . Programs in user mode perform operations that can only be performed in kernel mode , You can call syscall Instructions , System call exception thrown , Enter the exception handling routine , So you can go into kernel mode |

Realize the idea

Mobile phone exception information at each stage of the assembly line , And pass it to the pipeline memory access stage , Handle the exception information at the same time in the memory access stage . Exception information to be collected at each stage of the pipeline :

decoding

Determine whether the system call is abnormal 、 Whether to return the instruction 、 Invalid instructions

perform

Judge whether there is self trapping anomaly 、 Overflow exception

Visiting and depositing

Check if there is any interruption . In the stage of visit and deposit , Processor combination CP0 The value of the relevant register in , Determine whether the exception needs to be handled , If you need to deal with , Then transfer to the entry address of the processing routine corresponding to the exception , Clear all information on the pipeline except the write back phase , Also modify the coprocessor CP0 The value of the relevant register in .eret Instructions , Transferred to the EPC At the address where the register is stored , At the same time, all information on the pipeline except the write back stage is cleared , Modify the coprocessor CP0 The value of the relevant register in . It is called clearing the information of a certain stage on the pipeline , In fact, you can set all the registers in this stage as initial values

Modification of data flow diagram

Determine the self trapping instruction 、syscall quality 、eret Instruction process

id

Modification of system structure

id

id The module determines whether to call the instruction syscall, Exception return instruction eret, Invalid instructions , Pass this information through excepttype_o Interface passed to ex modular , At the same time, the instruction address is passed through current_inst_addr_o The interface is passed to the execution phase .

ex

ex The module further determines whether there is a self trapping exception , Or overflow exception . This information will be integrated into id In the exception information of the module ,excepttype_i Pass in , adopt excepttype_o Pass on to mem modular . meanwhile current_inst_addr_o The interface passes the instruction address to mem modular , adopt is_delayslot_o Indicates whether the instruction is in the delay slot , This information will also be passed into mem modular .

mem

mem The module is based on the passed Exception types excepttype_i,Cause Register value cp0_cause_i,Status Register value cp0_status_i, Comprehensively judge whether to handle exceptions , If you need to deal with , The final exception type will skip excepttype_o The interface is sent to CTRL modular ,CTRL The module gives the entry address for exception handling new_pc Pass on to PC.

cp0_reg

When handling exceptions , Need modification CP0 Medium EPC,Status,Cause And so on , therefore mem The final exception type given by the module also needs to pass excepttype_o Interface feeding CP0 modular , Whether the abnormal command sent in at the same time is in the delay slot is_in_delayslot_i Interface feeding , The address of the exception instruction current_inst_address_o Interface feeding .CP0 The module modifies the value of the corresponding register according to this information .

CTRL

If you want to handle exceptions , It is necessary to clear the pipeline Writeback phase The value of the external register ,CTRL Modules are sent out by flush Realization .flush Module delivery PC,IF/ID,ID/EX,EX/MEM,MEM/WB Equal module , Set the registers in these modules as initial values .

LLbit

ll Set when executing LLbit by 1,sc Execution time , Check whether the register is 1, If 1 Just run normally , If 0, It indicates that there is interference , No storage operation . One of the causes of interference is ll,sc An exception occurred between the instructions , Therefore, one more step will be taken in the process of exception handling , take LLbit Register set to 0.

Code

Because it was written by myself cpu The last chapter of the Basic Edition , So put the complete code up .

pc_reg.v

`include "define.v"

module pc_reg(

input wire clk,

input wire rst,

// Information from the control module

input wire[5:0] stall,

input wire flush,

input wire[`RegBus] new_pc,

// Information from the decoding phase

input wire branch_flag_i,

input wire[`RegBus] branch_target_address_i,

output reg[`InstAddrBus] pc,

output reg ce

);

always @ (posedge clk) begin

if (rst == `RstEnable) begin

ce <= `ChipDisable;

end else begin

ce <= `ChipEnable;

end

end

/*always @ (posedge clk) begin if (ce == `ChipDisable) begin pc <= 32'h00000000; end else if(stall[0] == `NoStop)begin if(branch_flag_i == `Branch)begin// If a transfer occurs pc <= branch_target_address_i;// Give the destination address of the transfer end else begin pc <= pc + 4'h4; end end end*/

always @ (posedge clk)begin

if(ce == `ChipDisable)begin

pc <= 32'h00000000;

end else begin

if(flush == 1'b1)begin

//flush==1 Indicates that an exception occurred Will be taken from CTRL Exception handling given by the module

// Routine entry address new_pc Processing instruction execution

pc <= new_pc;

end else if(stall[0] == `NoStop)begin

end

end

end

end

endmodule

inst_rom.v

`include "define.v"

//inst_rom.v

module inst_rom(

input wire ce,

input wire[`InstAddrBus] addr,

output reg[`InstBus] inst

);

// Define an array , Size is InstMemNum, The element width is InstBus

reg[`InstBus] inst_mem[0:`InstMemNum-1];

// Working with files inst_rom.data Initialize instruction memory

initial $readmemh ("D:/test_2/inst_rom_11_3.data",inst_mem);

always @ (*)

begin

if(ce == `ChipDisable)// When the reset signal is invalid , According to the address entered , Give instruction memory ROM Corresponding elements in

begin

inst <= `ZeroWord;

end

else begin

inst <= inst_mem[addr[`InstMemNumLog2+1:2]];

end

end

endmodule

if_id.v

`include "define.v"

module if_id(

input wire clk,

input wire rst,

input wire[`InstAddrBus] if_pc,

input wire[`InstBus] if_inst,

input wire[5:0] stall, // Information from the control module

input wire flush,

output reg[`InstAddrBus] id_pc,

output reg[`InstBus] id_inst

);

/************************** explain ****************************** *****stall[0] Indicates the fetch address PC Whether it remains the same , by 1 Keep the same ***** *******stall[1] Indicates whether the pipeline fetch phase is suspended , by 1 To suspend ******* *******stall[2] Indicates whether the pipeline decoding phase is suspended , by 1 To suspend ******* *******stall[3] Indicates whether the pipeline execution phase is suspended , by 1 To suspend ******* *******stall[4] Indicates whether the pipeline memory access phase is suspended , by 1 To suspend ******* *******stall[5] Indicates whether the pipeline write back phase is suspended , by 1 To suspend ******* (1)stall[1] by Stop,stall[5] by NoStop, Indicates that the fetch phase is suspended , Decoding stage continue , Therefore, the null instruction is used as the instruction entering the decoding stage in the next cycle (2)stall[1] by NoStop, The finger picking phase continues , The obtained instruction enters the decoding stage (3) The rest of the time , Keep the register of decoding stage id_pc,id_inst unchanged ************************************************************/

always @ (posedge clk) begin

if (rst == `RstEnable) begin

id_pc <= `ZeroWord;

id_inst <= `ZeroWord;

end else if(flush== 1'b1)begin

// Exception occurs Clear the pipeline So reset id_pc id_inst Register value

id_pc <= `ZeroWord;

id_inst <= `ZeroWord;

end else if(stall[1] == `Stop && stall[2] == `NoStop)begin

id_pc <= `ZeroWord;

id_inst <= `ZeroWord;

end else if(stall[1] == `NoStop)begin

id_pc <= if_pc;

id_inst <= if_inst;

end

end

endmodule

ctrl.v

//ctrl.v

`include "define.v"

module ctrl(

input wire rst,

input wire stallreq_from_id,

input wire stallreq_from_ex,

input wire[31:0] excepttype_i,

input wire[`RegBus] cp0_epc_i,

output reg[5:0] stall,

output reg[`RegBus] new_pc,

output reg flush

);

/************************** explain ****************************** *****stall[0] Indicates the fetch address PC Whether it remains the same , by 1 Keep the same ***** *******stall[1] Indicates whether the pipeline fetch phase is suspended , by 1 To suspend ******* *******stall[2] Indicates whether the pipeline decoding phase is suspended , by 1 To suspend ******* *******stall[3] Indicates whether the pipeline execution phase is suspended , by 1 To suspend ******* *******stall[4] Indicates whether the pipeline memory access phase is suspended , by 1 To suspend ******* *******stall[5] Indicates whether the pipeline write back phase is suspended , by 1 To suspend ******* ************************************************************/

always @ (*) begin

if(rst == `RstEnable) begin

stall <= 6'b000000;

flush <= 1'b0;

new_pc <= `ZeroWord;

end else if(excepttype_i != `ZeroWord) begin

flush <= 1'b1;

stall <= 6'b000000;

case (excepttype_i)

32'h00000001: begin //interrupt

new_pc <= 32'h00000020;

end

32'h00000008: begin //syscall

new_pc <= 32'h00000040;

end

32'h0000000a: begin //inst_invalid

new_pc <= 32'h00000040;

end

32'h0000000d: begin //trap

new_pc <= 32'h00000040;

end

32'h0000000c: begin //ov

new_pc <= 32'h00000040;

end

32'h0000000e: begin //eret

new_pc <= cp0_epc_i;

end

default : begin

end

endcase

end else if(stallreq_from_ex == `Stop) begin

stall <= 6'b001111;

flush <= 1'b0;

end else if(stallreq_from_id == `Stop) begin

stall <= 6'b000111;

flush <= 1'b0;

end else begin

stall <= 6'b000000;

flush <= 1'b0;

new_pc <= `ZeroWord;

end //if

end //always

endmodule

data_ram.v

`include "define.v"

module data_ram(

input wire clk,

input wire ce,// Data memory enable signal

input wire we,// Whether it is a write operation Write 1

input wire[`DataAddrBus] addr,// Address to visit

input wire[3:0] sel,// Byte select signal

input wire[`DataBus] data_i,// The data to be written

output reg[`DataBus] data_o// Read out data

);

// Define a four byte array

reg[`ByteWidth] data_mem0[0:`DataMemNum-1];

reg[`ByteWidth] data_mem1[0:`DataMemNum-1];

reg[`ByteWidth] data_mem2[0:`DataMemNum-1];

reg[`ByteWidth] data_mem3[0:`DataMemNum-1];

// Write operations

always @ (posedge clk)begin

if(ce == `ChipDisable) begin

end else if(we == `WriteEnable)begin

if(sel[3] == 1'b1)begin

data_mem3[addr[`DataMemNumLog2+1:2]] <= data_i[31:24];

end

if(sel[2] == 1'b1)begin

data_mem2[addr[`DataMemNumLog2+1:2]] <= data_i[23:16];

end

if(sel[1] == 1'b1)begin

data_mem1[addr[`DataMemNumLog2+1:2]] <= data_i[15:8];

end

if(sel[0 == 1'b1])begin

data_mem0[addr[`DataMemNumLog2+1:2]] <= data_i[7:0];

end

end

end

// Read operations

always @ (*) begin

if(ce == `ChipDisable)begin

data_o <= `ZeroWord;

end else if(we == `WriteDisable)begin

data_o <= {

data_mem3[addr[`DataMemNumLog2+1:2]],data_mem2[addr[`DataMemNumLog2+1:2]],data_mem1[addr[`DataMemNumLog2+1:2]],data_mem0[addr[`DataMemNumLog2+1:2]]};

end else begin

data_o <= `ZeroWord;

end

end

endmodule

define.v

// overall situation

`define RstEnable 1'b1

`define RstDisable 1'b0

`define ZeroWord 32'h00000000

`define WriteEnable 1'b1

`define WriteDisable 1'b0

`define ReadEnable 1'b1

`define ReadDisable 1'b0

`define AluOpBus 7:0

`define AluSelBus 2:0

`define InstValid 1'b0

`define InstInvalid 1'b1

`define Stop 1'b1

`define NoStop 1'b0

`define InDelaySlot 1'b1

`define NotInDelaySlot 1'b0

`define Branch 1'b1

`define NotBranch 1'b0

`define InterruputAssert 1'b1

`define InterruputNotAssert 1'b0

`define TrapAssert 1'b1

`define TrapNotAssert 1'b0

`define True_v 1'b1

`define False_v 1'b0

`define ChipEnable 1'b1

`define ChipDisable 1'b0

// Instructions

`define EXE_AND 6'b100100

`define EXE_OR 6'b100101

`define EXE_XOR 6'b100110

`define EXE_NOR 6'b100111

`define EXE_ANDI 6'b001100

`define EXE_ORI 6'b001101

`define EXE_XORI 6'b001110

`define EXE_LUI 6'b001111

`define EXE_SLL 6'b000000

`define EXE_SLLV 6'b000100

`define EXE_SRL 6'b000010

`define EXE_SRLV 6'b000110

`define EXE_SRA 6'b000011

`define EXE_SRAV 6'b000111

`define EXE_SYNC 6'b001111

`define EXE_PREF 6'b110011

`define EXE_MOVZ 6'b001010

`define EXE_MOVN 6'b001011

`define EXE_MFHI 6'b010000

`define EXE_MTHI 6'b010001

`define EXE_MFLO 6'b010010

`define EXE_MTLO 6'b010011

`define EXE_SLT 6'b101010

`define EXE_SLTU 6'b101011

`define EXE_SLTI 6'b001010

`define EXE_SLTIU 6'b001011

`define EXE_ADD 6'b100000

`define EXE_ADDU 6'b100001

`define EXE_SUB 6'b100010

`define EXE_SUBU 6'b100011

`define EXE_ADDI 6'b001000

`define EXE_ADDIU 6'b001001

`define EXE_CLZ 6'b100000

`define EXE_CLO 6'b100001

`define EXE_MULT 6'b011000

`define EXE_MULTU 6'b011001

`define EXE_MUL 6'b000010

`define EXE_MADD 6'b000000

`define EXE_MADDU 6'b000001

`define EXE_MSUB 6'b000100

`define EXE_MSUBU 6'b000101

`define EXE_DIV 6'b011010

`define EXE_DIVU 6'b011011

`define EXE_J 6'b000010

`define EXE_JAL 6'b000011

`define EXE_JALR 6'b001001

`define EXE_JR 6'b001000

`define EXE_BEQ 6'b000100

`define EXE_BGEZ 5'b00001

`define EXE_BGEZAL 5'b10001

`define EXE_BGTZ 6'b000111

`define EXE_BLEZ 6'b000110

`define EXE_BLTZ 5'b00000

`define EXE_BLTZAL 5'b10000

`define EXE_BNE 6'b000101

`define EXE_LB 6'b100000

`define EXE_LBU 6'b100100

`define EXE_LH 6'b100001

`define EXE_LHU 6'b100101

`define EXE_LL 6'b110000

`define EXE_LW 6'b100011

`define EXE_LWL 6'b100010

`define EXE_LWR 6'b100110

`define EXE_SB 6'b101000

`define EXE_SC 6'b111000

`define EXE_SH 6'b101001

`define EXE_SW 6'b101011

`define EXE_SWL 6'b101010

`define EXE_SWR 6'b101110

`define EXE_SYSCALL 6'b001100

`define EXE_TEQ 6'b110100

`define EXE_TEQI 5'b01100

`define EXE_TGE 6'b110000

`define EXE_TGEI 5'b01000

`define EXE_TGEIU 5'b01001

`define EXE_TGEU 6'b110001

`define EXE_TLT 6'b110010

`define EXE_TLTI 5'b01010

`define EXE_TLTIU 5'b01011

`define EXE_TLTU 6'b110011

`define EXE_TNE 6'b110110

`define EXE_TNEI 5'b01110

`define EXE_ERET 32'b01000010000000000000000000011000

`define EXE_NOP 6'b000000

`define SSNOP 32'b00000000000000000000000001000000

`define EXE_SPECIAL_INST 6'b000000

`define EXE_REGIMM_INST 6'b000001

`define EXE_SPECIAL2_INST 6'b011100

//AluOp

`define EXE_AND_OP 8'b00100100

`define EXE_OR_OP 8'b00100101

`define EXE_XOR_OP 8'b00100110

`define EXE_NOR_OP 8'b00100111

`define EXE_ANDI_OP 8'b01011001

`define EXE_ORI_OP 8'b01011010

`define EXE_XORI_OP 8'b01011011

`define EXE_LUI_OP 8'b01011100

`define EXE_SLL_OP 8'b01111100

`define EXE_SLLV_OP 8'b00000100

`define EXE_SRL_OP 8'b00000010

`define EXE_SRLV_OP 8'b00000110

`define EXE_SRA_OP 8'b00000011

`define EXE_SRAV_OP 8'b00000111

`define EXE_MOVZ_OP 8'b00001010

`define EXE_MOVN_OP 8'b00001011

`define EXE_MFHI_OP 8'b00010000

`define EXE_MTHI_OP 8'b00010001

`define EXE_MFLO_OP 8'b00010010

`define EXE_MTLO_OP 8'b00010011

`define EXE_SLT_OP 8'b00101010

`define EXE_SLTU_OP 8'b00101011

`define EXE_SLTI_OP 8'b01010111

`define EXE_SLTIU_OP 8'b01011000

`define EXE_ADD_OP 8'b00100000

`define EXE_ADDU_OP 8'b00100001

`define EXE_SUB_OP 8'b00100010

`define EXE_SUBU_OP 8'b00100011

`define EXE_ADDI_OP 8'b01010101

`define EXE_ADDIU_OP 8'b01010110

`define EXE_CLZ_OP 8'b10110000

`define EXE_CLO_OP 8'b10110001

`define EXE_MULT_OP 8'b00011000

`define EXE_MULTU_OP 8'b00011001

`define EXE_MUL_OP 8'b10101001

`define EXE_MADD_OP 8'b10100110

`define EXE_MADDU_OP 8'b10101000

`define EXE_MSUB_OP 8'b10101010

`define EXE_MSUBU_OP 8'b10101011

`define EXE_DIV_OP 8'b00011010

`define EXE_DIVU_OP 8'b00011011

`define EXE_J_OP 8'b01001111

`define EXE_JAL_OP 8'b01010000

`define EXE_JALR_OP 8'b00001001

`define EXE_JR_OP 8'b00001000

`define EXE_BEQ_OP 8'b01010001

`define EXE_BGEZ_OP 8'b01000001

`define EXE_BGEZAL_OP 8'b01001011

`define EXE_BGTZ_OP 8'b01010100

`define EXE_BLEZ_OP 8'b01010011

`define EXE_BLTZ_OP 8'b01000000

`define EXE_BLTZAL_OP 8'b01001010

`define EXE_BNE_OP 8'b01010010

`define EXE_LB_OP 8'b11100000

`define EXE_LBU_OP 8'b11100100

`define EXE_LH_OP 8'b11100001

`define EXE_LHU_OP 8'b11100101

`define EXE_LL_OP 8'b11110000

`define EXE_LW_OP 8'b11100011

`define EXE_LWL_OP 8'b11100010

`define EXE_LWR_OP 8'b11100110

`define EXE_PREF_OP 8'b11110011

`define EXE_SB_OP 8'b11101000

`define EXE_SC_OP 8'b11111000

`define EXE_SH_OP 8'b11101001

`define EXE_SW_OP 8'b11101011

`define EXE_SWL_OP 8'b11101010

`define EXE_SWR_OP 8'b11101110

`define EXE_SYNC_OP 8'b00001111

`define EXE_MFC0_OP 8'b01011101

`define EXE_MTC0_OP 8'b01100000

`define EXE_SYSCALL_OP 8'b00001100

`define EXE_TEQ_OP 8'b00110100

`define EXE_TEQI_OP 8'b01001000

`define EXE_TGE_OP 8'b00110000

`define EXE_TGEI_OP 8'b01000100

`define EXE_TGEIU_OP 8'b01000101

`define EXE_TGEU_OP 8'b00110001

`define EXE_TLT_OP 8'b00110010

`define EXE_TLTI_OP 8'b01000110

`define EXE_TLTIU_OP 8'b01000111

`define EXE_TLTU_OP 8'b00110011

`define EXE_TNE_OP 8'b00110110

`define EXE_TNEI_OP 8'b01001001

`define EXE_ERET_OP 8'b01101011

`define EXE_NOP_OP 8'b00000000

//AluSel

`define EXE_RES_LOGIC 3'b001

`define EXE_RES_SHIFT 3'b010

`define EXE_RES_MOVE 3'b011

`define EXE_RES_ARITHMETIC 3'b100

`define EXE_RES_MUL 3'b101

`define EXE_RES_JUMP_BRANCH 3'b110

`define EXE_RES_LOAD_STORE 3'b111

`define EXE_RES_NOP 3'b000

// Instruction memory inst_rom

`define InstAddrBus 31:0

`define InstBus 31:0

`define InstMemNum 131071

`define InstMemNumLog2 17

// Data storage data_ram

`define DataAddrBus 31:0

`define DataBus 31:0

`define DataMemNum 131071

`define DataMemNumLog2 17

`define ByteWidth 7:0

// General registers regfile

`define RegAddrBus 4:0

`define RegBus 31:0

`define RegWidth 32

`define DoubleRegWidth 64

`define DoubleRegBus 63:0

`define RegNum 32

`define RegNumLog2 5

`define NOPRegAddr 5'b00000

// division div

`define DivFree 2'b00

`define DivByZero 2'b01

`define DivOn 2'b10

`define DivEnd 2'b11

`define DivResultReady 1'b1

`define DivResultNotReady 1'b0

`define DivStart 1'b1

`define DivStop 1'b0

//CP0 Register address

`define CP0_REG_COUNT 5'b01001 // read-write

`define CP0_REG_COMPARE 5'b01011 // read-write

`define CP0_REG_STATUS 5'b01100 // read-write

`define CP0_REG_CAUSE 5'b01101 // read-only

`define CP0_REG_EPC 5'b01110 // read-write

`define CP0_REG_PrId 5'b01111 // read-only

`define CP0_REG_CONFIG 5'b10000 // read-only

div.v

`include "define.v"

module div(

input wire clk,

input wire rst,

input wire signed_div_i,

input wire[31:0] opdata1_i,

input wire[31:0] opdata2_i,

input wire start_i,

input wire annul_i,

output reg[63:0] result_o,

output reg ready_o

);

wire[32:0] div_temp;

reg[5:0] cnt;

reg[64:0] dividend;

reg[1:0] state;

reg[31:0] divisor;

reg[31:0] temp_op1;

reg[31:0] temp_op2;

assign div_temp = {

1'b0,dividend[63:32]} - {1'b0,divisor};

always @ (posedge clk) begin

if (rst == `RstEnable) begin

state <= `DivFree;

ready_o <= `DivResultNotReady;

result_o <= {

`ZeroWord,`ZeroWord};

end else begin

case (state)

`DivFree: begin //DivFree״̬

if(start_i == `DivStart && annul_i == 1'b0) begin

if(opdata2_i == `ZeroWord) begin

state <= `DivByZero;

end else begin

state <= `DivOn;

cnt <= 6'b000000;

if(signed_div_i == 1'b1 && opdata1_i[31] == 1'b1 ) begin

temp_op1 = ~opdata1_i + 1;

end else begin

temp_op1 = opdata1_i;

end

if(signed_div_i == 1'b1 && opdata2_i[31] == 1'b1 ) begin

temp_op2 = ~opdata2_i + 1;

end else begin

temp_op2 = opdata2_i;

end

dividend <= {

`ZeroWord,`ZeroWord};

dividend[32:1] <= temp_op1;

divisor <= temp_op2;

end

end else begin

ready_o <= `DivResultNotReady;

result_o <= {

`ZeroWord,`ZeroWord};

end

end

`DivByZero: begin //DivByZero״̬

dividend <= {

`ZeroWord,`ZeroWord};

state <= `DivEnd;

end

`DivOn: begin //DivOn״̬

if(annul_i == 1'b0) begin

if(cnt != 6'b100000) begin

if(div_temp[32] == 1'b1) begin

dividend <= {

dividend[63:0] , 1'b0};

end else begin

dividend <= {

div_temp[31:0] , dividend[31:0] , 1'b1};

end

cnt <= cnt + 1;

end else begin

if((signed_div_i == 1'b1) && ((opdata1_i[31] ^ opdata2_i[31]) == 1'b1)) begin

dividend[31:0] <= (~dividend[31:0] + 1);

end

if((signed_div_i == 1'b1) && ((opdata1_i[31] ^ dividend[64]) == 1'b1)) begin

dividend[64:33] <= (~dividend[64:33] + 1);

end

state <= `DivEnd;

cnt <= 6'b000000;

end

end else begin

state <= `DivFree;

end

end

`DivEnd: begin //DivEnd״̬

result_o <= {

dividend[64:33], dividend[31:0]};

ready_o <= `DivResultReady;

if(start_i == `DivStop) begin

state <= `DivFree;

ready_o <= `DivResultNotReady;

result_o <= {

`ZeroWord,`ZeroWord};

end

end

endcase

end

end

endmodule

id.v

`include "define.v"

module id(

input wire rst,

input wire[`InstAddrBus] pc_i,

input wire[`InstBus] inst_i,

input wire[`RegBus] reg1_data_i,

input wire[`RegBus] reg2_data_i,

input wire is_in_delayslot_i,// Whether it is in the delay slot instruction

// Deliver to regfile Information about

output reg reg1_read_o,

output reg reg2_read_o,

output reg[`RegAddrBus] reg1_addr_o,

output reg[`RegAddrBus] reg2_addr_o,

// Information sent to the execution phase

output reg[`AluOpBus] aluop_o,

output reg[`AluSelBus] alusel_o,

output reg[`RegBus] reg1_o,

output reg[`RegBus] reg2_o,

output reg[`RegAddrBus] wd_o,

output reg wreg_o,

// The operation result of the instruction in the execution stage

input wire ex_wreg_i,

input wire[`RegBus] ex_wdata_i,

input wire[`RegAddrBus] ex_wd_i,

input wire[`AluOpBus] ex_aluop_i,

// The operation result of the instruction in the memory access stage

input wire mem_wreg_i,

input wire[`RegBus] mem_wdata_i,

input wire[`RegAddrBus] mem_wd_i,

output wire stallreq,

output reg next_inst_in_delayslot_o,// Whether the next instruction is a delay slot

output reg branch_flag_o,// Whether there is a transfer

output reg[`RegBus] branch_target_address_o,// Transfer to destination address

output reg[`RegBus] link_addr_o,// The return address of the transfer instruction to be saved

output reg is_in_delayslot_o,// Whether the currently decoded instruction is in the delay slot

output wire[`RegBus] inst_o ,// Newly added output interface

//input wire[`AluOpBus] ex_aluop_i,

//output wire stallreq

output wire[31:0] excepttype_o,// Collected exception information

output wire[`RegBus] current_inst_address_o// The address of the decoding stage instruction

);

wire[5:0] op = inst_i[31:26];

wire[4:0] op2 = inst_i[10:6];

wire[5:0] op3 = inst_i[5:0];

wire[4:0] op4 = inst_i[20:16];

wire[`RegBus] pc_plus_8;// Save the address of the second instruction after the instruction in the current decoding stage

wire[`RegBus] pc_plus_4;// Save the instruction address immediately following the instruction in the current decoding stage

wire[`RegBus] imm_sll2_signedext;// In the corresponding branch instruction offset Move two places to the left , Then the symbol is extended to 32 The value of a

reg[`RegBus] imm;

reg instvalid;

reg excepttype_is_syscall;// Whether it is a system call exception syscall

reg excepttype_is_eret;// Whether it is an exception return instruction

/*excepttype_o The lower eight bits of are reserved for external interrupts , The eighth digit indicates whether it is syscall Caused by instructions System call exception , The ninth bit indicates whether the exception is caused by an invalid instruction , The twelfth digit indicates whether it is eret Instructions eret An instruction can be considered a special exception -- Return exception */

assign excepttype_o = {

19'b0,excepttype_is_eret,2'b0,instvalid,excepttype_is_syscall,8'b0};

// Input signal pc_i Is the address of the instruction currently in the decoding phase

assign current_inst_address_o = pc_i;

assign stallreq = `NoStop;// Loading in implementation 、 The signal is assigned a value when the instruction is stored

assign imm_sll2_signedext = {

{

14{

inst_i[15]}},inst_i[15:0],2'b00};

//imm_sll2_signedext Corresponding to... In branch instruction offset Move two places to the left , Then the symbol is extended to 32 The value of a

assign pc_plus_8 = pc_i+8;

assign pc_plus_4 = pc_i+4;

assign stallreq = `NoStop;

assign inst_o = inst_i;// Instructions in the decoding stage

// Define a new variable Indicates the register to be read 1 Whether it exists with the previous instruction load relevant

reg stallreq_for_reg1_loadrelate;

// Define a new variable Indicates the register to be read 2 Whether it exists with the previous instruction load relevant

reg stallreq_for_reg2_loadrelate;

// Define a new variable Indicates whether the previous instruction is a load instruction

wire pre_inst_is_load;

// According to the input signal ex_aluop_i value Determine whether the previous instruction is a load instruction

// If it's a load instruction So set pre_inst_is_load by 1 Reverse 0

assign pre_inst_is_load = ((ex_aluop_i == `EXE_LB_OP)||

(ex_aluop_i == `EXE_LBU_OP)||

(ex_aluop_i == `EXE_LH_OP)||

(ex_aluop_i==`EXE_LHU)||

(ex_aluop_i==`EXE_LW_OP)||

(ex_aluop_i==`EXE_LWR_OP)||

(ex_aluop_i==`EXE_LWL_OP)||

(ex_aluop_i==`EXE_LL_OP)||

(ex_aluop_i==`EXE_SC_OP)) ? 1'b1 : 1'b0;

/* If the last instruction is a load instruction And the loading instruction to be loaded into the destination register is the current instruction To pass the Regfile Module read port 1 Read the general register , Then it means that there is load relevant */

// Set up stallreq_for_reg1_loadrelate by Stop

always @(*)begin

stallreq_for_reg1_loadrelate <= `NoStop;

if(rst == `RstEnable)begin

reg1_o <= `ZeroWord;

end else if(pre_inst_is_load == 1'b1 && ex_wd_i == reg1_addr_o && reg1_read_o == 1'b1)begin

stallreq_for_reg1_loadrelate <= `Stop;// There is load relevant Stop

end

end

//reg2 And reg1 Empathy

always @(*)begin

stallreq_for_reg2_loadrelate <= `NoStop;

if(rst == `RstEnable)begin

reg2_o <= `ZeroWord;

end else if(pre_inst_is_load == 1'b1 && ex_wd_i == reg2_addr_o && reg2_read_o == 1'b1)begin

stallreq_for_reg2_loadrelate <= `Stop;// There is load relevant Stop

end

end

assign stallreq = stallreq_for_reg1_loadrelate | stallreq_for_reg2_loadrelate;

always @ (*) begin

if (rst == `RstEnable) begin

aluop_o <= `EXE_NOP_OP;

alusel_o <= `EXE_RES_NOP;//nop

wd_o <= `NOPRegAddr;

wreg_o <= `WriteDisable;

instvalid <= `InstValid;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

reg1_addr_o <= `NOPRegAddr;

reg2_addr_o <= `NOPRegAddr;

imm <= 32'h0;

link_addr_o <= `ZeroWord;// The return address of the transfer instruction to be saved

branch_target_address_o <= `ZeroWord;// Transfer to destination address

branch_flag_o <= `NotBranch;// No transfer

next_inst_in_delayslot_o <= `NotInDelaySlot;// Whether the next instruction is in the delay slot

end else begin // Initialize first

aluop_o <= `EXE_NOP_OP;

alusel_o <= `EXE_RES_NOP;

wd_o <= inst_i[15:11];

wreg_o <= `WriteDisable;

instvalid <= `InstInvalid;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

reg1_addr_o <= inst_i[25:21];//rs

reg2_addr_o <= inst_i[20:16];//rt

imm <= `ZeroWord;

link_addr_o <= `ZeroWord;

branch_target_address_o <= `ZeroWord;

branch_flag_o <= `NotBranch;

next_inst_in_delayslot_o <= `NotInDelaySlot;

excepttype_is_syscall <= `False_v;// There is no system call exception by default

excepttype_is_eret <= `False_v;// Default is not eret Instructions

instvalid <= `InstInvalid;// Default invalid directive

case (op)// Instruction code

`EXE_SPECIAL_INST: begin // The instruction code is SPECIAL

case(op2)// Function code

5'b00000: begin

case(op3) // Judge which instruction it is according to the function code

`EXE_OR: begin //or R Type command rs|rt -> rd

wreg_o <= `WriteEnable;

aluop_o <= `EXE_OR_OP;

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_AND:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_AND_OP;//R rs&rt ->rd

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_XOR:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_XOR_OP;// R rs^rt ->rd

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_NOR:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_NOR_OP;// R rs~|rt ->rd

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SLLV:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLL_OP;

alusel_o <= `EXE_RES_SHIFT;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SRLV:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SRLV_OP;

alusel_o <= `EXE_RES_SHIFT;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SRAV:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SRAV_OP;

alusel_o <= `EXE_RES_SHIFT;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SYNC:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_NOP_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MFHI:begin// The special register hi The value of is assigned to the address rd The register of

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MFHI_OP;

alusel_o <= `EXE_RES_MOVE;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_MFLO:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MFLO_OP;

alusel_o <= `EXE_RES_MOVE;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_MTHI:begin//hi<-rs Write special registers

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MTHI_OP;

alusel_o <= `EXE_RES_MOVE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_MTLO:begin //lo<-rs Write special registers

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MTLO_OP;

reg1_read_o <= 1'b1;//rs

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_MOVN:begin// Judge rt Register value If not for 0 take rs The value is assigned to rd conversely rd The value remains the same

//wreg_o <= `WriteEnable;

aluop_o <= `EXE_MOVN_OP;

alusel_o <= `EXE_RES_MOVE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

//reg2_o The value of is the address rt The value of the register for

if(reg2_o != `ZeroWord)begin

wreg_o <= `WriteEnable;

end else begin

wreg_o <= `WriteDisable;

end

end

`EXE_MOVZ:begin // Judge rt Register value If it is 0 take rs The value is assigned to rd conversely rd The value remains the same

aluop_o <= `EXE_MOVZ_OP;

alusel_o <= `EXE_RES_MOVE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

if(reg2_o == `ZeroWord)begin

wreg_o <= `WriteEnable;

end else begin

wreg_o <= `WriteDisable;

end

end

`EXE_SLT:begin//slt Instructions rd<-(rs<rt)

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLT_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SLTU:begin //sltu Instructions

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLTU_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_ADD:begin//rd<-rs+rt

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADD_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_ADDU:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADDU_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SUB:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SUB_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SUBU:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SUBU_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MULT:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MULT_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MULTU:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MULTU_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_DIV:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_DIV_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_DIVU:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_DIVU_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_JR:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_JR_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;//rs Registers need to be used

reg2_read_o <= 1'b0;

wd_o <= inst_i[15:11];

link_addr_o <= pc_plus_8;// The return address

branch_target_address_o <= reg1_o;// Transfer to destination address

branch_flag_o <= `Branch;// Whether there is a transfer

next_inst_in_delayslot_o <= `InDelaySlot;// The next instruction is not in the delay slot

instvalid <= `InstValid;

end

`EXE_JALR:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_JALR_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

wd_o <= inst_i[15:11];

link_addr_o <= pc_plus_8;

branch_target_address_o <= reg1_o;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

instvalid <= `InstValid;

end

`EXE_TEQ:begin//teq

wreg_o <= `WriteDisable;

aluop_o <= `EXE_SYSCALL_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_TGE:begin//tge

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TGE_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_TGEU:begin//tgeu

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TGEU_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_TLT:begin//tlt

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TLT_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_TLTU:begin//tltu

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TLTU_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_TNE:begin//tne

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TNE_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_SYSCALL:begin//syscall

wreg_o <= `WriteDisable;

aluop_o <= `EXE_SYSCALL_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

excepttype_is_syscall <= `True_v;

end

default:begin

end

endcase

end

default:begin

//aluop_o <= `EXE_NOP_OP;

//alusel_o <= `EXE_RES_OP;

//wd_o <= `NOPRegAddr;

//wreg_o <= `WriteDisable;

//instvalid <= `InstValid;

//reg1_read_o <= `ReadDisable;

//reg2_read_o <= `ReadDisable;

//reg1_addr_o <= inst_i[25:21];

//reg2_addr_o <= inst_i[20:16];

end

endcase//op3

end // 5'b00000

`EXE_J:begin

wreg_o <= `WriteDisable;// Whether to write to the destination register in the decoding stage

aluop_o <= `EXE_J_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

link_addr_o <= `ZeroWord;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

instvalid <= `InstValid;

branch_target_address_o <= {

pc_plus_4[31:28],inst_i[25:0],2'b00};// The address of the transfer destination

end

`EXE_JAL:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_JAL_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

wd_o <= 5'b11111;// The address of the destination register to be written register $1

link_addr_o <= pc_plus_8;// The return address of the transfer instruction to be saved

branch_flag_o <= `Branch;// The sign of the transfer

next_inst_in_delayslot_o <= `InDelaySlot;

instvalid <= `InstValid;

branch_target_address_o <= {

pc_plus_4[31:28],inst_i[25:0],2'b00};

end

`EXE_BEQ:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_BEQ_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;// Need to compare rs And rt

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

if(reg1_o == reg2_o)begin // If rs Value reg1_o And rd Value reg2_o equal Transfer occurs

branch_target_address_o <= pc_plus_4 + imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

`EXE_BGTZ:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_BGTZ_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;//rs

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

if((reg1_o[31] == 1'b0)&&(reg1_o != `ZeroWord))begin

branch_target_address_o <= pc_plus_4 + imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

`EXE_BLEZ:begin

wreg_o <= `WriteDisable;// Whether to write to the destination register in the decoding stage

aluop_o <= `EXE_BLEZ_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

if((reg1_o[31] == 1'b1)&&(reg1_o != `ZeroWord))begin

branch_target_address_o <= pc_plus_4 + imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

`EXE_BNE:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_BNE_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

if(reg1_o != reg2_o)begin

branch_target_address_o <= pc_plus_4+imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

`EXE_REGIMM_INST:begin

case(op4)

`EXE_BLTZAL:begin//bltzal

wreg_o <= `WriteEnable;

aluop_o <= `EXE_BGEZAL_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

link_addr_o <= pc_plus_8;

wd_o <= 5'b11111;

instvalid <= `InstValid;

if(reg1_o[31] == 1'b1) begin//reg1_o<0

branch_target_address_o <= pc_plus_4+imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

`EXE_BLTZ:begin//bltz

wreg_o <= `WriteDisable;

aluop_o <= `EXE_BGEZAL_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

if(reg1_o[31] == 1'b1)begin

branch_target_address_o <= pc_plus_4 + imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

`EXE_BGEZ:begin//bgez

wreg_o <= `WriteDisable;

aluop_o <= `EXE_BGEZ_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

if(reg1_o[31] == 1'b0)begin//rs Is greater than or equal to 0

branch_target_address_o <= pc_plus_4 + imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

`EXE_BGEZAL:begin//bgezal

wreg_o <= `WriteEnable;

aluop_o <= `EXE_BGEZAL_OP;

alusel_o <= `EXE_RES_JUMP_BRANCH;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

link_addr_o <= pc_plus_8;

wd_o <= 5'b11111;

instvalid <= `InstValid;

if(reg1_o[31] == 1'b0)begin

branch_target_address_o <= pc_plus_4 + imm_sll2_signedext;

branch_flag_o <= `Branch;

next_inst_in_delayslot_o <= `InDelaySlot;

end

end

// Address is rs The value of the general-purpose register and the instruction 16 The bit immediate sign is extended to 32 Compare values after bits , If the two are equal , That causes a self trapping anomaly

`EXE_TEQI:begin //teqi

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TEQI_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

instvalid <= `InstValid;

end

`EXE_TGEI:begin //tegi

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TGEI_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

instvalid <= `InstValid;

end

`EXE_TGEIU:begin //teqi

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TGEIU_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

instvalid <= `InstValid;

end

`EXE_TLTI:begin //teqi

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TLTI_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

instvalid <= `InstValid;

end

`EXE_TLTIU:begin //teqi

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TLTIU_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

instvalid <= `InstValid;

end

`EXE_TNEI:begin //teqi

wreg_o <= `WriteDisable;

aluop_o <= `EXE_TNEI_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

instvalid <= `InstValid;

end

default:begin

end

endcase // op2

end

`EXE_ORI:begin //ORI Instructions

wreg_o <= `WriteEnable;

aluop_o <= `EXE_OR_OP;

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

16'h0, inst_i[15:0]}; // Count now 0 Expand

wd_o <= inst_i[20:16]; // Read rt Address

instvalid <= `InstValid;

end

`EXE_ANDI:begin //andi

wreg_o <= `WriteEnable;

aluop_o <= `EXE_AND_OP;

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

16'h0,inst_i[15:0]};

wd_o <= inst_i[20:16];//rt

instvalid = `InstValid;

end

`EXE_XORI:begin//xori

wreg_o <= `WriteEnable;

aluop_o <= `EXE_XOR_OP;

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

16'h0,inst_i[15:0]};

wd_o <= inst_i[20:16];

instvalid = `InstValid;

end

`EXE_LUI:begin//lui

wreg_o <= `WriteEnable;// Pay attention to the typographical errors in the book No more words

aluop_o <= `EXE_OR_OP;

alusel_o <= `EXE_RES_LOGIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

inst_i[15:0],16'h0};

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

/*`EXE_PREF: begin//pref wreg_o <= `WriteDisable; aluop_o <= `EXE_NOP_OP; alusel_o <= `EXE_RES_NOP; reg1_read_o <= 1'b0; reg2_read_o <= 1'b0; instvalid <= `InstValid; end */

`EXE_SLTI:begin //slti rt <- (rs < (sign_extended)immediate)

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLT_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_SLTIU:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLTU_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_ADDI:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADDI_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_ADDIU:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_ADDIU_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

imm <= {

{

16{

inst_i[15]}},inst_i[15:0]};

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_LB:begin// Write the loading result to the destination register

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LB_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;// The address used to calculate the loading target address is base The register value of

reg2_read_o <= 1'b0;

wd_o <= inst_i[20:16];// Destination register address

instvalid <= `InstValid;

end

`EXE_LBU:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LBU_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_LH:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LH_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_LHU:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LHU_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_LW:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LW_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_LWL:begin// Load left The loading result needs to be written to the destination register [20:16]

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LWL_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_LWR:begin// Load right

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LWR_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_SB:begin // There is no need to write general-purpose registers The address used to calculate the storage destination address is base The value of the register for

wreg_o <= `WriteDisable;

aluop_o <= `EXE_SB_OP;

reg1_read_o <= 1'b1; //[25:21] reg1_addr_o ======> base

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

alusel_o <= `EXE_RES_LOAD_STORE;

end

`EXE_SH:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_SH_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

alusel_o <= `EXE_RES_LOAD_STORE;

end

`EXE_SW:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_SW_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

alusel_o <= `EXE_RES_LOAD_STORE;

end

`EXE_SWL:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_SWL_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

alusel_o <= `EXE_RES_LOAD_STORE;

end

`EXE_SWR:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_SWR_OP;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

alusel_o <= `EXE_RES_LOAD_STORE;

end

`EXE_LL:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_LL_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_SC:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SC_OP;

alusel_o <= `EXE_RES_LOAD_STORE;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

wd_o <= inst_i[20:16];

instvalid <= `InstValid;

end

`EXE_SPECIAL2_INST:begin//(op)

case(op3)

`EXE_CLZ:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_CLZ_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_CLO:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_CLO_OP;

alusel_o <= `EXE_RES_ARITHMETIC;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

end

`EXE_MUL:begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_MUL_OP;

alusel_o <= `EXE_RES_MUL;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MADD:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_MADD_OP;

alusel_o <= `EXE_RES_MUL;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MADDU:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_MADDU_OP;

alusel_o <= `EXE_RES_MUL;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MSUB:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_MSUB_OP;

alusel_o <= `EXE_RES_MUL;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

`EXE_MSUBU:begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_MSUBU_OP;

alusel_o <= `EXE_RES_MUL;

reg1_read_o <= 1'b1;

reg2_read_o <= 1'b1;

instvalid <= `InstValid;

end

default:begin

end

endcase //EXE_SPECIAL_INST2 case

end

default:begin

end

endcase //case op

if(inst_i == `EXE_ERET)begin

wreg_o <= `WriteDisable;

aluop_o <= `EXE_ERET_OP;

alusel_o <= `EXE_RES_NOP;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

instvalid <= `InstValid;

excepttype_is_eret <= `True_v;

end

if(inst_i[31:21] == 11'b00000000000)begin //sll,srl,sra

if(op3 == `EXE_SLL) begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SLL_OP;

alusel_o <= `EXE_RES_SHIFT;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b1;

imm[4:0] <= inst_i[10:6];

wd_o <= inst_i[15:11];

instvalid <= `InstValid;

end else if(op3 == `EXE_SRL)begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SRL_OP;

alusel_o <= `EXE_RES_SHIFT;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b1;

imm[4:0] <= inst_i[10:6];

wd_o <= inst_i[15:11];

instvalid <= `InstValid;

end else if(op3 == `EXE_SRA) begin

wreg_o <= `WriteEnable;

aluop_o <= `EXE_SRA_OP;

alusel_o <= `EXE_RES_SHIFT;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b1;

imm[4:0] <= inst_i[10:6];

wd_o <= inst_i[15:11];

instvalid <= `InstValid;

end

end

//endcase

//end

// end else begin //if

if(inst_i[31:21]==11'b010_0000_0000&&inst_i[10:0]==11'b000_0000_0000)//mfc0 Instructions

begin

aluop_o <= `EXE_MFC0_OP;

alusel_o <= `EXE_RES_MOVE;// A mobile operation

wd_o <= inst_i[20:16];//rt The destination register to be written is in the instruction rt Value

wreg_o <= `WriteEnable;// Read required CP0 The value of the register in is written to the destination register , To write a general-purpose register

instvalid <= `InstValid;

reg1_read_o <= 1'b0;

reg2_read_o <= 1'b0;

end else if(inst_i[31:21]==11'b010_0000_0100&&inst_i[10:0]==11'b00000000000)//mtc0 Instructions

begin

aluop_o <= `EXE_MTC0_OP;

alusel_o <= `EXE_RES_MOVE;

wreg_o <= `WriteDisable;// There is no need to write general-purpose registers

instvalid <= `InstValid;

reg1_read_o <= 1'b1;// Need to read the general register adopt Regfile1 The port reads data

reg1_addr_o <= inst_i[20:16];// The read address is in the instruction 16-20 position yes rt Value

reg2_read_o <= 1'b0;

end

end //if

end //always

/* Data push forward to reg1_o The assignment process adds two cases 1: If Regfile Module read port 1 The register to be read is the destination register to be written at the execution stage , Then, the results of the execution phase ex_wdata_i As reg1_o Value 2: If Regfile Module read port 1 The register to be read is the destination register to be written in the memory access stage , Then, the results of the storage access stage mem_wdata_i As reg1_o Value */

always @ (*) begin

if(rst == `RstEnable) begin

reg1_o <= `ZeroWord;

end else if((reg1_read_o == 1'b1) && (ex_wreg_i == 1'b1)

&& (ex_wd_i == reg1_addr_o)) begin

reg1_o <= ex_wdata_i;

end else if((reg1_read_o == 1'b1) && (mem_wreg_i == 1'b1)

&& (mem_wd_i == reg1_addr_o)) begin

reg1_o <= mem_wdata_i;

end else if(reg1_read_o == 1'b1) begin

reg1_o <= reg1_data_i;

end else if(reg1_read_o == 1'b0) begin

reg1_o <= imm;

end else begin

reg1_o <= `ZeroWord;

end

end

always @ (*) begin

if(rst == `RstEnable) begin

reg2_o <= `ZeroWord;

end else if((reg2_read_o == 1'b1) && (ex_wreg_i == 1'b1)

&& (ex_wd_i == reg2_addr_o)) begin

reg2_o <= ex_wdata_i;

end else if((reg2_read_o == 1'b1) && (mem_wreg_i == 1'b1)

&& (mem_wd_i == reg2_addr_o)) begin

reg2_o <= mem_wdata_i;

end else if(reg2_read_o == 1'b1) begin

reg2_o <= reg2_data_i;

end else if(reg2_read_o == 1'b0) begin

reg2_o <= imm;

end else begin

reg2_o <= `ZeroWord;

end

end

// Output variables is_in_delayslot_o Indicates whether the instruction in the current decoding stage is a delay slot instruction

always @ (*)begin

if(rst == `RstEnable)begin

is_in_delayslot_o <= `NotInDelaySlot;

end else begin

// Directly equal to is_in_delayslot_i

is_in_delayslot_o <= is_in_delayslot_i;

end

end

endmodule

id_ex.v

`include "define.v"

// On the rising edge of the clock cycle , Pass the result of the decoding stage to the execution stage */

module id_ex(

input wire clk,

input wire rst,

input wire flush,

// The last chapter , The signal transmitted from the decoding stage

input wire[`RegBus] id_current_inst_address,

input wire[31:0] id_excepttype,

// Information transmitted from the decoding stage

input wire[`AluOpBus] id_aluop,

input wire[`AluSelBus] id_alusel,

input wire[`RegBus] id_reg1,

input wire[`RegBus] id_reg2,

input wire[`RegAddrBus] id_wd,

input wire id_wreg,

// Information from the control module

input wire[5:0] stall ,

input wire[`RegBus] id_link_address,

input wire id_is_in_delayslot,

input wire next_inst_in_delayslot_i,

input wire[`RegBus] id_inst, // come from id The signal of the module Instructions currently in the decoding stage

// Information passed to the execution phase

output reg[`AluOpBus] ex_aluop,

output reg[`AluSelBus] ex_alusel,

output reg[`RegBus] ex_reg1,

output reg[`RegBus] ex_reg2,

output reg[`RegAddrBus] ex_wd,

output reg ex_wreg,

output reg[`RegBus] ex_link_address,

output reg ex_is_in_delayslot,

output reg is_in_delayslot_o,

output reg[`RegBus] ex_inst ,// Pass on to ex modular Instructions currently in execution

// The last chapter New interface Signals passed to the execution phase

output reg[`RegBus] ex_current_inst_address,

output reg[31:0] ex_excepttype

);

always @ (posedge clk) begin

if (rst == `RstEnable) begin

ex_aluop <= `EXE_NOP_OP;

ex_alusel <= `EXE_RES_NOP;

ex_reg1 <= `ZeroWord;

ex_reg2 <= `ZeroWord;

ex_wd <= `NOPRegAddr;

ex_wreg <= `WriteDisable;

ex_link_address <= `ZeroWord;

ex_is_in_delayslot <= `NotInDelaySlot;

ex_inst <= `ZeroWord;

ex_excepttype <= `ZeroWord;

ex_current_inst_address <= `ZeroWord;

end else if(flush == 1'b1) begin// Clear the pipeline

ex_aluop <= `EXE_NOP_OP;

ex_alusel <= `EXE_RES_NOP;

ex_reg1 <= `ZeroWord;

ex_reg2 <= `ZeroWord;

ex_wd <= `NOPRegAddr;

ex_wreg <= `WriteDisable;

ex_excepttype <= `ZeroWord;

ex_link_address <= `ZeroWord;

ex_inst <= `ZeroWord;

ex_is_in_delayslot <= `NotInDelaySlot;

is_in_delayslot_o <= `NotInDelaySlot;

ex_current_inst_address <= `ZeroWord;

end else if(stall[2] == `Stop && stall[3] == `NoStop)begin// Execute stop memory access and continue

ex_aluop <= `EXE_NOP_OP;

ex_alusel <= `EXE_RES_NOP;

ex_reg1 <= `ZeroWord;

ex_reg2 <= `ZeroWord;

ex_wd <= `NOPRegAddr;

ex_wreg <= `WriteDisable;

ex_link_address <= `ZeroWord;

ex_is_in_delayslot <= `NotInDelaySlot;

ex_inst <= `ZeroWord;

ex_excepttype <= `ZeroWord;

ex_current_inst_address <= `ZeroWord;

end else if(stall[2] == `NoStop)begin// Implementation continues

ex_aluop <= id_aluop;

ex_alusel <= id_alusel;

ex_reg1 <= id_reg1;

ex_reg2 <= id_reg2;

ex_wd <= id_wd;

ex_wreg <= id_wreg;

ex_link_address <= id_link_address;

ex_is_in_delayslot <= id_is_in_delayslot;

ex_inst <= id_inst;

is_in_delayslot_o <= next_inst_in_delayslot_i;

ex_excepttype <= id_excepttype;

ex_current_inst_address <= id_current_inst_address;

/*end else begin ex_aluop <= id_aluop; ex_alusel <= id_alusel; ex_reg1 <= id_reg1; ex_reg2 <= id_reg2; ex_wd <= id_wd; ex_wreg <= id_wreg; end*/

end

end

endmodule

ex.v

`include "define.v"

//ex.v Perform module

module ex(

// The information sent from the decoding stage to the execution stage

input wire[`AluOpBus] aluop_i,

input wire[`AluSelBus] alusel_i,

input wire[`RegBus] reg1_i,

input wire[`RegBus] reg2_i,

input wire[`RegAddrBus] wd_i,

input wire wreg_i,

input wire rst,

//HILO Module given HI,LO Register value

input wire[`RegBus] hi_i,

input wire[`RegBus] lo_i,

// Whether the instruction in the write back phase should be written HI,LO, Used to detect HI,LO Register related data problems

input wire[`RegBus] wb_hi_i,

input wire[`RegBus] wb_lo_i,

input wire wb_whilo_i,

// Whether to write the instruction in the memory access stage HI,LO, Used to detect HI,LO Register related data problems

input wire[`RegBus] mem_hi_i,

input wire[`RegBus] mem_lo_i,

input wire mem_whilo_i,

// Added input port

input wire[`DoubleRegBus] hilo_temp_i,// Save the result of multiplication

input wire[1:0] cnt_i,// Which cycle is in the implementation stage

// Add input from division module

input wire[`DoubleRegBus] div_result_i,

input wire div_ready_i,

// The return address to be saved for the branch instruction in the execution stage

input wire[`RegBus] link_address_i,

// Whether the instruction in the current execution stage is in the delay slot

input wire is_in_delayslot_i,

// New input port inst_i, Its value is the instruction currently in execution

input wire[`RegBus] inst_i,// Instructions currently in execution

// Whether to write the instruction in the memory access stage CP0 Register in Used to detect data correlation

input wire mem_cp0_reg_we,

input wire[4:0] mem_cp0_reg_write_addr,

input wire[`RegBus] mem_cp0_reg_data,

// Whether the instruction in the write back phase should be written CP0 Register in It is also used to detect data correlation

input wire wb_cp0_reg_we,

input wire[4:0] wb_cp0_reg_write_addr,

input wire[`RegBus] wb_cp0_reg_data,

// And CP0 Direct connection Used to read the value of the specified register

input wire[`RegBus] cp0_reg_data_i,

// The input interface added in the last chapter

input wire[31:0] excepttype_i,

input wire[`RegBus] current_inst_address_i,

output reg[4:0] cp0_reg_read_addr_o,

// Pass to the next stage of the pipeline Used to write CP0 The value of the specified register

output reg cp0_reg_we_o,

output reg[4:0] cp0_reg_write_addr_o,

output reg[`RegBus] cp0_reg_data_o,

// In the execution phase, the instruction pair LO,HI Register write request

output reg[`RegBus] hi_o,

output reg[`RegBus] lo_o,

output reg whilo_o,

// Results of execution

output reg[`RegAddrBus] wd_o,

output reg wreg_o,

output reg[`RegBus] wdata_o,

output reg stallreq,

output reg[`DoubleRegBus] hilo_temp_o,

output reg[1:0] cnt_o,

// The output added to the division module

output reg[`RegBus] div_opdata1_o,

output reg[`RegBus] div_opdata2_o,

output reg div_start_o,

output reg signed_div_o,

//output reg is_in_delayslot_o,

// The following new output interfaces are for load 、 Storage instruction preparation

output wire[`AluOpBus] aluop_o, // The subtype to be calculated at the execution stage

output wire[`RegBus] mem_addr_o,// Load the memory address corresponding to the storage instruction

output wire[`RegBus] reg2_o,// Store the data to be stored by the instruction , perhaps lwl,lwr The address of the destination register to which the instruction is to be loaded

// The output port added in the last chapter

output wire[31:0] excepttype_o,

output wire[`RegBus] current_inst_address_o,

output wire is_in_delayslot_o

);

// Save the result of logical operation

reg[`RegBus] logicout;

// Save the result of the shift operation

reg[`RegBus] shiftres;

// Save the result of the move operation