当前位置:网站首页>Jesd204b debugging notes (practical version)

Jesd204b debugging notes (practical version)

2022-07-27 13:13:00 【51CTO】

This article is an original article by Ming Deyang , Reprint please indicate the source !

During the functional commissioning of the project , Yes AD9144,AD9516 Parameter configuration is very important and essential , The following problems have been encountered in this process .

One 、 problem 1

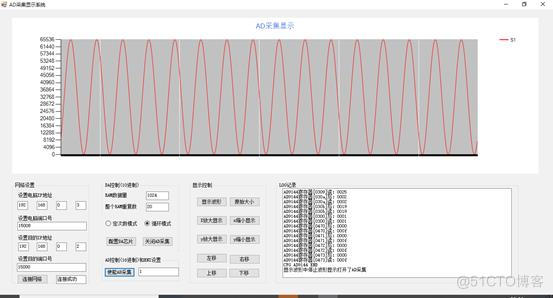

When we use the upper computer software to configure, we find that the upper computer log There are write parameters but no read parameters in the record , There are two possibilities for this problem , First, the parameters are not written in, so the parameters read out are 0, Second, it was written in, but there was an error reading the parameters .

As shown in the figure :

In this regard, we doubt whether there is a problem with network communication , The inspection found that PC And FPGA Gigabit Network indicator of the connected network port

It doesn't light up, but the 100m network is lit up .

Check the network configuration and find that the connection speed of the network is only 100m , Unable to use gigabit network transmission , That is, computers do not support Gigabit Networks .

There are two solutions , First, replace the computer host , The second is to change the program again and set it as 100m network transmission .

This time we choose method one , Replace PC Retest the host and find AD9144,AD9516 The configuration can read and write normally ,

So the reason for this problem is PC And FPGA Network interface mismatch .

Two 、 problem 2

It's going on AD9144,AD9516 After register configuration , download bit Stream file to FPGA after , Observe with an oscilloscope AD9144 The output signal , No waveform output found , use Vivado Grab the signal and observe , Find out sync and tx_tready The signal is always low and not high , That is to say AD9144 And jesd204b Not synchronized .

There are many reasons why synchronization is not possible , It can be roughly divided into hardware problems 、 Clock relation problem 、 Register configuration problem , First, remove the hardware problem .

Analyze the clock relationship , It is found that there is no error in the numerical calculation result of clock theory , Please check the detailed analysis steps by yourself 《 Description of clock relationship 》.

Check according to the theoretical value of clock relationship JESD204B Of IP Nuclear settings , No mistakes found .

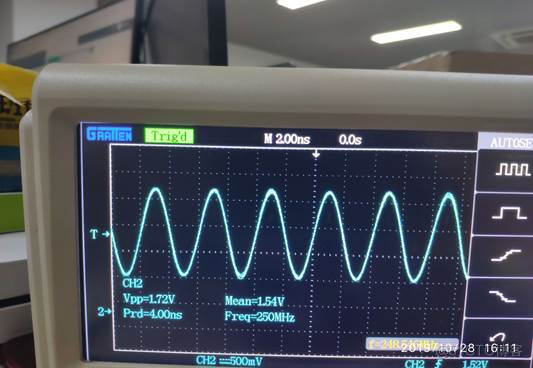

Check with an oscilloscope FPGA To AD9516 The frequency division clock of is found to be undetectable , Check the schematic diagram and locate the corresponding pin , Find out FPGA The transmitted clock is too large and overclocking , The oscilloscope cannot detect the signal , By looking for AD9516 It is found that the maximum value of the source clock used for frequency division is 250MHZ, After the AD9516 The source clock is set to 250MHZ, It can also be tested normally with an oscilloscope .

250MHZ Clock source :

By analyzing the clock in the program, it is found that the clock used by the data generation module is 62.5MHZ, And used to drive JESD204B The clock of the module is device_clock=125MHZ, Because data generation and data transmission are synchronized , So the clock doesn't match , take 62.5MHZ Change it to 125MHZ.

contrast JESD204B Of IP Register configuration data provided by kernel manual , No errors found .

JESD204B Of IP Nuclear parameters :

see AD9144 Register configuration manual , find AD9144 The synchronization signal indicates 0X470,0X471,0X472,0X473

They respectively represent code group synchronization signals, namely synchronization K code , Frame synchronization signal check kernel Check Flag , Initial channel synchronization signal .

Then observe the configuration process through the configuration of the upper computer again and find that other register values can be read and written normally , And this 4 The read value of registers is 0, That means there is no problem with the hardware , It is most likely that there is an error in register configuration .

Synchronous indication register :

Look up AD9144,AD9516 The manual found AD9516 The register of 0X232 The write value of should be 1, however AD9516 The reference value given by the configuration software of is 0, Therefore, it can be successfully configured after changing the register value .

Register configuration :

After successful configuration, it is shown in the following figure :

3、 ... and 、 problem 3

After solving the configuration problem , For testing vivado The observation of sync,tx_tready The signal found that the signal had been pulled high , also tx_data There are values , explain AD9144 And JESD204B It's synchronized .

Signal after synchronization :

But I'm using an oscilloscope to observe AD9144 When simulating the waveform of, it is found that the waveform deviates from the expected , Look up AD9144 and JESD204B Smooth and combine vivado Of vio Function to debug data online , It is found that the mode of digital to analog conversion is 16 The complement of hexadecimal corresponds to , After readjusting the data , The output waveform is consistent with the expectation , Finish debugging .

Abnormal waveform (125MHZ):

Normal waveform (31.25MHZ):

These are the problems encountered during debugging , Here is a summary to share with you , Welcome to discuss each other in the comments .

边栏推荐

- Gartner 权威预测未来4年网络安全的8大发展趋势

- MySQL扩展

- 【表达式计算】双栈 : 表达式计算问题的通用解法

- js日期时间格式化(年月日、时分秒、星期、季度、获取时间差、日期与时间戳转换的功能)

- Detail the construction methods, attributes and common methods in reflection

- Article reproduction: srcnn

- 时间工具类,得到当前时间,date转string

- 堆

- 592. 分数加减运算 : 表达式计算入门题

- flinksql从Oracle同步数据到Doris,一共50几个字段,Oracle表中3000多万条

猜你喜欢

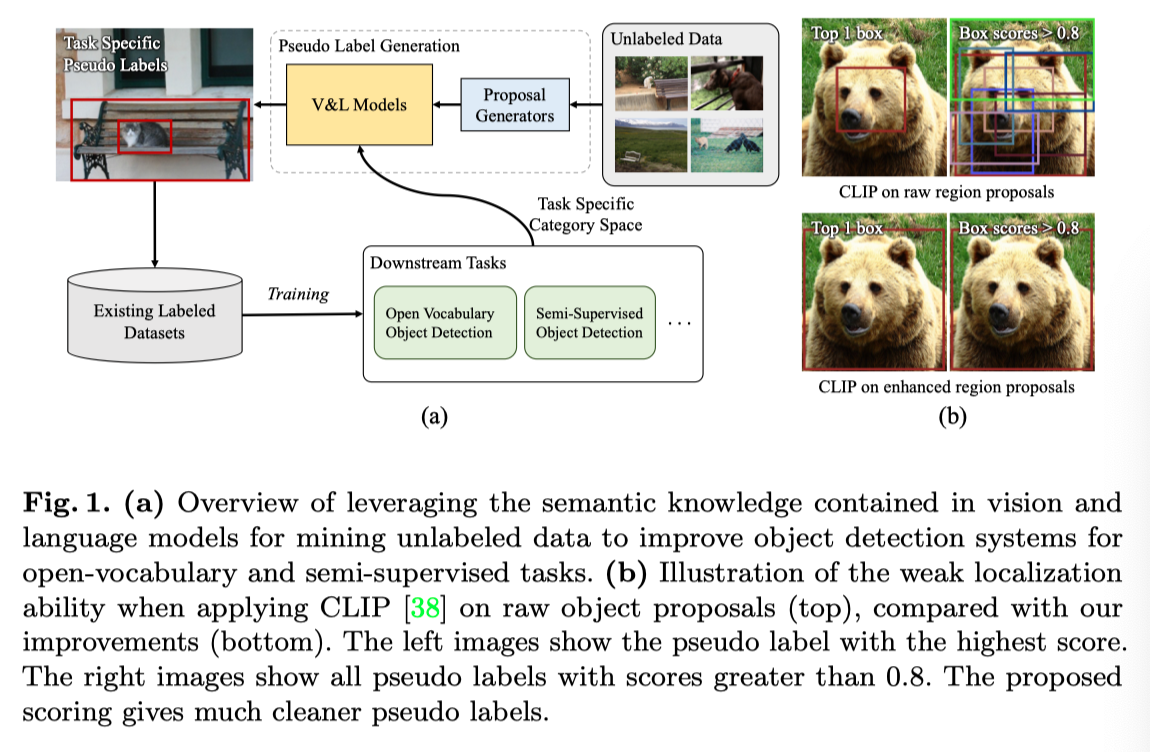

ECCV2022 | RU&谷歌提出用CLIP进行zero-shot目标检测!

What should I do if I can't see any tiles on SAP Fiori launchpad?

II. Analysis of the execution process of make menuconfig

Security measures for tcp/ip protocol vulnerabilities

Aike AI frontier promotion (7.27)

Mixin\ plug in \scoped style

Xposed+fdex2 app shelling (black cat complains about app shelling)

Set接口

Why does the class annotated with @configuration generate cglib proxy?

ArrayList常用方法总结

随机推荐

592. 分数加减运算 : 表达式计算入门题

为什么需要外键?

HDU1698_ Just a Hook

How can the top 500 enterprises improve their R & D efficiency? Let's see what industry experts say!

js日期时间格式化(年月日、时分秒、星期、季度、获取时间差、日期与时间戳转换的功能)

最新版泛域名证书申请

Keil mdk5.37 and above can add AC5 (armcc) compiler by themselves

延迟队列DelayQueue性能测试

Isolation level

Error: the source of the existing CacheManager is: urlconfigurationsource

Poj1273 drainage ditches [maximum flow] [SAP]

Overview of static inner classes and non static inner classes

Flinksql synchronizes data from Oracle to Doris, with a total of more than 50 fields and more than 30 million entries in Oracle tables

The sparksubmit. Main () method submits external parameters and remotely submits the standalone cluster task

Minimally invasive brain science broke the listing: the company's market value is HK $14.3 billion, and minimally invasive medical is the major shareholder

【萌新解题】斐波那契数列

Enjoy the luxury meta universe louis:the game, and participate in the NFT series digital collection white roll activity | tutorial

Connotative quotations

Xposed+fdex2 app shelling (black cat complains about app shelling)

改变线程状态的方法