当前位置:网站首页>Aurora 8b10b IP use - 02 - IP function design skills

Aurora 8b10b IP use - 02 - IP function design skills

2022-06-21 06:06:00 【Vuko wxh】

Préface

Entreprendre ce qui précède,Le présent document porte principalement sur:IPExemples d'utilisation de méthodes et de techniques de configuration pour certaines fonctions du noyau,Référence principaleIPContenu du chapitre III du manuel.

Réinitialisation et coupure de courant

Réinitialiser

Le signal de Réinitialisation est utilisé pour réinitialiser Aurora 8B/10B Le noyau est défini à un état de démarrage connu. Lors de la réinitialisation,Le noyau arrête toute opération en cours et réinitialise un nouveau canal.

Sur un module duplex complet,Réinitialiser le signal réinitialiser le canal TX Et RX Fin.Sur le module simplex,tx_system_reset Réinitialiser TX Accès,Et rx_system_reset Réinitialiser RX Accès. gt_reset Transmetteur de Réinitialisation du signal,Réinitialisation finale du noyau.tx_system_reset Utilisé sur l'interface avec la bande latérale simplex tx_reset Et rx_reset Les signaux sont séparés.

Exemple

Réinitialiser l'assertion dans le noyau duplex

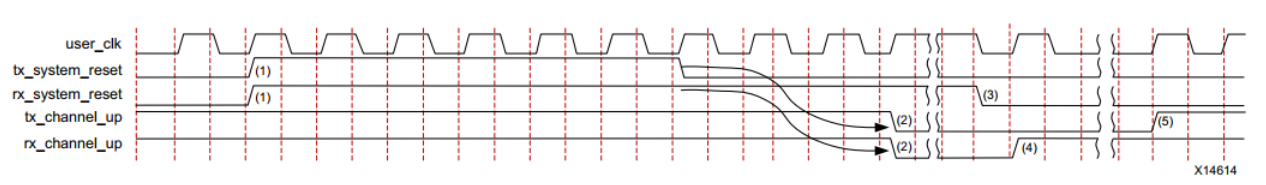

Il doit y avoir au moins six assertions de Réinitialisation dans le noyau duplex user_clk Période de temps. Donc,,channel_up En trois user_clk Faible après le cycle,Comme le montre la figure ci - dessous.

Dans le noyau duplex gt_reset Assertion

L'image suivante montre gt_reset Assertion, Il devrait y en avoir au moins six init_clk_in Période de temps. Donc,,user_clk Arrêt après plusieurs cycles d'horloge , Parce qu'il n'y a pas d'émetteur - récepteur txoutclk Et channel_up Puis il a été abaissé .

Dans le noyau simplex tx_system_reset Et rx_system_reset Assertion

La figure ci - dessous montre le simplex connecté dans le système TX Noyau et simplex RX Noyau.TX_IP Et RX_IP Peut être sur le même ou plusieurs appareils .

L'image suivante montre le noyau simplex tx_system_reset Et rx_system_reset Processus de recommandation assermenté .

- tx_system_reset Et rx_system_reset Réglé à au moins six horloges user_clk Période de temps.

- tx_channel_up Et rx_channel_up En trois user_clk Faible après le cycle.

- rx_system_reset A été abaissé (Ou)In tx_system_reset Relâchez après avoir été abaissé . Cela garantit un travail simple TX L'émetteur - récepteur dans le noyau a commencé à transmettre les données d'initialisation plus tôt , Et augmente le simplex RX Possibilité d'aligner le noyau sur la séquence de données correcte .

- rx_channel_up In tx_channel_up L'affirmation a été faite avant . Simplex RX Le noyau doit satisfaire à cette condition ,Simplex TX Paramètres du minuteur simplex dans le noyau (C_ALIGNED_TIMER、C_BONDED_TIMER Et C_VERIFY_TIMER) Des ajustements sont nécessaires pour satisfaire à ce critère .

- Quand simplex-TX Le noyau est terminé dans le temps configuré Aurora 8B/10B Lors de l'initialisation d'un transfert de séquence par un canal de protocole ,tx_channel_up En position. tx_channel_up last L'affirmation de simplex-TX Le noyau simplex-RX Envoyer quand le noyau est prêt Aurora Séquence d'initialisation.

Aurora 8B/10B Duplex Power On Sequence( Séquence d'alimentation duplex )

Pendant la séquence d'alimentation de la plaque ,gt_reset Et reset Les signaux doivent être de haut niveau . Horloge de référence de l'émetteur - récepteur (GT_REFCLK) Et l'horloge libre du noyau (INIT_CLK) On s'attend à ce qu'il reste stable pendant l'alimentation ,Pour que Aurora 8B/10B Le noyau fonctionne correctement .

Aurora 8B/10B Duplex Normal Operation Reset Sequence( Séquence de Réinitialisation du fonctionnement normal duplex )

En fonctionnement normal, Le signal de Réinitialisation est attendu à gt_reset Régler au moins avant de régler le signal 128 - Oui. user_clk Période de temps, Pour s'assurer que la partie du noyau de la logique programmable atteint un état de Réinitialisation connu Ingt_reset L'affirmation de user_clk Avant le signal,Comme suit.

Aurora 8B/10B Simplex Power On Sequence( Séquence d'alimentation simplex )

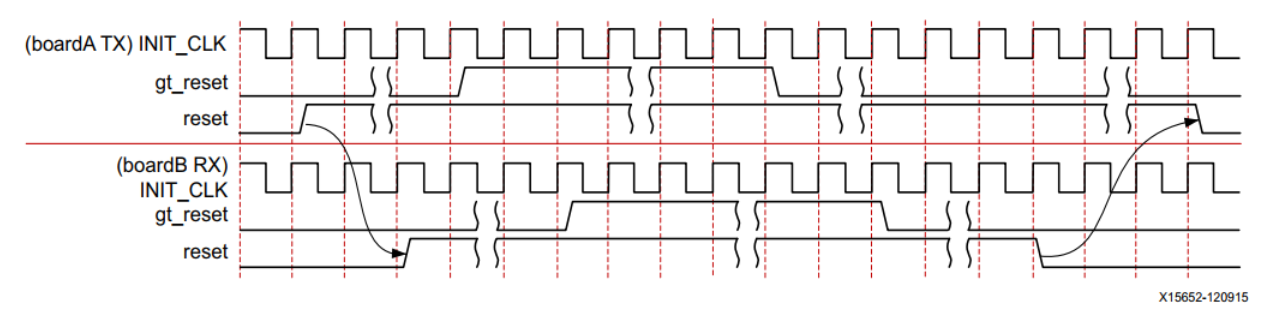

Pendant l'alimentation ,TX simplex Et RX simplex Du noyau gt_reset Et reset Le signal devrait être élevé . Prévisions INIT_CLK Et GT_REFCLK Stable pendant l'alimentation . Il faut d'abordTXOn Boardgt_resetSignal bas,Et ensuite,RXFingt_resetBaisse.; Cela garantit que RX Verrouillage latéral correct CDR,Comme le montre la figure ci - dessous.

Séquence d'alimentation simplex :

Release TX Fin gt_reset (A)

Release RX Fin gt_reset

Release RX Fin synchronisée à user_clk (D)

Release TX Fin synchronisée à user_clk (B)

Attention!: Il faut veiller à ce que (D) À (B) La différence de temps entre .

Aurora 8B/10B Simplex Normal Operation Reset Sequence( Séquence de Réinitialisation du fonctionnement normal simplex )

Pour les configurations simplex ,Suggestion TX La séquence de Réinitialisation latérale correspond à RX La séquence de Réinitialisation latérale est étroitement couplée ,Parce que TX Et RX Le lien n'a pas de chemin de rétroaction de communication . Votre attention, s'il vous plaît.,Si RX L'extrémité est réinitialisée , Il n'y a pas de mécanisme direct pour informer TX Réinitialisation du terminal . Donc,,Pour Aurora 8B/10B Noyau simplex , Le couplage de Réinitialisation doit être traité au niveau du système . Chaque fois TX La Réinitialisation latérale doit être suivie de RX Side,Comme le montre la figure ci - dessous,RX Réinitialisation latérale invalide et TX Le temps entre la Réinitialisation latérale invalide doit être aussi court que possible . En position gt_reset Avant,Au moins 128 Cycles d'horloge,Pour s'assurer que gt_reset Inhibition de la position user_clk Avant, La partie du noyau de la logique programmable atteint un état de Réinitialisation connu . gt_reset Le temps d'affirmation doit être d'au moins six init_clk Période de temps, Pour satisfaire le circuit de déjitter contenu dans le noyau .

Coupure de courant

C'est un signal efficace de haut niveau . AssertionpowerdownHeure,Aurora 8B/10B L'émetteur - récepteur dans le noyau s'éteindra , Mettez - les hors service 、Mode de faible puissance. Annuler l'assertion en cas de panne de courant , Le noyau se réinitialise automatiquement . gt_reset Il doit êtrepowerdown Position arrière position arrière .

Shared Logic(Logique partagée)

Vivado IDE L'option logique partagée dans configure le noyau pour inclure des ressources partageables , Par exemple, un émetteur - récepteur à quatre canaux PLL (QPLL)、 Différence d'émetteur - récepteur refclk Tampon (IBUFDS_GTE2), Et l'horloge et la logique de Réinitialisation dans le noyau ou l'exemple de conception .

La hiérarchie logique partagée s'appelle <component_name>_support. Fig. 3-9 Et des graphiques 3-10 Montre deux hiérarchies , Où les blocs logiques partagés sont contenus dans le noyau ou dans la conception de l'échantillon . La différence entre les deux niveaux réside dans les limites du noyau . Il utilise VivadoDans Shared Logic Options pour le contrôle . Quand la logique partagée est dans le noyau ,Single Ended L'option exclura le tampon d'horloge différentielle approprié du noyau .

Le contenu de la logique partagée dépend de l'interface physique et de l'appareil cible . La logique partagée contient le tampon différentiel de l'émetteur - récepteur (IBUFDS_GTE2/IBUFDS_GTE3) Exemples、 Prise en charge de la logique de Réinitialisation et <USER_COMPONENT_NAME:>_CLOCK_MODULE Instanciation de. La logique partagée contient également une instance publique de l'émetteur - récepteur basée sur le type d'émetteur sélectionné GTPE2_COMMON、GTXE2_COMMON Ou GTHE2_COMMON. Prise en charge de la logique de Réinitialisation contient pour réinitialiser et gt_reset La logique de déjitter du port .

Aurora 8B/10B Utilisation du noyau CPLL,Non utilisé QPLL(C'est - à - dire: GTXE2_COMMON/GTHE2_COMMON). QPLL Pour Zynq-7000 Et 7 Série de dispositifs, Et l'instancier dans une logique partagée , Pour s'aligner sur les autres noyaux Serial Connect de cylindre .

Le tableau suivant énumère les ressources partagées pour chaque série .

Sharable Resources

| Transceiver Type used in the Aurora 8B/10B Core | Resources |

|---|---|

| Zynq-7000 and 7 series device GTX/GTH/GTP transceivers in 2-byte mode | IBUFDS_GTE2: transceiver reference clock GT*_COMMON: transceiver clocking; BUFG: clocking IBUFDS: init_clk |

| Zynq-7000 and 7 series device GTX/GTH/GTP transceivers in 4-byte mode | IBUFDS_GTE2: transceiver reference clock GT*_COMMON: transceiver clocking MMCM: clocking 2xBUFG: clocking; IBUFDS: init_clk |

| UltraScale GTH Transceivers | IBUFDS_GTE3: transceiver reference clock BUFG_GT: clocking |

| UltraScale+ GTH Transceivers | IBUFDS_GTE4: transceiver reference clock BUFG_GT: clocking |

gt_refclk1_out Et gt_refclk2_out Le signal peut être partagé par d'autres émetteurs - récepteurs dans la conception , Et le Guide d'horloge de l'émetteur - récepteur doit être suivi pour la connectivité et la proximité à quatre canaux de l'émetteur - récepteur .Fig. 3-11 Afficher à partir du noyau contenant la logique partagée (aurora_8b10b_0) Vers une autre instance du noyau qui ne contient pas de logique partagée (aurora_8b10b_1) Connexion de ressources partageables pour . Certains ports peuvent varier en fonction de la configuration du noyau et du type d'émetteur - récepteur sélectionné .

Using the Scrambler/Descrambler( Utilisation d'un spoiler / Disjoncteur )

Un 16 Brouilleur de bits / Disjoncteur , Pour les données avec des polynômes :G(x) = X16 + X5 + X4 + X3 + 1,Oui. < component name>_scrambler.v[hd] Obtenir Module. Il garantit qu'il n'y aura pas de données en double pendant longtemps . Le brouilleur et le disjoncteur sont synchronisés en fonction de l'envoi et de la réception des caractères de compensation de l'horloge respectivement . Le spoiler n'affecte que les symboles de données .

Utiliser CRC

Mise en œuvre pour les données utilisateur 16 Bits ou 32 Bits CRC In < component name>_crc_top.v[hd] Disponible dans le module.

Pour 2 Byte Design Generation CRC16,Pour 4 Byte Design Generation CRC32. crc_valid Et crc_pass_fail_n Le signal indique la réception de CRC Et envoyé CRC Les résultats de. CRC-CCITT (16’h1021) Et le polynôme Ethernet standard (32’h04C11DB7) Utilisé séparément 16 Bits et 32 Bitwise CRC Polynôme.CRC Est calculé par canal , Avec les données comme suffixe . Au récepteur AXI Interface Division,CRC Supprimé, Les paquets de données suivent le AXI Mode d'envoi reçu par l'interface . L'image ci - dessous montre comment on peut CRC Envoyer le même paquet avec et quand activer CRC Options.

Logique d'échange à chaud

Aurora 8B/10B Hot swap Logic in ( En utilisant des init_clk Signal) Caractères de compensation de l'horloge reçus . Aurora RX L'interface reçoit un caractère de compensation d'horloge indiquant que le canal de communication est actif et non interrompu . Si le caractère de compensation de l'horloge n'est pas reçu dans un délai prédéterminé , La logique Hot swap réinitialisera le noyau et l'émetteur - récepteur . Le module de compensation de l'horloge doit être utilisé pour Aurora 8B/10B Conception.

Compensation de l'horloge

La fonction de compensation de l'horloge permet de Aurora 8B/10B La fréquence d'horloge de référence utilisée de chaque côté du canal varie jusqu'à ±100ppm. Selon Aurora 8B/10B Spécification du Protocole , Générer un module de compensation d'horloge standard en utilisant le noyau <component_name>_standard_cc_module.v[hd].

standard_cc_module Traitement du cycle de génération des caractères de compensation de l'horloge , Comme indiqué dans le tableau ci - dessous . Peut être utilisé CC_FREQ_FACTOR Contrôle de la périodicité .

| Lane Width | DO_CC Entre USER_CLK Cycle | DO_CC Durée(USER_CLK Cycle) |

|---|---|---|

| 2 | 5,000 | 6 |

| 4 | 2,500 | 3 |

Prévention 16 Octets UFC Le nombre de cycles préalables requis pour que le message entre en conflit avec la séquence de compensation de l'horloge dépend du nombre de canaux dans le canal et de la largeur de chaque canal . Pendant la transmission des caractères de compensation de l'horloge , La demande de message de contrôle de flux natif n'a pas été confirmée . Cela aide à prévenir NFC Conflit entre le message et la séquence de compensation de l'horloge .Paramètres CC_FREQ_FACTOR C'est sûr. CC Fréquence de la séquence . .Toute tentative d'augmenter ou de diminuer les paramètres doit être soigneusement analysée et testée .

Assurez - vous que la durée et la période choisies sont suffisantes pour corriger la différence maximale entre les fréquences d'horloge utilisées . N'effectuez pas plus d'une séquence de correction d'horloge sur les huit cycles de l'autre .AvecCC La séquence remplace la longue séquence inactive (>12 Cycles)Peut être abaisséEMI.

En utilisant le support de petite extrémité

Aurora 8B/10B Le noyau prend en charge par défaut l'interface utilisateur dans le grand format . Il prend également en charge les formats de petites extrémités pour se connecter de façon transparente aux AXI4-Stream De IP Noyau.

reference

- PG046

边栏推荐

- [MYSQL] MYSQL文件结构,页与行记录

- 398 hash table (242. valid alphabetic words & 349. intersection of two arrays & 202. happy numbers)

- FPGA - 7系列 FPGA SelectIO -05- 逻辑资源之OLOGIC

- lambda-stream

- leetcode 410. 分割数组的最大值——(每日一难day30)

- 【数据挖掘】期末复习 第四章

- 一次Namenode的RPC延迟故障排查引发的深入思考

- tf. contrib. slim. conv2d()

- 完善业务细节

- 微生物生态排序分析——CCA分析

猜你喜欢

C language course design (detailed explanation of clothing management system)

复制 代码生成器 生成的代码到idea中,运行后网址报错怎么解决

![[SQL injection 16] read / write file for SQL vulnerability exploitation](/img/83/1c4680d4ea6980e0777b8ea4eeaba5.jpg)

[SQL injection 16] read / write file for SQL vulnerability exploitation

【数据挖掘】期末复习 第二章

C语言课程设计(服装管理系统详解)

构建和保护小型网络考试

对网页 ‘’为所欲为‘’ 之手动实现 csdn深色模式?

![[JVM] classloader](/img/32/5bf40969528285fb0d0f7f98ba585a.png)

[JVM] classloader

FPGA - 7系列 FPGA SelectIO -04- 逻辑资源之IDELAY和IDELAYCTRL

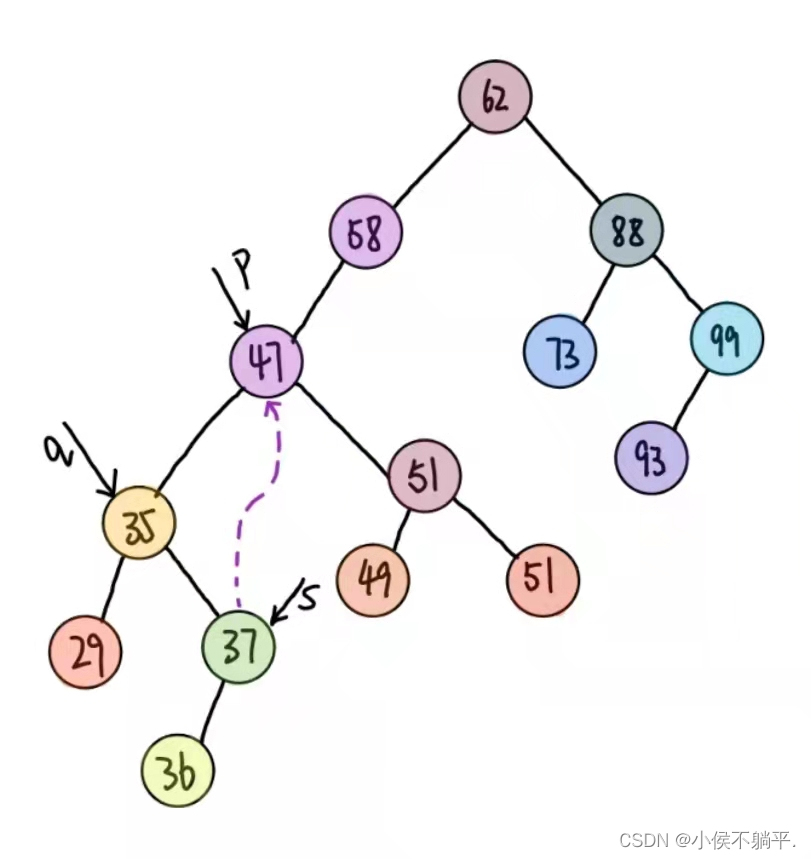

Basic operation of binary sort tree

随机推荐

对网页 ‘’为所欲为‘’ 之手动实现 csdn深色模式?

[MySQL] SQL statement execution process of MySQL

图着色问题回溯法(最通俗易懂)

R statistical plot - correlation of environmental factors +mantel test combination diagram (linket package introduction 1)

Connection refused : no futher information : localhost/127.0.0.1:6379

Cross chain revelation: has your assets really been transferred in the process of cross chain?

[JVM] method area

Deep thinking caused by a namenode RPC delay troubleshooting

构建和保护小型网络考试

397 linked list (206. reverse linked list & 24. exchange nodes in the linked list in pairs & 19. delete the penultimate node of the linked list & interview question 02.07. link list intersection & 142

Copy the code generated by the code generator to the idea. How to solve the error reported by the web address after running

Discussion on the American ess audio DAC decoder chip es9023

MySQL MySQL mysqldump data backup and incremental backup

【数据挖掘】期末复习 第二章

tf. Operation

[MYSQL] MYSQL文件结构,页与行记录

[grafana] optimization of grafana MIMIR in massive time series indicators

Improve the determination of the required items of business details. When the error information is echoed according to the returned status code, the echoed information is inconsistent with the expecta

sqli-labs23

FPGA - 7系列 FPGA SelectIO -06- 逻辑资源之ODELAY