当前位置:网站首页>[t31zl intelligent video application processor data]

[t31zl intelligent video application processor data]

2022-07-06 07:51:00 【qq2224043166】

T31ZL It is an intelligent video application processor , Suitable for mobile cameras 、 Safety investigation 、 Video call 、 Video analysis and other video equipment .

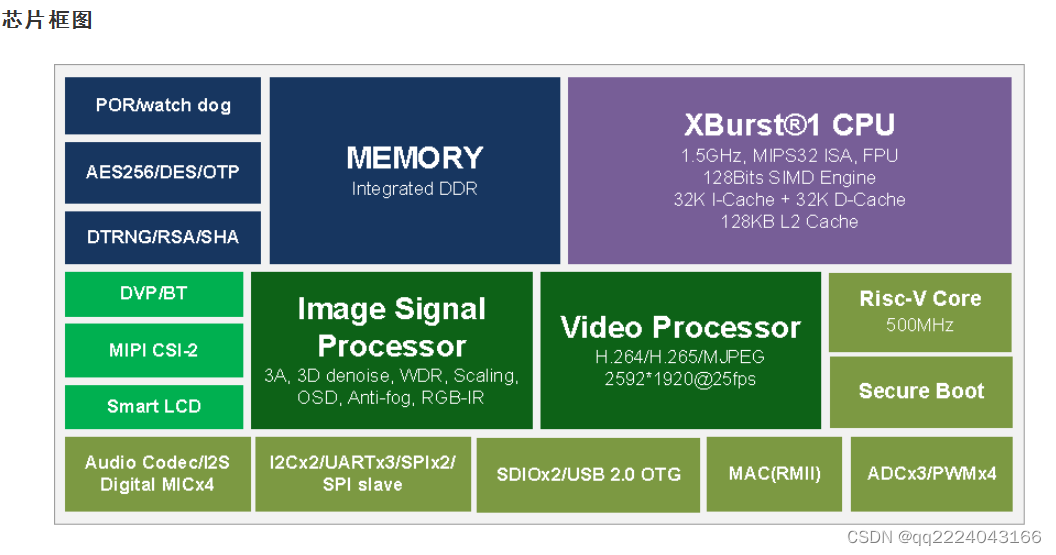

T31ZL Provide high speed CPU Ability to calculate , Excellent image signal processing .fluent 2048x2048 Resolution video recording .**CPU( a central processor )** Core equipment 32kB Instructions and 32kB Data L1 cache , as well as 128kB Second level cache , With 1.5GHz function , Full function MMU Functions perform tasks related to the operating system .CPU The core of the core is XBurst Processor engine .XBurst It is the industry-leading microprocessor core , It has excellent high performance and best in class low power consumption . It also includes a and IEEE754 Compatible hardware floating point units .

**VPU( Video processing unit )** The core is a video encoder engine , Designed for use HEVC(ISO/IEC 23008-2 Efficient video coding ) and AVC(ISO/IEC 14496-10 Advanced video coding ) Standard processing of video streams . It also supports the use of JPEG standard (ITU T.81) Still image coding .T31ZL Together with on-chip video acceleration engine and post image processing unit, it provides high video performance . Coding support AVC The maximum resolution of the format 2592x2048. the height is 40Mbit/s,[email protected]( Image signal processor ) The core supports excellent image processing of images from original sensors . It supports DVP.BT and MIPI Interface . have 3A And so on .2D and 3D Denoise .WDR/HDR, Lens coloring . It can provide the highest resolution 2592x2048 Resolution images for viewing or encoding for storage or transmission , So as to make it faster 、 More convenient to use T31ZL,512M position DDR2 Integrated on a chip .

In chip module , Such as audio codec 、 Multichannel SAR-ADC Controller and camera interface , It provides a set of economical video application peripherals for designers . Through high speed SPI and MMC/SD/SDIO The host controller supports WLAN、 Bluetooth and expansion options .

Other peripherals ( Such as USB OTG、MAC、UART and SPI) And general system resources provide enough computing and connection capabilities for many applications .POR/ watchdog XBurst(1CPU s Hz.MIPS32 ISA,FPU)

【 Functional block diagram 】

chart 1-1 T31ZL chart

1.2【 Product features 】

1.2.1CPU

·XBurst-1core

-XBurst FPU The instruction set supports single floating point and double floating point formats , And IEEE754 Compatible

-XBurst 9 Stage pipeline microarchitecture , The working frequency is 1.5GHz·MMU 32 Entrance union TLB 8 Entry command TLB 8 Entry data TLB

First level cache 32kB Instruction cache 32kB Data caching .

Hardware debugging support 16kB Tightly coupled memory L2 cache 128kB unify Cache

1.2.2 Video processor unit .

- Support DVT HEVC/AVC/JPEG Encoder .

- Support as much as 20Mbit/s Of HEVC And Gotha 40Mbit/s Of AVC,

- The maximum frame rate is [email protected]@25fps 2

- The maximum size is up to 2592x4096 The resolution of the

1.2.3 Image signal processor

- dynamic / Static defect pixel correction green equalization black level correction lens shading correction 3A( Auto exposure / Automatic white balance / Autofocus ) Support statistical information output (3A) Adaptive dynamic range compression Demosic Sharpen Bayer denoising 2D/3D De noise Xin Tongxin Color noise suppression lens distortion correction 2D Color correction 3D Color correction Fo Gamma correction ·Defog,WDR 3 Independent image scaler and output clipping , Mirror and flip support maximum resolution :2592x2048

1.2.4 intelligence LCD Basic functions of the controller

- The display size is up to [email protected]、24BPP intelligence LCD Interface 6800(A type ) and 8080(B type ) Color

- Support as much as 16777.216(16M) Color panel support through SLCD 8bit The data interface transmits in two cycles 565 adopt SLCD 8bit The data interface transmits in three cycles 888 It supports display panels of different sizes and supports internal DMA Operation and direct write register operation

1.2.5 Video input .

- Support 8/10/12 position RGB Bayer input .

- Support DVP.BT1120( Serial mode )/BT656/BT601 and MIPI CSI(2 passageway , the height is 1.5Gbps).

- The biggest support :[email protected]

- Support single sensor input

1.2.6 Audio system

- Integrated audio codec 24 position DAC, have 93dB SNR 24 position ADC, have 92dB SNR Support signal terminal and differential microphone input and line input automatic level control (ALC), It is used to smooth the pure logic process of audio recording : No mixed signal layer and less mask cost programmable input and output analog gain digital interpolation and extraction integrated filter cores Sampling rate 8K/12K/16K/24K/32/44.1K/48K/96K

1.2.7 Memory interface

- Integrate 512M position DDR2 On chip static memory interface support 6 External chip selection CS6-1#. Each storage group can be configured separately . The size and base address of the static storage group are programmable , Connect directly to 8 External memory interface device with bit bus width , Or external static storage connected to each storage group . read / Write strobe set time and hold time period can be programmed and inserted into the access cycle , The connection with low-speed memory waiting for insertion is realized by automatically waiting for periodic insertion through the waiting pin , To prevent data bus conflicts when continuous memory accesses different storage groups , Or to the same storage group after read access

1.2.8 system function

- On chip 12/24/48MHZ Clock generation and power management are realized on the oscillator circuit , A three chip PLL (PLL), With programmable multiplier CCLK、HHCLK、H2CLK.

- By setting register , You can change the software's PCLK、HOCLK、DDR CLK、VPU CLK frequency SSI Clock support 50M The clock MSC Clock support 100M Clock function unit clock gating off PO、ISP、VPU The power supply . have PWM Output and / Or enter the... Of the edge counter IPU Timer and counter units provide eight independent channels , Six of these channels have input signal conversion edge counters 16 position A The counter and 16 position B Counter , With automatic reload function . Each channel supports interrupt generation , When A The counter overflows three clock sources :RTCLK( Real time clock ).

-EXCLK( External clock input ). choice PCLK(APB Bus clock ), choice 1,4,16,64256 and 1024 Clock division . Every channel has PWM Output

◆ Operating system timer controller 64 Bit counter and 32 The bit comparison register supports interrupt generation of two clock sources when the counter matches the comparison register :RTCLK( Real time clock ).HCLK( System bus clock ) use 1.4 16.64.256 and 1024 A clock divides the selected interrupt controller , common 64 Broken source . Each interrupt source can independently enable the priority mechanism , To indicate the highest priority interrupt . All registers are controlled by CPU visit . Unmasked interrupt can wake up the chip in sleep mode . Another set of sources 、 Masks and pending registers provide services

◆ Watchdog timer generation WDT Reset 16 Bit data register ,16 The bit counter clock uses the input clock selected by the software .PCLK、EXTAL and RTCCLK It can be used as a clock for counters . Direct memory access to the controller through software , You can set the frequency division ratio of the clock to 1,4,16,64256 and 1024, Support up to 32 Independent DMA Channel descriptor or with previous JZ SoC Descriptor free transmission mode compatible with transmission data unit :1 byte 、2 byte 、4 byte 、16 byte 、32 byte 、64 byte 、128 Number of byte data units transmitted :1~224-1 Independent source and destination port widths :8 position 、16 position 、,32 Three priorities of bit fixed channel group :0-3, The highest :4-11: middle :12-31: Minimum extra INTC IRQ Can be bound to a programmable DMA passageway ·SAR A//D controller 1 Channel resolution :10 Bit integral nonlinearity :1 LSB Differential nonlinearity :t0.5 LSB The resolution of the / Speed : The highest 2MSPS Maximum frequency :24MHz low power consumption :1.5mW( The worst ) Support multi touch detection and write ct

1.2.9 peripherals

- Universal l/O Ports each port can be configured as an input 、 Output or standby function port each port can be configured as low / High level or rise / Interrupt source triggered by falling edge . Each interrupt source can be shielded independently , Each port is connected with an internal pull-up or pull-down resistor . Pull up can be disabled / Pull down resistor GPIO Output 3 A break , Each interrupt corresponds to a group ,INT·SMB Controller two-wire SMB The serial interface consists of serial data and serial clock (SCL) Form a two speed standard mode (100 Kb/s) Fast mode (400 Kb/s) Device clock and pclk A programmable SCL Generator master or slave SMB Same operation 7 Bit addressing /10 Bit addressing 16 Level transmission and reception FIFO Interrupt operation can be connected to the same number of devices SMB The bus is only affected by 400pF APB Interface 2 Independent SMB passageway (SMBO、SMB1) Limit of the maximum bus capacitance

● A high-speed synchronous serial interface (SFC)3 Protocol support :National Of Microwire.TI Of SSP. And Motorola's SPI Send only or receive only operations MSB, First used for command and data transmission , and LSB first for address transfer 64 entries x 32 bit wide data FIFO one device select Configurable sampling point for Receipt Configurable timing parameters:TSCT and tss Configurable flash address wide Is a supported transport format : standard SPI Only two data transmission modes are supported : Dependent mode and DMA Mode configurable 6 Standard speed synchronous serial interface of software flow in three stages (SSI1)3 Protocol support :National Of Microwire、TI Of SSP、, And Motorola's SPI Full duplex or transmit only or receive only operation programmable transmission sequence :MSB first or LSB first 128 Entries deep x 32 Bit width transmit and receive data FIFO Configurable normal transmission mode or interval transmission mode programmable clock phase and polarity for Motorola SSI Format back-to-back character transmission / Receive mode loopback mode test three UART(UARTO、UART1、UART2) Full duplex operation 5-.6-.7 Bit or 8 Bit character , Optional no parity 、 Parity sum 1.1%. or 2 Stop bits 64x8 Bit transfer n And receiving

1.3【 Process characteristics 】

Process technology 22nm CMOS low power consumption

Supply voltage Universal input / Output :1.5~3.6V

DDR Input / Output :1.8V(DDR2)±0.1V

EFUSE Programming :1.8V±10%

Analog power 1:1.8V±10%

Analog power 2:3.3V±10%

The core :0.8V±0.1V

encapsulation QFN 88

Working frequency 1.5GHz

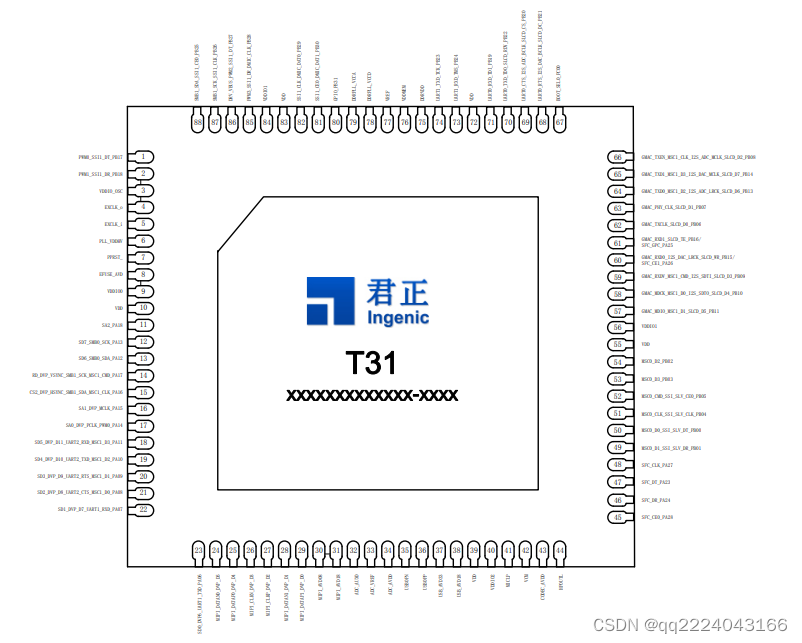

1.4【 Package and pins 】

1.4.2.1 summary T31ZL The processor uses QFN88 The package is shown in the figure 2-1 Shown .T31ZL Pin to ball distribution diagram 2-2. The details of the pin The description is shown in table 2-1

1.42.2 Welding process T31ZL Lead free packaging . Its reflux curve follows J-STD-020C It contains IPC/JEDEC Lead free reflux curve .

1.4.2.3 Humidity sensitivity grade T31ZL The humidity sensitivity grade of the package is 3 level .

Due to Junzheng data control ; A more detailed SDK Project application is required ;

边栏推荐

- Position() function in XPath uses

- Common functions for PHP to process strings

- 数字经济时代,如何保障安全?

- flask返回文件下载

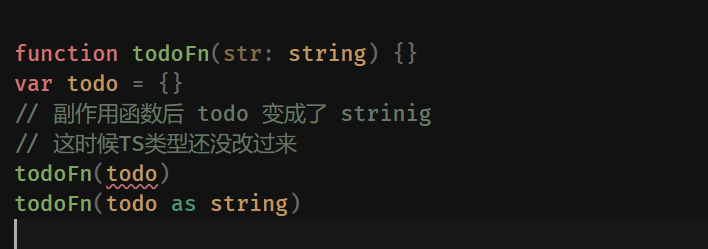

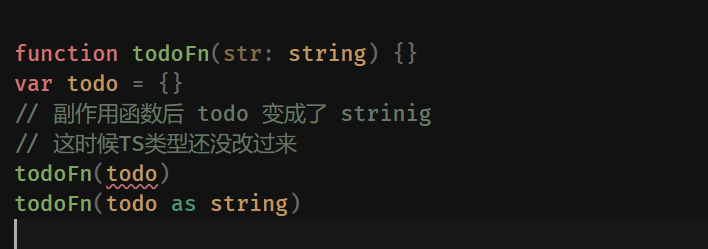

- Wonderful use of TS type gymnastics string

- 数据治理:数据质量篇

- 08- [istio] istio gateway, virtual service and the relationship between them

- [dictionary tree] [trie] p3879 [tjoi2010] reading comprehension

- 软件测试界的三无简历,企业拿什么来招聘你,石沉大海的简历

- datax自检报错 /datax/plugin/reader/._drdsreader/plugin.json]不存在

猜你喜欢

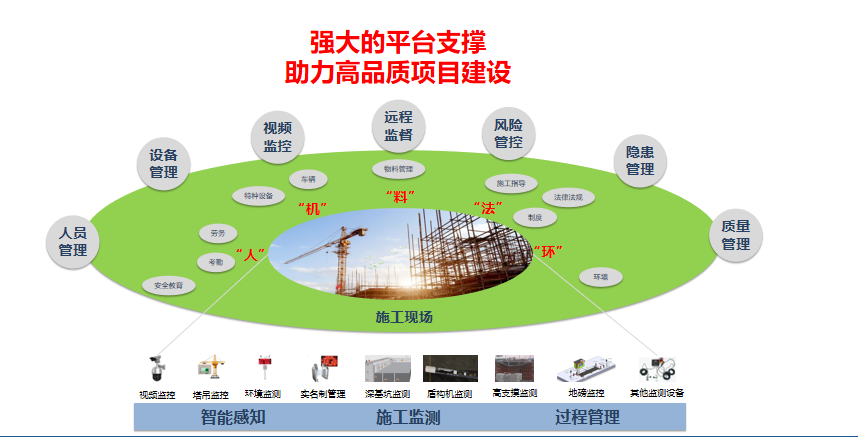

Solution: intelligent site intelligent inspection scheme video monitoring system

![[computer skills]](/img/30/2a4506adf72eb4cb188dd64cce417d.jpg)

[computer skills]

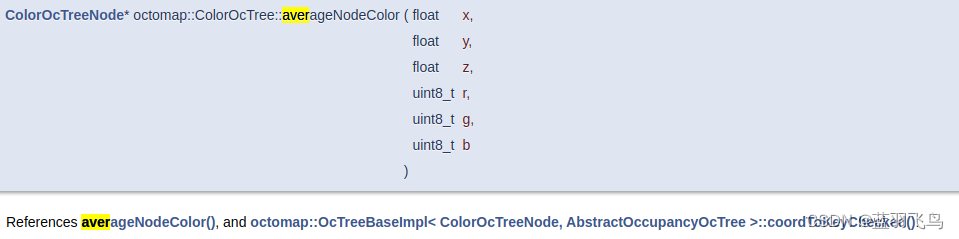

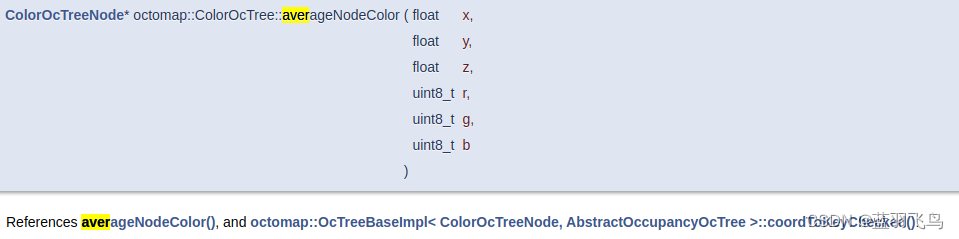

octomap averageNodeColor函数说明

Description of octomap averagenodecolor function

![[1. Delphi foundation] 1 Introduction to Delphi Programming](/img/14/272f7b537eedb0267a795dba78020d.jpg)

[1. Delphi foundation] 1 Introduction to Delphi Programming

. Net 6 learning notes: what is NET Core

![When the Jericho development board is powered on, you can open the NRF app with your mobile phone [article]](/img/3e/3d5bff87995b4a9fac093a6d9f9473.png)

When the Jericho development board is powered on, you can open the NRF app with your mobile phone [article]

Pre knowledge reserve of TS type gymnastics to become an excellent TS gymnastics master

成为优秀的TS体操高手 之 TS 类型体操前置知识储备

![If Jerry's Bluetooth device wants to send data to the mobile phone, the mobile phone needs to open the notify channel first [article]](/img/d6/92ad1c6f84415de6ab0dfd16cd6073.png)

If Jerry's Bluetooth device wants to send data to the mobile phone, the mobile phone needs to open the notify channel first [article]

随机推荐

Scala语言学习-08-抽象类

Fundamentals of C language 9: Functions

二叉树创建 & 遍历

P3047 [usaco12feb]nearby cows g (tree DP)

C # display the list control, select the file to obtain the file path and filter the file extension, and RichTextBox displays the data

opencv学习笔记八--答题卡识别

珠海金山面试复盘

edge浏览器 路径获得

Data governance: data quality

Sharing of source code anti disclosure scheme under burning scenario

js對象獲取屬性的方法(.和[]方式)

Google可能在春节后回归中国市场。

Full Score composition generator: living on code

MySQL view tablespace and create table statements

PHP Coding Standard

【T31ZL智能视频应用处理器资料】

Interview Reply of Zhuhai Jinshan

Position() function in XPath uses

[1. Delphi foundation] 1 Introduction to Delphi Programming

合规、高效,加快药企数字化转型,全新打造药企文档资源中心