当前位置:网站首页>Conception et mise en service du processeur - chapitre 4 tâches pratiques

Conception et mise en service du processeur - chapitre 4 tâches pratiques

2022-07-01 08:13:00 【서가가장아름닸다.】

Simple.CPUVoir la mise en service de la conceptionDeBug—MyCPUSection

Prends une note.:

Run All Les options ne sont disponibles qu'après avoir accédé à la page de simulation,Et le processus qu'il exécute est indiqué dans le coin inférieur droit.

1.SignalisationBug

Ajouter cinq paragraphesPCLa valeur du signal n'est pas difficile à trouver,IF_PC => ID_PCNon. EXE_PC,C'est - à - dire que la phase d'exécution n'a pas reçu dePCValeur.Résultats de l'inspection:

ifJ'ai transmis les données àid,Maisid_stageÇa n'a pas marché.fs_to_ds_bus_r <= fs_to_ds_bus.Vas - y.idModule,Découverteds_validNon assigné.

Avant modification:

Après modification:

always @(posedge clk) begin // Bug 1

if(reset) begin

ds_valid <= 1'b0;

end

else if(ds_allowin) begin

ds_valid <= fs_to_ds_valid;

end

if (fs_to_ds_valid && ds_allowin) begin

fs_to_ds_bus_r <= fs_to_ds_bus;

end

end

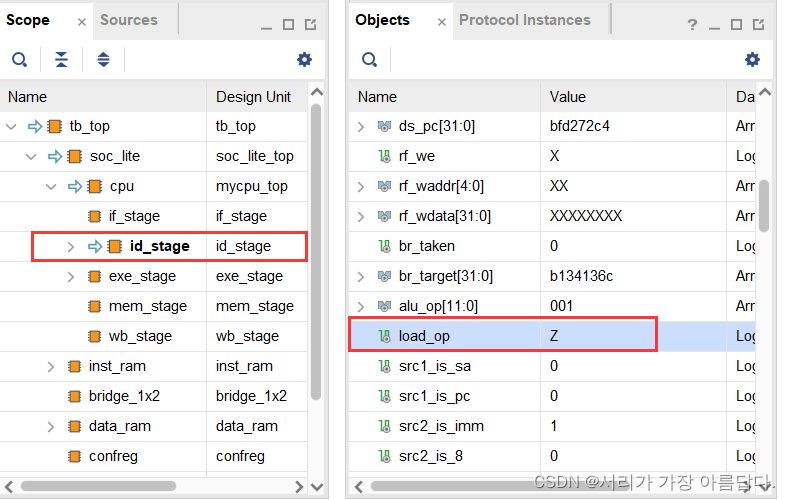

2.Typique"Z"SignalBug

Cela est souvent dû au fait que les variables ne sont pas assignées .Trouverid_stage Module Discovery :

load_op Aucune instruction d'affectation connexe . Ajouter au bon endroit :

load_opÇa veut direloadDeoperate Section cette section devrait être alignée sur lw Connexion à la commande .

SimulationBugPetit épisode

Compléter la logique ci - dessus Bug, Refaire la simulation , L'épisode suivant apparaît :

La plupart de ces indices sont dus à des erreurs de frappe dans certaines variables , Ne paniquez pas. .Cliquez surok Vous pouvez voir le chemin exact du fichier pour le problème :

Ouvrez le bloc - notes pour voir l'emplacement exact des erreurs .

MonBugPositionné comme:ID.stage De 128 Lignes et troisième lignes

Utiliser de nouveaux outils -Basé surTrace Mise en service de la comparaison

3.Addiu Paramètres de transfert de l'instance d'instruction Bug

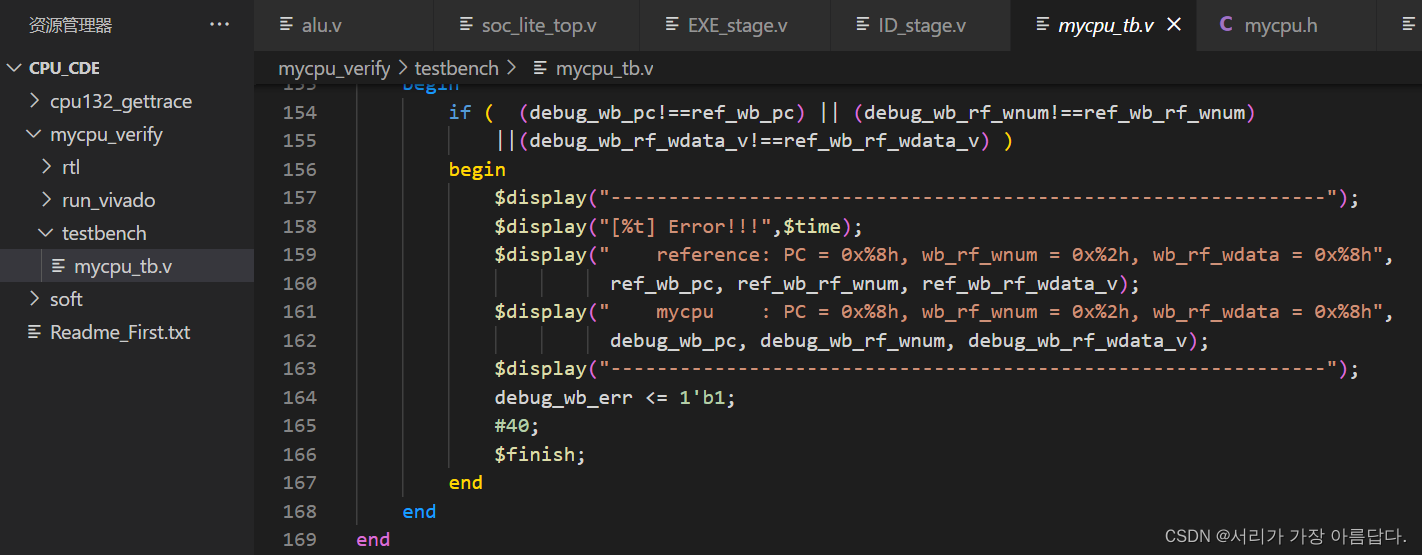

Run All Le premier apparaît après trace Erreur de comparaison , Les messages d'erreur de comparaison sont tirés des codes pertinents suivants: :

On peut voir que les informations relatives à la comparaison sont les suivantes: :PCValeur、 Registre de destination écrit 、 Écrire les données de destination

Analyse:PCLa valeur est: 0x bfc00000, Quelle directive représente - t - elle? ?

In lab3\CPU_CDE\soft\func_lab3\obj\test.s Recherche moyenne bfc00000 Vous pouvez voir les instructions correspondantes :

Pour 0x2408 ffff Instructions correspondantes 001001 00000 01000 1111111111111111

Consultez le tableau pour savoir, Le format d'instruction correspondant est addiuDirectives, Et l'emplacement de l'erreur est sur les données écrites , Il faut vérifier. aluModules etEXE_stageModule,Découverte:

EXE_stage Erreur d'Instanciation des paramètres du module

Modifier comme suit::

alu u_alu(

.alu_op (es_alu_op ),

.alu_src1 (es_alu_src1 ),

.alu_src2 (es_alu_src2 ),

.alu_result (es_alu_result)

);

4.Bug

Je vois. PC Une erreur s'est produite, Il doit y avoir une branche ou un saut. , Regardons quelques instructions à proximité. (test.sDocumentation).

/media/sf_func_lab3/start.S:19

bfc00004: 2408ffff li t0,-1

/media/sf_func_lab3/start.S:20

bfc00008: 100000e0 b bfc0038c <locate>

/media/sf_func_lab3/start.S:21

bfc0000c: 00000000 nop

/media/sf_func_lab3/start.S:24

bfc00010: 3c088000 lui t0,0x8000

/media/sf_func_lab3/start.S:25

bfc00014: 25290001 addiu t1,t1,1

Il est évident que bfc00008 Cette instruction est une instruction de branche ,Et mycpu Pas de saut .

Expliquez d'abord nop Directives, C'est gentil de définir l'instruction slot Delay à nop,Comme ci - dessus,nop La directive n'exige pas non plus de mise en œuvre spécifique .

Le flux de contrôle s'écoule d'abord dans l'étape du doigt de préfet , Puis pré - Fetch Finger phase Update PC Et visiter RAM Obtenir des instructions ,PC Et RAM Enfin, la phase de décodage s'écoule simultanément , Le saut est effectué au cours de la phase de décodage par le contrôle Logique combinatoire .

Nous Séquence d'exécution prévue

Je vois.,Dans nos attentes, Le pré - jugement des instructions de branche est effectué par la phase de décodage .

Celui - là. B Directive modifiée par r0 Hengwei 0 Et BEQ La directive obtient.

Nous pouvons trouver que lorsque cette instruction de fente de retard , J'aurais dû. assign br_bus = {br_taken,br_target};, Mais les deux signaux les plus bas sont les mêmes. , Pour trouver le problème .

Problème avec le chemin du fichier :\lab3\CPU_CDE\mycpu_verify\rtl\myCPU\mycpu.h

Changer la largeur du BIT :

`define BR_BUS_WD 33

5.Bug

Erreur globale

Cette erreur est toujours aluModule( Assignation de l'inadéquation des largeurs de bits avant et arrière ):

Changement:

assign sr_result = sr64_result[31:0];

6.Bug

C'est parce que RTL Circuit combiné présent dans le Code ,Pas facile à trouver., Si, par hasard, vous voyez cette ligne, , Son erreur est encore évidente. .

alu.vErreur du module:

Changement:

assign or_result = alu_src1 | alu_src2;

PC-BugPetit épisode

Après avoir résolu les problèmes ci - dessus , Rediriger pour découvrir ce phénomène ...

Observations: Writeback Level for each Running Error reported PCAvectrace.txtIncohérence, Mais son numéro de registre de destination et ses données sont corrects . Quelle est la cause? ?

7.Le dernier.Bug

Chemin du fichier d'erreur :mycpu_verify => rtl => myCPU => tools.v

Un peu plus d'attention va voir ici. decoder_6_64 Il n'y a pas assez de décodage pour le module 64Bits,C'est - à - dire seulement【62:0】, Donc ça devrait être changé en :

generate for (i=0; i<64; i=i+1) begin:gen_for_dec_6_64 //Bug 7

Affichage vidéo réussi :

Il est recommandé d'allumer tous les interrupteurs de cadran lors de l'essai sur le tableau supérieur. , La vitesse de comptage est la plus lente en ce moment , Faciliter l'observation des phénomènes expérimentaux . On peut en composer un ou deux. ,Vitesse modérée.

Liens vidéo:Simple.CPU Tâches pratiques de référence en matière de conception

RÉFÉRENCES:

Liens vers des blogs connexes :CPUConception pratique lab3

边栏推荐

- The difference between interceptors and filters

- How to prevent the other party from saying that he has no money after winning the lawsuit?

- On several key issues of digital transformation

- Why are some Wills made by husband and wife invalid

- How to get a SharePoint online site created using the office365 group template

- 力扣每日一题-第31天-202.快乐数

- [getting started] enter the integer array and sorting ID, and sort its elements in ascending or descending order

- 使用 setoolkit 伪造站点窃取用户信息

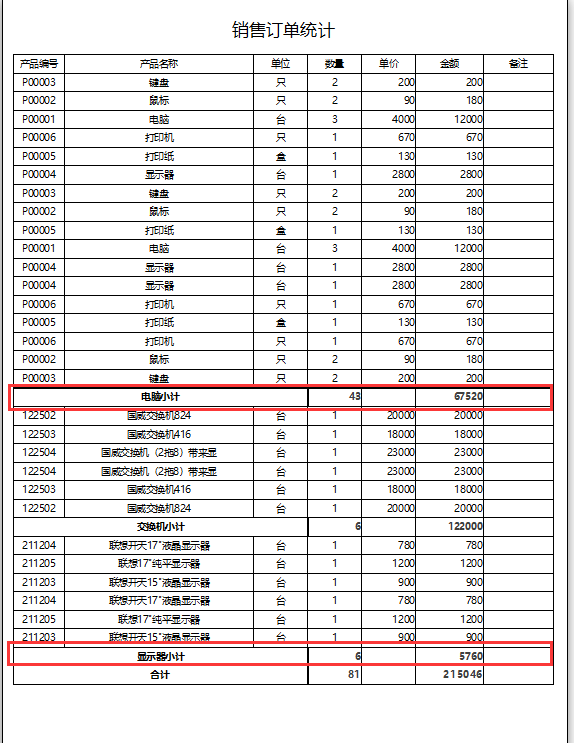

- Access report realizes subtotal function

- [staff] key number (key number identification position | key number marking list | a major key identification principle | F, C, G position marking ascending | F major key identification principle | B

猜你喜欢

随机推荐

php laravel微信支付

程序员养生宝典

Serial port oscilloscope software ns-scope

[getting started] intercepting strings

【入门】输入n个整数,输出其中最小的k个

Soft keyboard height error

Thesis learning -- Analysis and Research on similarity query of hydrological time series

凸印的印刷原理及工艺介绍

web254

Gdip - hatchBrush图案表

Using settoolkit to forge sites to steal user information

[untitled]

golang中的正则表达式使用注意事项与技巧

How to prevent the other party from saying that he has no money after winning the lawsuit?

CPU设计实战-第四章实践任务一简单CPU参考设计调试

[getting started] enter the integer array and sorting ID, and sort its elements in ascending or descending order

Tupu software has passed CMMI5 certification| High authority and high-level certification in the international software field

Li Kou daily question - day 31 -202 Happy number

Significance and measures of source code encryption

How to get a SharePoint online site created using the office365 group template