当前位置:网站首页>The use of DDR3 (Naive) in Xilinx VIVADO (3) simulation test

The use of DDR3 (Naive) in Xilinx VIVADO (3) simulation test

2022-08-04 11:13:00 【chylinne】

1. Overview

This paper conducts Testbench simulation on the previously configured MIG IP core based on user interface (Naive) and the designed read-write module, and verifies the consistency of write/read data through waveform data.

2, DDR3 emulation file call

Since the physical ports in the MIG IP core (such as ddr3_dq, ddr3_dqs_n, ddr3_dqs_p, ddr3_addr, etc.) need to be connected to the DDR3 chip, we also need to connect these interfaces to a specific DDR simulation module during simulation, so that theEmulates the operation of a DDR3 chip.

Before running the simulation, we need to add the header file ddr3_model_parameters.vh and the DDR3 simulation module file ddr3_model.sv into the project, as shown in the following figure.These two files can be copied from the official routines of the MIG IP core.Select the MIG IP core (mig_7series_0) added in the project, then right-click and select Open IP Example Design to download the official example.These two files can be found in the import directory in the official routine.

3, Testbench code design

The previous article introduced the design of the read-write state machine, which can be briefly summarized as follows:

Idle state IDLE (4'b0001), write data state WRITE (4'b0010), write read interval state WAIT (4'b0100), read data state READ (4'b1000).The write operation is to write 0~511 in sequence, the address starts from 0, and the address increases by 8.The read operation starts from address 0, increases the address by 8, and counts, and the count value should be equal to the read data value.

So in Testbench, we just need to set a system clock of 50 MHz, and then make sure that the top layer under test (ddr3_rw_top) and the DDR3 emulation module (ddr3_model) are wired correctly.The Testbench code looks like this:

`timescale 1ns/100psmodule tb_ddr3_rw_top();reg sys_clk;reg sys_rst_n;wire[15:0] ddr3_dq;wire [1:0] ddr3_dqs_n;wire[1:0] ddr3_dqs_p;wire[13:0] ddr3_addr;wire[2:0] ddr3_ba;wire ddr3_ras_n;wire ddr3_cas_n;wire ddr3_we_n;wire ddr3_reset_n;wire[0:0] ddr3_ck_p;wire [0:0] ddr3_ck_n;wire[0:0] ddr3_cke;wire [0:0] ddr3_cs_n;wire[1:0] ddr3_dm;wire[0:0] ddr3_odt;wire error_flag;initial beginsys_clk = 1'b0;sys_rst_n <= 1'b0;#50sys_rst_n <= 1'b1;endalways #10 sys_clk = ~sys_clk;ddr3_rw_top ddr3_rw_top_inst(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.ddr3_dq (ddr3_dq),.ddr3_dqs_n (ddr3_dqs_n),.ddr3_dqs_p (ddr3_dqs_p),.ddr3_addr (ddr3_addr),.ddr3_ba (ddr3_ba),.ddr3_ras_n (ddr3_ras_n),.ddr3_cas_n (ddr3_cas_n),.ddr3_we_n (ddr3_we_n),.ddr3_reset_n (ddr3_reset_n),.ddr3_ck_p (ddr3_ck_p),.ddr3_ck_n (ddr3_ck_n),.ddr3_cke (ddr3_cke),.ddr3_cs_n (ddr3_cs_n),.ddr3_dm (ddr3_dm),.ddr3_odt (ddr3_odt),.error_flag (error_flag));ddr3_model ddr3_model_inst (.rst_n (sys_rst_n),.ck (ddr3_ck_p),.ck_n (ddr3_ck_n),.cke (ddr3_cke),.cs_n (ddr3_cs_n),.ras_n (ddr3_ras_n),.cas_n (ddr3_cas_n),.we_n (ddr3_we_n),.dm_tdqs (ddr3_dm),.ba (ddr3_ba),.addr (ddr3_addr),.dq (ddr3_dq),.dqs (ddr3_dqs_p),.dqs_n (ddr3_dqs_n),.tdqs_n(),.odt (ddr3_odt));endmodule4. Test results

(1) Overview

As shown in the red box in the figure below, the init_calib_complete output by the DDR3 chip is pulled high, indicating that the DDR3 initialization is successful.The data verification result error_flag is all 0, indicating that the reading and writing are correct.Among them, the condition for error_flag to be pulled high (set to 1) is: when the DDR3 output read is valid, the read count value ≠ the read data value.

(2) Write start

As shown in the red box in the figure below, cur_state is the current state of the state machine, and 2 represents the write state.The given address app_addr starts from 0 and increases by 8.When the write enable app_wdf_wren is pulled high, the data app_wdf_data (0, 1, 2...) is written.

(3) End of writing

As shown in the red box in the figure below, cur_state is the current state of the state machine, and 2 represents the write state.When the write enable app_wdf_wren is high, the data app_wdf_data (509, 510, 511...) is written, 512 cannot be written because app_wdf_wren is pulled low.

(4) Start of reading

As shown in the red box in the figure below, cur_state is the current state of the state machine, and 8 represents the read state.When the read valid app_rd_data_valid output by DDR3 is high, the data corresponding to the previously input address can be read out. The red box reads app_rd_data data 0, 1, 2 ..., and the counter rd_cnt also starts to count, and the two valuesThe same, the description reads correctly.

(5) End of reading

As shown in the red box in the figure below, when the app_rd_data_valid output by DDR3 is high, the read data is valid, and the data is read in the red box... 509, 510, 511.The data 480 (or other data) outputted later can be ignored, because app_rd_data_valid has been pulled low by DDR3 at this time, and the data is invalid.

边栏推荐

猜你喜欢

Maple 2022软件安装包下载及安装教程

What is the principle of thermal imaging temperature measurement?Do you know?

Use pytest hook function to realize automatic test result push enterprise WeChat

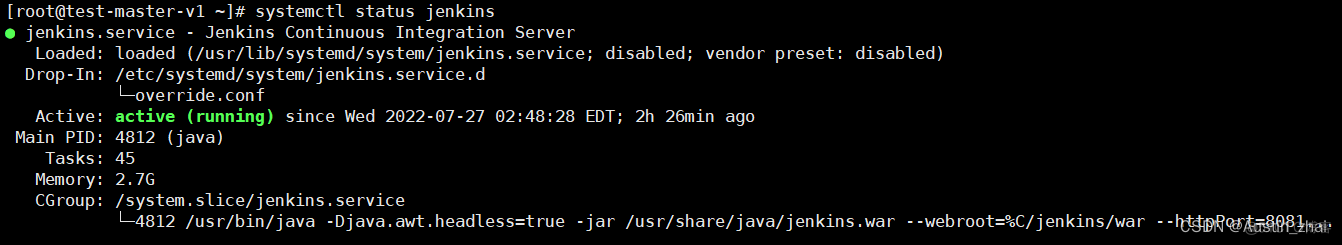

Jenkins使用手册(1) —— 软件安装

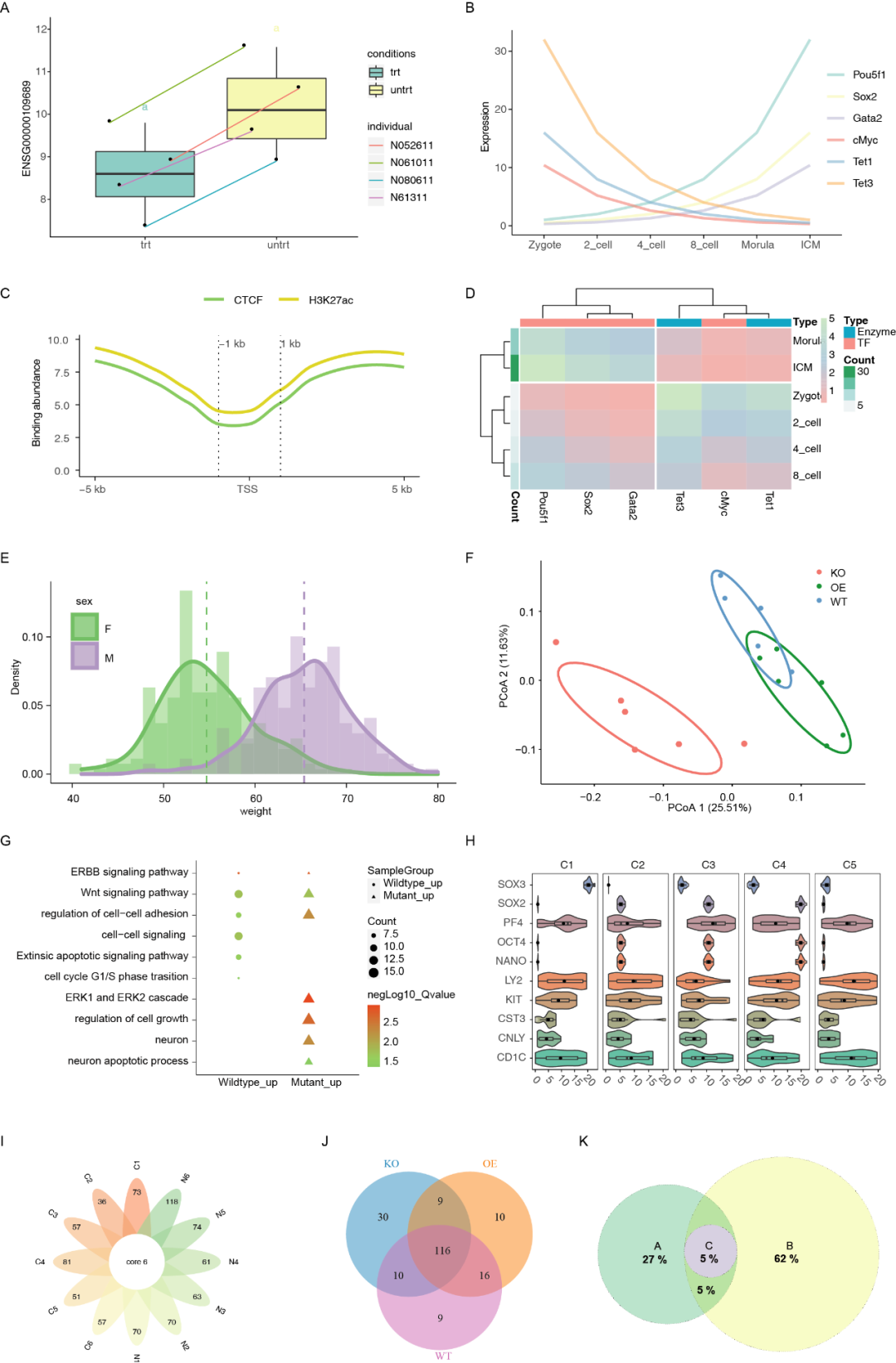

Advanced transcriptome analysis and R data visualization hot registration (2022.10)

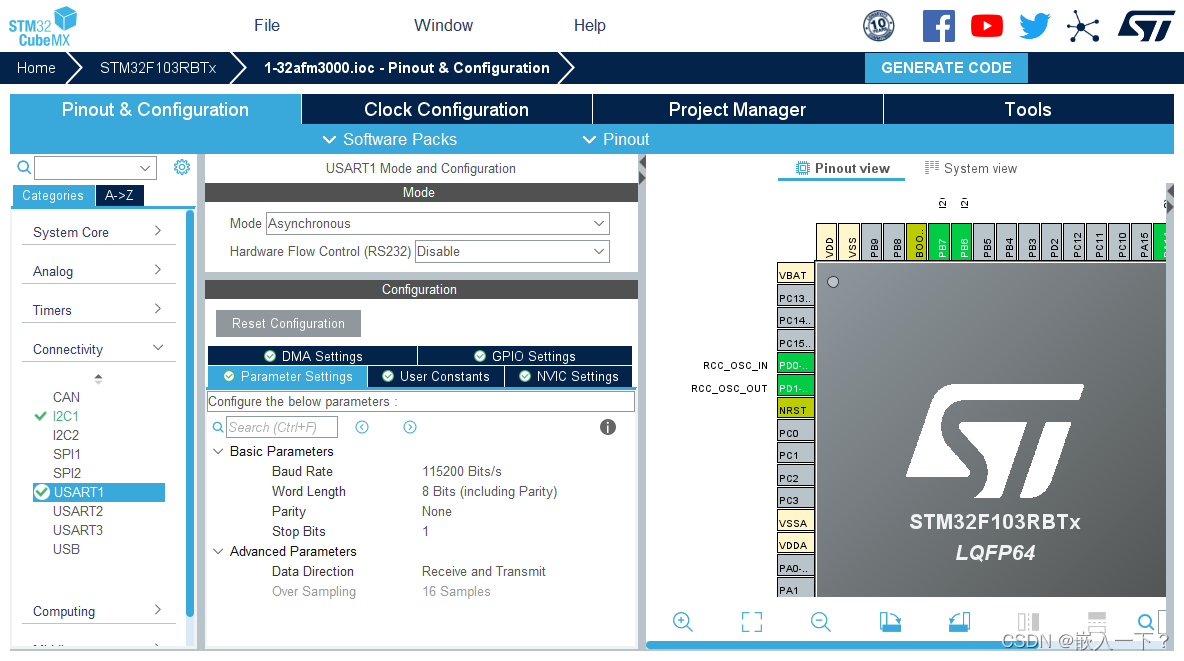

cubemx stm32 afm3000模块 气体流量传感器 驱动代码

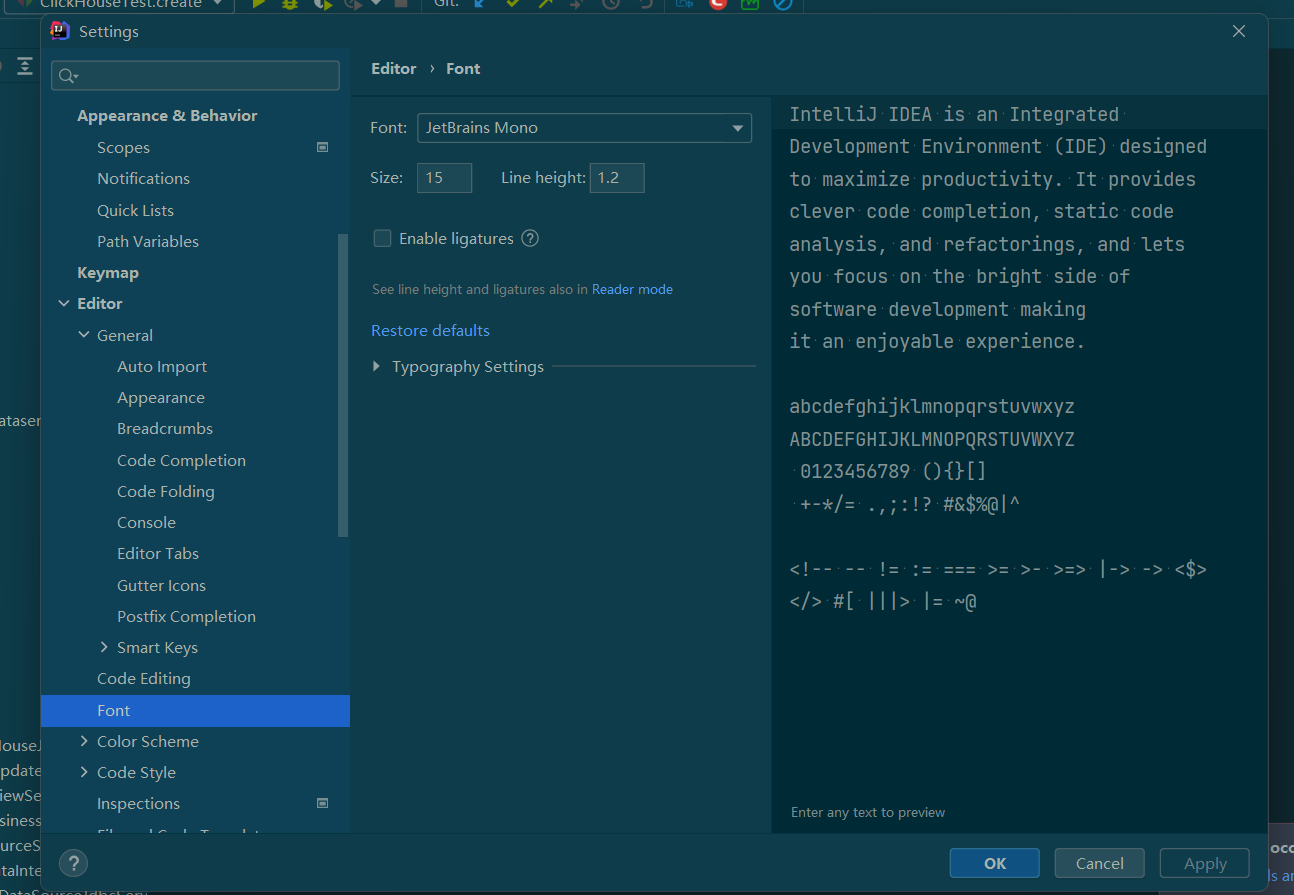

【Idea series】idea configuration

A topic of map

北京大学,新迎3位副校长!其中一人为中科院院士!

利用pytest hook函数实现自动化测试结果推送企业微信

随机推荐

apache dolphin scheduler 文件dolphinscheduler-daemon.sh详解

Leetcode刷题——543. 二叉树的直径、617. 合并二叉树(递归解决)

WPF 截图控件之画笔(八)「仿微信」

Business collocations

Four ways to traverse a Map

Win11文件类型怎么改?Win11修改文件后缀的方法

Leetcode——利用先序遍历特性完成114. 二叉树展开为链表

MySQL 45 讲 | 10 MySQL为什么有时候会选错索引?

Mysql高级篇学习总结13:多表连接查询语句优化方法(带join语句)

章节小测一

Oracle中对临时表空间执行shrink操作

热成像测温的原理是什么呢?你知道吗?

Leetcode刷题——路径总和

mae,mse,rmse分别利用sklearn和numpy实现

Super Learning Method

MySQL 45 讲 | 11 怎么给字符串字段加索引?

Leetcode刷题——构造二叉树(105. 从前序与中序遍历序列构造二叉树、106. 从中序与后序遍历序列构造二叉树)

ORA-00054 资源正忙

Jenkins使用手册(1) —— 软件安装

*W3C* 标准组织