当前位置:网站首页>STM32 Personal Notes - Watchdog

STM32 Personal Notes - Watchdog

2022-08-01 09:48:00 【Couvrir wild beast】

Part of the notes are from the public account of "STM32 Embedded Development".

Watchdog

Early MCUs did not have a watchdog, which could easily cause some products to crash and fail to restart.To avoid this problem, later MCUs inherit the function of watchdog internally.

There are two kinds of watchdogs, which are used in different fields.Two watchdogs: independent watchdog and window watchdog.

Independent Watchdog

It is known from the RCC clock tree that the LSI drives the independent watchdog.Remains active even in the event of a master clock transmission failure.

IWDG is most suitable for those occasions where the watchdog needs to be used as an outside of the main program, can work completely independently, and requires less time precision.

Features:

Free running down counter.

Clocked by independent RC oscillator (can operate in standby and stop modes).

A reset occurs when the down counter value reaches 0x000 (if the watchdog is activated).

Window watchdog

The reason why it is called a window is because the dog feeding time is within a range with upper and lower limits. You can set the upper limit time and lower limit time by setting the time register: the dog feeding time cannot be too early or too late..

Features:

A programmable down counter.

Conditions to trigger chip reset:

The down counter has not been updated for a certain period of time -- commonly known as feeding the dog.

Not updated within the specified time frame---------------It's too early to feed the dog, the dog is not hungry yet.

Watchdog Reset Early Warning Interrupt -- Gives the application a chance to update the down counter (feed the dog) before the chip resets.

The upper limit window of the window watchdog is the configuration register WWDG_CFG: W[6:0], and the lower limit window is fixed 0x40.

A reset occurs when the window watchdog counter is outside the upper limit window or outside the lower limit window.

The upper limit window is set by WWDG_CFG:W[6:0], the maximum is 0x7F, which is 127.The minimum is 0x40, which is 64.So the value range is 0x40~0x7F, that is, 64~127.

Configuration register WWDG_CFG: WDGTB[1:0] sets the clock frequency division factor for the counter, determines the time range that the counter can time, and thus determines the time range of the window.

The clock of the window watchdog comes from PCLK1, and its frequency is 36M in the clock configuration.Then, the WWDG timeout period can be calculated by the above timeout formula.

Difference

Condition comparison:

Characteristic comparison:

Similar points

Different points

The difference between the two:

The independent watchdog has no interrupts, and the windowed watchdog has interrupts.

The independent watchdog is divided into hardware and software, and the window watchdog can only be controlled by software.

Independent watchdog has only lower limit, window watchdog has lower limit and upper limit.

The independent watchdog is 12-bit decremented, and the windowed watchdog is 7-bit decremented.

The independent watchdog uses the internal RC oscillator of about 40kHz, and the window watchdog uses the system clock APB1.

The independent watchdog has no interrupt function. As long as the value of the counter is reloaded before the counter decreases to 0 (lower limit), no reset will be generated.

Be careful when the watchdog and an external reset IC exist at the same time, the external circuit may prevent the watchdog from being reset.

The window watchdog has an interrupt. The function of this interrupt is to generate an interrupt when the counter reaches the lower limit of 0x40, allowing you to feed the dog.If the dog is not fed, the system reset will be generated when the value of the counter becomes 0x3f.Even if you feed the dog, you should feed the dog quickly in the interrupt, or the counter will decrease by 1 after a long time and it will become 0x3f to reset.

The window watchdog also has an upper limit value, the counter can only be loaded if the counter value is between the upper limit value and the lower limit value, otherwise a system reset will be generated.When the upper limit value is smaller than the lower limit value, it is meaningless.

边栏推荐

猜你喜欢

随机推荐

Opencv creates a window - cv.namedWindow()

招聘随想2022

Lsky Pro 企业版手动升级、优化教程

【数据集】各类绝缘子、鸟巢及防震锤数据集汇总

How to query database configuration parameters in GBase 8c, such as datestyle

js中如何实现深拷贝?

杨辉三角(c语言实现)

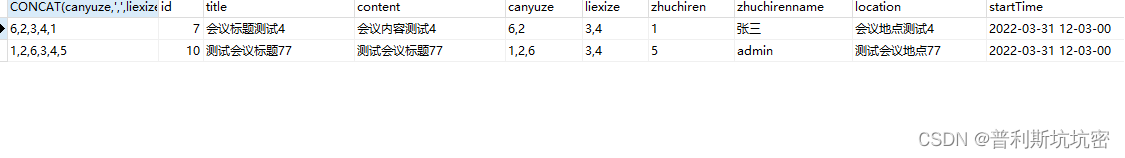

Meeting OA (Upcoming Meetings & All Meetings)

50.【动态二维数组的运用】

SkiaSharp 之 WPF 自绘 五环弹动球(案例版)

朴素贝叶斯--学习笔记--基本原理及代码实现

net stop/start mysql80 access denied

PHP获取时间戳后写数据库的一个问题

ogg同步oracle到mysql,字段里面可能有需要转义的字符,怎么配置转义?

Dataset之mpg:mpg数据集的简介、下载、使用方法之详细攻略

已解决(pip安装库报错)Consider using the-- user option or check the permissions.

C语言程序设计50例(三)(经典收藏)

ASP.NET Core 6框架揭秘实例演示[30]:利用路由开发REST API

关于#SQL#的问题,如何解决?

[Software Architecture Mode] The difference between MVVM mode and MVC mode