当前位置:网站首页>What is the difference between'1 and'b1 when assigning values

What is the difference between'1 and'b1 when assigning values

2022-07-25 23:34:00 【A little confused】

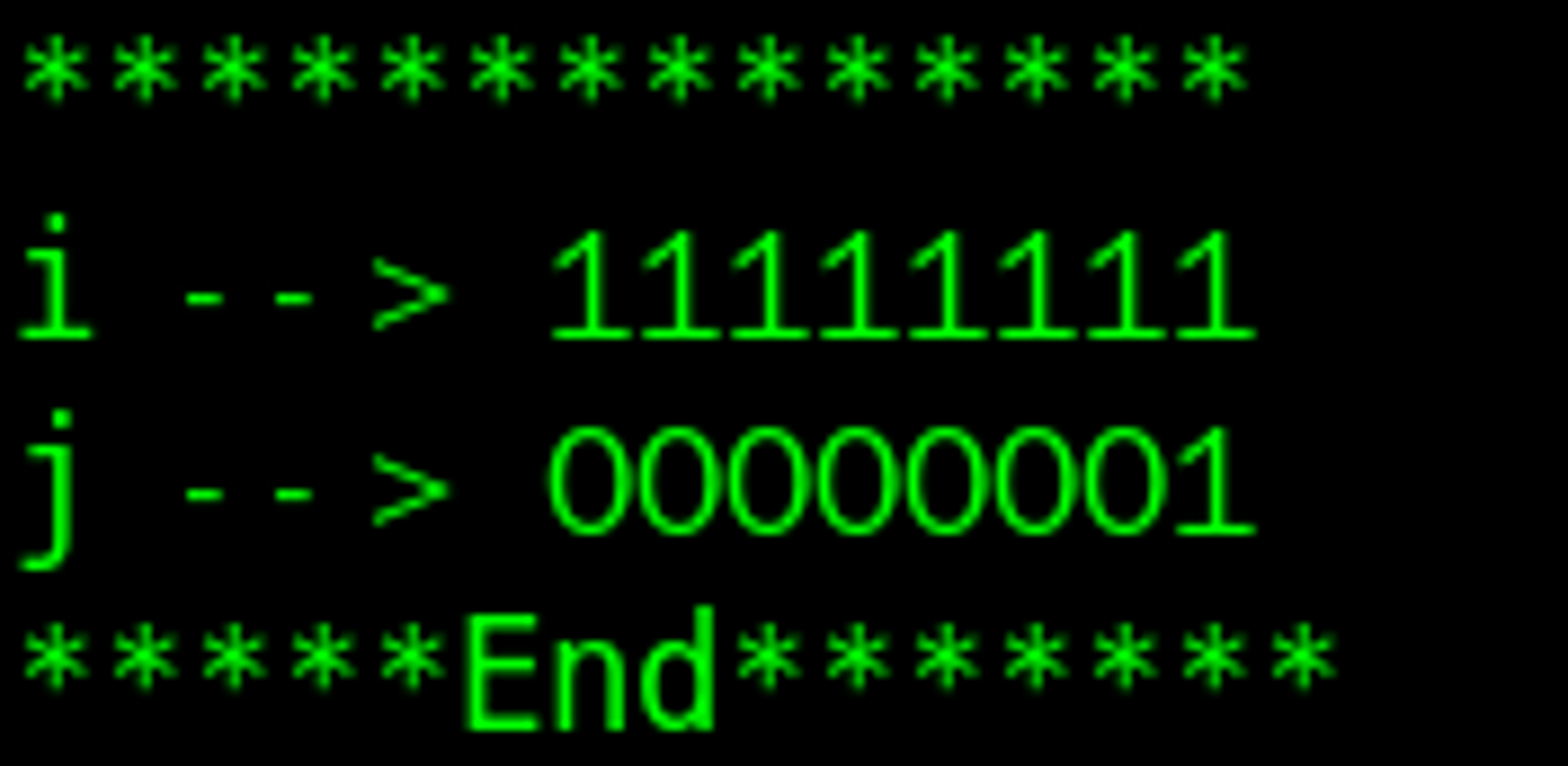

stay sv When assigning a value in ,'1 and 'b1 What difference does assignment make ?

Give a simple assignment file , Look at the output

module tb;

byte i;

byte j;

initial begin

i = '1;

j = 'b1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

Variable i and j All declared as byte type (8 bit), When used '1 When assigning values , All bits are 1; When used 'b1 When assigning values , Only the lowest is 1

What are the benefits

Let's make a change

module tb;

parameter SIZE = 8;

bit [SIZE-1 : 0] i;

bit [SIZE-1 : 0] j;

initial begin

i = '1;

j = 'b1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

Set a parameter , The output at this time should be consistent with that before the change

But if we subsequently change the value of the parameter , For example, we will SIZE The value of is changed to 16, Let's take a look at the results

module tb;

parameter SIZE = 16;

bit [SIZE-1 : 0] i;

bit [SIZE-1 : 0] j;

initial begin

i = '1;

j = 'b1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

You can see , use '1 The way of assignment , No matter how wide the seat is , All positions will be 1

And if we use the common Verilog Assignment method , When the bit width is 8 bit when

i = 8'hFF

When the bit width is changed to 16 bit when

i = 16'hFFFF

To achieve this effect , Many steps are simplified when changing

I looked back Verilog The book of , Found in fact Verilog There are also ways to achieve this effect , Is to use complement

i = ~0; //1 Complement operation of

j = -1; //2 Complement operation of

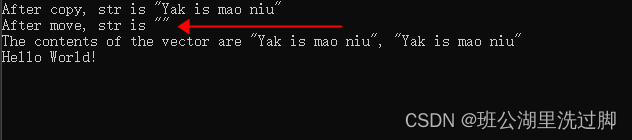

Take a look at the running results in this example

module tb;

parameter SIZE = 16;

bit [SIZE-1 : 0] i;

bit [SIZE-1 : 0] j;

initial begin

i = ~0;

j = -1;

$display("**************");

$display("i --> %b", i);

$display("j --> %b", j);

$display("*****End*******");

end

endmodule

It does , then SIZE The value of is changed to 32

All positions can still be 1

边栏推荐

- [code case] blog page design (with complete source code)

- Scaffold installation

- LeetCode 0136. 只出现一次的数字:异或

- Idea sets get and set templates to solve the naming problem of boolean type fields

- 从哪些维度评判代码质量的好坏?如何具备写出高质量代码的能力?

- Summary of built-in instructions and custom instructions

- Cuteone: a onedrive multi network disk mounting program / with member / synchronization and other functions

- 在应用中使用 Jetpack 库

- [Muduo] package EventLoop and thread

- 【微信小程序】页面导航

猜你喜欢

Very simple vsplayaudio online music player plug-in

utility实用组件学习之swap,move,forward,exchange

Release of v6.5.1/2/3 series of versions of Xingyun housekeeper: the ability of database OpenAPI continues to be strengthened

Idea sets get and set templates to solve the naming problem of boolean type fields

POI special effects Market Research

The VM session was closed before any attempt to power it on

【JUC】并发需要了解的关键字volatile

Taobao Search case

WordPress removes the website publishing time

WebMvcConfigurationSupport

随机推荐

谷粒学苑P98踩坑 e.GlobalExceptionHandler : null

Cuteone: a onedrive multi network disk mounting program / with member / synchronization and other functions

chown: changing ownership of ‘/var/lib/mysql/‘: Operation not permitted

图的遍历-DFS,BFS(代码详解)

Docker 安装 Redis-5.0.12(远程访问)

762. Prime number calculation setting in binary representation

Classes and objects (3)

WebMvcConfigurationSupport

The VM session was closed before any attempt to power it on

[Muduo] package EventLoop and thread

【MUDUO】EventLoopThreadPool

Function definition and call

JS get the current date and time

Several commonly used traversal methods

[Muduo] EventLoop event cycle

意向不到的Dubug妙招

Rendering, filtering (filtering) and sorting of lists

LeetCode 0135. 分发糖果

Source code of YY music wechat applet imitating Netease cloud music

策略模式_