当前位置:网站首页>Xilinx约束学习笔记—— 时序约束

Xilinx约束学习笔记—— 时序约束

2022-08-02 06:43:00 【ltqshs】

Xilinx约束学习笔记—— 约束方法学

1.1 组织约束文件

Xilinx 建议将时序约束和物理约束分开保存为两个不同的文件。甚至可以将针对某一个模块的约束单独保存在一个文件中。

1.1.1 综合和实现可以使用不同的约束文件

可以使用 USED_IN_SYNTHESIS 和 USED_IN_IMPLEMENTATION 属性指定约束文件是在综合或实现过程中使用。

注意:特别是IP、DCP这类使用OOC模式的模块,因为这些模块在综合过程中是一个黑盒,当顶层约束指定的约束路径为黑盒中的内容时,可能在综合过程中会报找不到目标的错误。因此,最好的方法是将约束会为两个文件,一个综合用,一个实现时用。

在工程模式中可以使用如下代码指定约束文件使用时机。

set_property USED_IN_SYNTHESIS false [get_files wave_gen_pins.xdc]

set_property USED_IN_IMPLEMENTATION true [get_files wave_gen_pins.xdc]

非工程模式中,不需要如此设置。因为什么时候使用约束文件,只和读取约束文件的时机相关。如下:其中 wave_gen_timing.xdc 会在综合和实现过程中使用,而 wave_gen_pins.xdc 只会在实现过程中使用。

read_verilog [glob src/*.v] read_xdc wave_gen_timing.xdc synth_design -top wave_gen -part xc7k325tffg900-2 read_xdc wave_gen_pins.xdc opt_design place_design route_design 1.2 约束的顺序

推荐约束顺序如下:

## Timing Assertions Section

# Primary clocks

# Virtual clocks

# Generated clocks

# Clock Groups

# Bus Skew constraints

# Input and output delay constraints

## Timing Exceptions Section

# False Paths

# Max Delay / Min Delay

# Multicycle Paths

# Case Analysis

# Disable Timing

## Physical Constraints Section

# located anywhere in the file, preferably before or after the timing constraints

# or stored in a separate constraint file

1.3 创建综合约束

Vivado 综合将设计中的 RTL 描述转换为工艺映射网表。此过程分为多个步骤进行,包括一些时序导向的优化。FPGA 包含许多逻辑特性,可以有许多不同的应用方式。需要通过约束来引导综合引擎工作,以满足实现时所需的要求。

综合约束可以分为4类:

RTL Attributes

Timing Constraints

Physical and Configuration Constraints

Elaborated Design Constraints

1.3.1 RTL Attributes

RTL Attributes 必须写入 RTL 文件中。他们通常用来选择逻辑的某些部分的映射样式,以及保留某些寄存器和网线,或控制最终网表中的设计层次结构。

IMPORTANT: The DONT_TOUCH attribute does not obey the properties of USED_IN_SYNTHESIS and USED_IN_IMPLEMENTATION . If you use DONT_TOUCH properties in the synthesis XDC, it is propagated to implementation regardless of the value of USED_IN_IMPLEMENTATION .

注意:DONT_TOUCH 属性不受 USED_IN_SYNTHESIS 和 USED_IN_IMPLEMENTATION 的控制,当在综合约束中使用 DONT_TOUCH 时,他会传递到实现过程中,无论 USED_IN_IMPLEMENTATION 的属性值是什么。

set_property DONT_TOUCH true [get_cells fsm_reg]

1.3.2 Timing Constraints

Timing Constraints 必须通过一个或多个 XDC 文件传递给综合引擎。只有以下与建立时间分析相关的约束对综合结果有实际影响:

create_clock

create_generated_clock

set_input_delay

set_output_delay

set_clock_groups

set_false_path

set_max_delay

set_multicycle_path

1.3.3 Physical and Configuration Constraints

Physical and Configuration Constraints 会被综合算法忽略。(既然会被忽略为什么又提到?)

1.3.4 Elaborated Design Constraints

创建综合 XDC 的第一个版本时,只需要使用简单的时序约束来描述高级设计要求即可。因为此阶段的路径延迟并不准确,目的只是为了在实现开始前,尽量让综合的结果满足时序。并且在此阶段可能需要反复迭代 RTL 代码和 XDC 文件,以便查找各种网名和排除各种语法错误。

在 Elaborated Design 的创建过程中,某些 RTL 名称被修改或丢失。需要注意如下几点:

网表中寄存器的名称会比在 RTL 代码中的名称多一个 _reg 的后缀。

有些寄存器或网线会被吸收掉,例如二维寄存器会被综合成 Memory Block,乘除法会综合成 DSP。

在使用 get_* 查询路径时,最好不要使用 -hierarchical 参数,路径中使用/显示描述路径的层级。

不要对组合逻辑的网线附加约束。它们很可能会被合并到一个 LUT 中并从网表中消失。

1.4 创建实现约束

在某些情况下,综合网表中的对象名称与 Elaborated Design 中的名称不同。如果是这种情况,就必须使用正确的名称重新创建一些约束,并将它们保存在仅用于实现的 XDC 文件中。当工具可以正确加载所有 XDC 文件后,就可以运行时序分析以便:

添加缺少的约束,例如输入和输出延迟。

添加时序例外,例如伪路径、多周期路径和最小/最大延迟约束。

识别由于设计中的长路径而导致的严重违规,修改 RTL 代码。

在综合期间,为了提高设计性能,有些寄存器可能被复制。但综合器不会把复制的单元添加到用户 XDC 约束中。如要将时序约束附加到 Vivado Synthesis 复制的对象上,根据约束的写入方式不同,复制的单元有可能不会被 XDC 约束覆盖到,这可能会影响结果的实现质量。可以使用 -include_replicated_objects 参数来避免此问题。

例如 set_false_path –from [get_cells –hierarchical *rx_reg] 可以改为 set_false_path -from [get_cells -hierarchical *rx_reg -include_replicated_objects] 。

本文来源于网络:《Xilinx约束学习笔记—— 约束方法学》

边栏推荐

- 队列题目:无法吃午餐的学生数量

- request.getSession(), the story

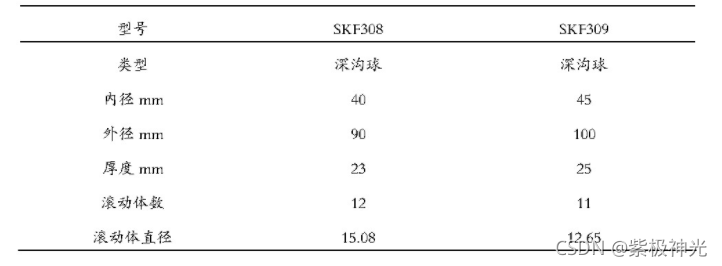

- 【故障诊断分析】基于matlab FFT轴承故障诊断【含Matlab源码 2001期】

- 论文阅读 (64):Weakly-supervised Video Anomaly Detection with Robust Temporal Feature Magnitude Learning

- optional

- 飞桨paddle技术点整理

- Submit code process

- [21天学习挑战赛——内核笔记](一)——设备树的概述(硬件、目标、效果、文件类型)

- 关于ue4.27像素流送打包后的本地服务器问题

- Vscode连接远程服务器出现‘Acquiring lock on/home/~’问题

猜你喜欢

随机推荐

雷达人体存在感应器方案,智能物联网感知技术,实时感应人体存在

2022年8月计划,着重ue4视频教程

【机器学习】实验5布置:AAAI会议论文聚类分析

_2_顺序表

牛客编程题中——需要处理输入较大数的题目

About the local server problem after ue4.27 pixel streaming package

nacos源码启动找不到istio包

Connection reset by peer 问题解析

Detailed explanation of 9 common reasons for MySQL index failure

【请教】SQL语句按列1去重来计算列2之和

第06章 索引的数据结构【2.索引及调优篇】【MySQL高级】

(部分不懂,笔记整理未完成)【图论】差分约束

File upload vulnerability (2)

System.Security.SecurityException: 未找到源,但未能搜索某些或全部事件日志。不可 访问的日志: Security

Submit code process

Analysis of GCC compiler technology

WebGPU 导入[2] - 核心概念与重要机制解读

关于ue4.27像素流送打包后的本地服务器问题

PWA 踩坑 - 第一次加载页面后无法获取CacheStorage某些资源

宝塔+FastAdmin 404 Not Found

——设备树的概述(硬件、目标、效果、文件类型)](/img/c6/6c2321bfcd184886e1cb59664bec11.png)