当前位置:网站首页>Difference between CMOS and TTL?

Difference between CMOS and TTL?

2022-07-31 02:19:00 【Electric competition bench】

TTL

BJT (transistor) integrated logic constitutes a chip or device

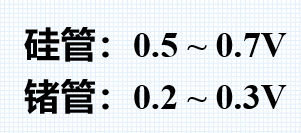

Turn on voltage:

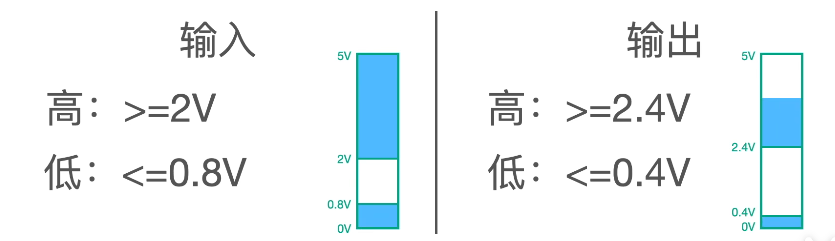

Why is 2V considered as input high level?

Take a NAND gate as an example: when A and B are both input at 2V, T1, 2, and 5 are fully turned on, and T4 is turned off, and the output is low;

Why is 0.8V considered as input low level?

And if one of the inputs of A and B is low level0.8V, the voltage of the emitter E point of T1 is pulled down, T1, 2, 5 are turned off, T4 is turned on, and the output is highlevel.

D1 and D2 act as clamps to limit the current to protect the device.

Common Types:

The 74 series that we commonly use now are TTL devices, and his level is judged to be the TTL level as the standard.In addition, there are the following types: high-speed H-TTL, low-power L-TTL, Schottky S-TTL, low-power Schottky LS-TTL

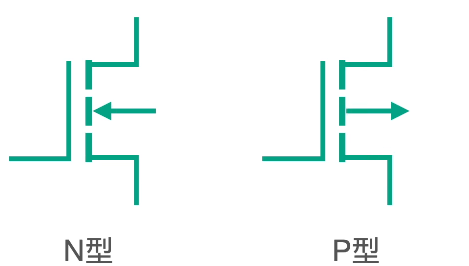

CMOS

Complementary symmetry is because both N-type MOS and P-type MOS appear in the circuit.

Input voltage characteristics: Supply voltage: 3-18V

Low: 0.3*VCC High: 0.7*VCC

Output Voltage Characteristics:

Low: 0.1*VCC High: 0.9*VCC

Common series:

74HC high-speed CMOS, 74HCT high-speed CMOS compatible with TTL, 74BCT bipolar compatible with TTL

(BiCMOS: The FET is used as the front stage and the middle stage; the triode is used as the output stage)

CMOS vs. TTL:

①TTL is a bipolar current control device, CMOS is a unipolar voltage control device

②The power supply voltage is different, TTL commonly used 5V power supply, CMOS: 5V, 3.3V, 2.4V, 1.8V

③TTL weak anti-interference ability and small noise tolerance, mainly because of the wide range of CMOS logic levels, the difference between the high-level threshold interval and the low-level intervalThe distance is large and the anti-interference ability is strong; but the CMOS device has large input impedance, which is easy to capture interference and has high noise.However, the output impedance of CMOS is low, in the range of KΩ; The unused input pins of CMOS devices must be grounded or fixed at a fixed level (ie, pay attention to electrostatic protection), while the pins of TTL devices are left floating and default to high level.

④TTL power consumption is high, CMOS power consumption is low, static power consumption is almost no, and level switching has high current.

⑤TTL devices work fast, with a transmission delay of 5~10ns; cmos transmission delay of 25~50ns.

Mutual drive analysis

Comparing the input and output levels of the two, it is obvious that TTL cannot directly drive CMOS devices, while the latter can directly drive the former; so TTL driving CMOS needs to add a pull-up resistor on the periphery, and TTL's VCC is connected to a resistor, high levelThe drive capacity is small.

边栏推荐

- cudaMemcpy study notes

- PDF split/merge

- Force buckled brush the stairs (7/30)

- Crawler text data cleaning

- 934. The Shortest Bridge

- Shell 脚本循环遍历日志文件中的值进行求和并计算平均值,最大值和最小值

- Fiddler captures packets to simulate weak network environment testing

- MySQL installation tutorial (detailed, package teaching package~)

- BAT卖不动「医疗云」:医院逃离、山头林立、行有行规

- C language applet -- common classic practice questions

猜你喜欢

基于FPGA的图像实时采集

Drools Rule Properties, Advanced Syntax

Static route analysis (the longest mask matching principle + active and standby routes)

静态路由解析(最长掩码匹配原则+主备路由)

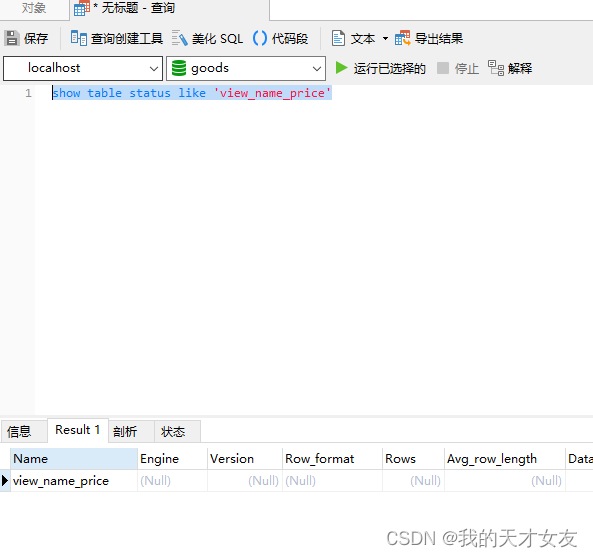

mysql 视图

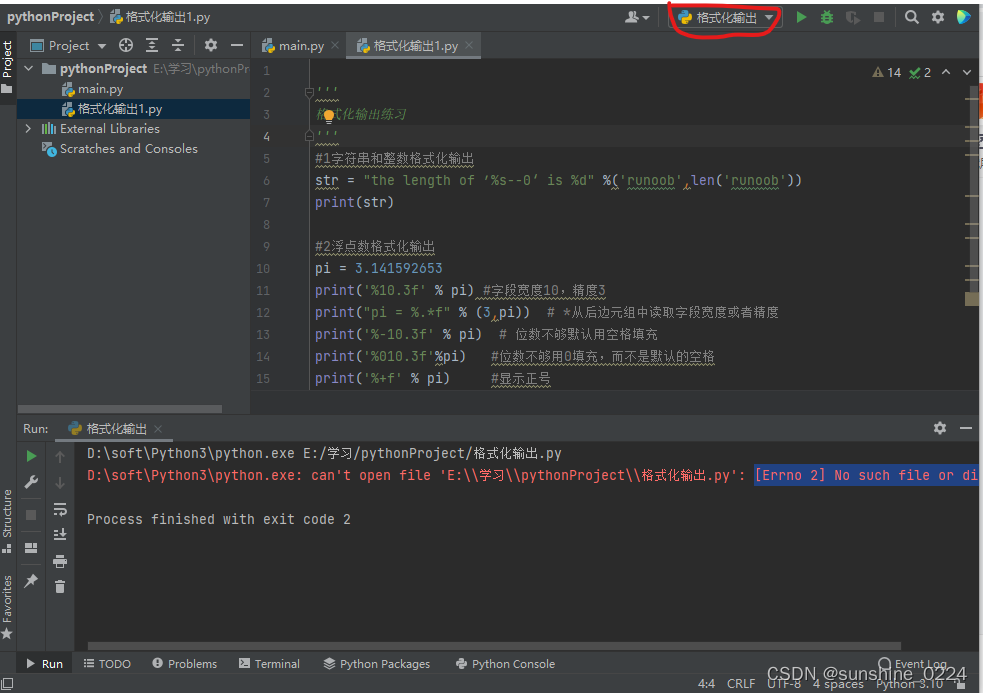

pycharm cannot run after renaming (error: can't open file...No such file or directory)

uniapp uses 3rd party fonts

![[Map and Set] LeetCode & Niu Ke exercise](/img/66/d812a6ad854cb0993c796760042150.png)

[Map and Set] LeetCode & Niu Ke exercise

真正的CTO,是一个懂产品的技术人

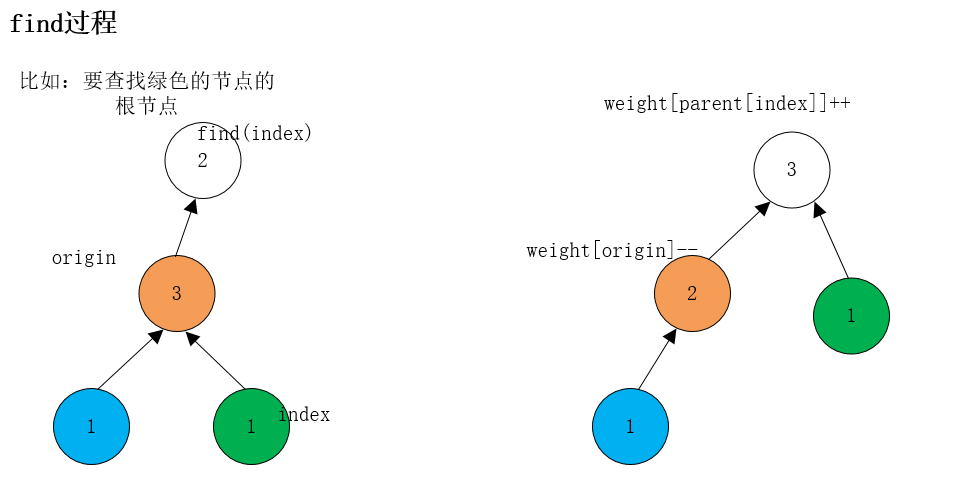

leetcode-952: Calculate max component size by common factor

随机推荐

[Map and Set] LeetCode & Niu Ke exercise

mmdetection trains a model related command

Brute Force/Adjacency Matrix Breadth First Directed Weighted Graph Undirected Weighted Graph

Brute Force/Adjacency List Breadth First Directed Weighted Graph Undirected Weighted Graph

Nacos

[1153] The boundary range of between in mysql

验证整数输入

934. 最短的桥

What level of software testing does it take to get a 9K job?

First acquaintance with C language -- array

曼城推出可检测情绪的智能围巾,把球迷给整迷惑了

CV-Model【3】:MobileNet v2

Introduction to flask series 】 【 flask - using SQLAlchemy

Refuse to work overtime, a productivity tool set developed by programmers

Force buckled brush the stairs (7/30)

Basic introduction to ShardingJDBC

完整复制虚拟机原理(云计算)

My first understanding of MySql, and the basic syntax of DDL and DML and DQL in sql statements

直播预告 | KDD2022博士论文奖冠亚军对话

汉源高科8路HDMI综合多业务高清视频光端机8路HDMI视频+8路双向音频+8路485数据+8路E1+32路电话+4路千兆物理隔离网络