当前位置:网站首页>OS interrupt mechanism and interrupt handler

OS interrupt mechanism and interrupt handler

2022-07-04 00:33:00 【Alkali!】

Interrupt plays a particularly important role in the operating system , It is the basis for the realization of multiprogramming , Without interruption , It is impossible to implement multiprogramming , because Switching between processes is accomplished through interrupts . On the other hand , Interruption is also the basis of device management , In order to improve the utilization of processor and realize CPU And I/O The device executes in parallel , There must also be support for interruptions . The interrupt handler is I / O The lowest layer in the system , It is the whole I / O Foundation of the system .

Interrupt profile

1. Break and fall into

1) interrupt

Interruption means CPU Yes I / O A response to an interrupt signal sent by a device . CPU Pause the running program , Retain CPU After environment , Automatically go to execute the I / O Device interrupt handler . After the execution , Back to the breakpoint , Continue with the original procedure . I / O The device can be a character device , It can also be a piece of equipment 、 Communication equipment, etc . Because the interrupt is caused by an external device , So it is also called external interrupt .

2) fall into

There's another one from CPU Caused by internal events interrupt , For example, the process has overflow or underflow in the operation , Another example is a program error , Such as illegal instructions 、 The address is out of bounds , And power failure . This kind of interrupt is usually called Internal interruption or trapping ( trap ). Like an interrupt , If the system finds a trap event , CPU The executing program will also be suspended , Go to execute the handler of the trapped event . The main difference between interrupt and trap is the source of the signal , That is, from CPU external , still CPU Inside .

2. Interrupt vector table and interrupt priority

1) Interrupt vector table

For the convenience of handling , Usually, each device is equipped with a corresponding interrupt handler , And put the entry address of the program in an entry of the interrupt vector table , And specify an interrupt number for the interrupt request of each device , It directly corresponds to an entry in the interrupt vector table . When I / O When the device sends an interrupt request signal , The interrupt controller determines the interrupt number of the request , Look up the interrupt vector table according to the interrupt number of the device , Get the entry address of the device interrupt handler , In this way, you can go to the interrupt handler to execute .

2) Interrupt priority

But the reality is : There are often multiple interrupt sources , Each interrupt source has different urgency to service requirements , for example , The interrupt request of the keyboard terminal is less urgent than that of the printer , And the urgency of the printer interrupt request is not as good as that of the disk . So , The system needs to specify different priorities for them .

3. How to deal with multiple interrupt sources

For the case of multiple interrupt sources , When the processor is processing an interrupt , Here comes a new interrupt request , How to deal with it . for example , When the system is processing a printer interrupt , A higher priority disk interrupt signal has been received . In this case , There are two ways to deal with :

- shielding ( prohibit ) interrupt

- Nested interrupts

1) shielding ( prohibit ) interrupt

When the processor is processing an interrupt , All interrupts will be masked , That is, the processor requests any new interrupt , Are temporarily ignored , And let them wait . Until the processor has finished processing this interrupt , The processor then checks whether an interrupt has occurred . If you have any , Then deal with the new interrupt , If there is no , Then return to the interrupted program . In this method , All interrupts will be processed sequentially . Its advantage is simplicity , But it cannot be used for interrupt requests that require high real-time performance . chart 6-9( a ) It shows a case when multiple interrupt sequence processing is prohibited .

2) Nested interrupts

In the system with interrupt priority set , Priority control is usually carried out according to such rules :

- (1) When there are multiple interrupt requests with different priorities at the same time , CPU Give priority to the interrupt request with the highest priority ;

- (2) High priority interrupt requests can preempt the processor of running low priority interrupts , This method is similar to priority based preemptive process scheduling . for example , The processor is processing a printer interrupt , When a disk outage comes , You can pause the processing of printer interrupts , Turn to disk interrupt . If the new one is keyboard interrupt , Because its priority is lower than that of the printer , So the processor continues to process the printer interrupt . chart 6-9( b ) Shows the case when multiple interrupts are possible .

Interrupt handler

When a process requests I / O In operation , The process will be suspended , until I / O Equipment complete I/O After the operation , The device controller sends a message to CPU Send an interrupt request , CPU After responding, it turns to the interrupt handler , The interrupt handler executes the corresponding processing , After processing, remove the blocking state of the corresponding process .

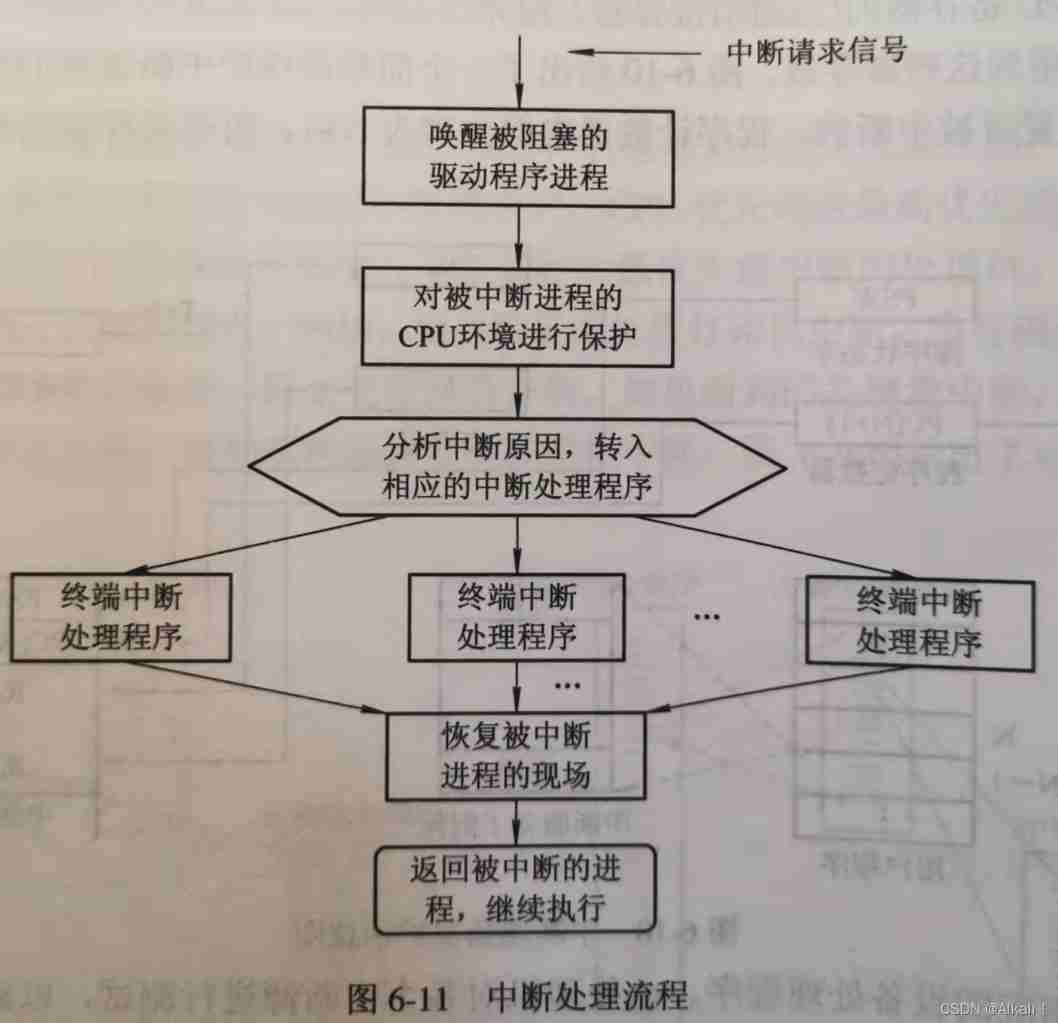

The process of interrupt handler can be divided into the following steps :

(1) Determine whether there are unresponsive interrupt signals

Whenever the device completes a character ( Words or data blocks ) Read in of ( Or output ), The device controller sends an interrupt request signal to the processor . The request processor transfers the data read by the device to the buffer in the memory ( Read in ), Or request the data to be output by the processor ( Output ) To the device controller . Every time the program finishes executing the current instruction , The processor should test whether there is any unresponsive interrupt signal . If there is no , Continue with next instruction . If you have any , Stop the execution of the original process , Prepare to transfer to execute interrupt handler , Prepare for transferring control of the processor to the interrupt handler .

(2) Protection of interrupted processes CPU Environmental Science

Before transferring control to the interrupt handler , You need to protect the interrupted process first CPU Environmental Science , So that the operation can be resumed later . The first thing to save is , Information needed to recover from the interruption site to the current process operation . The processor status word is usually automatically set by the hardware ( PSW ) And stored in the program counter ( PC ) The address of the next instruction in is saved in the interrupt reserve ( Stack ) in . then , Put the interrupted process CPU Site information , About to include all CPU The register of ( Such as general register 、 Segment register, etc ) The contents are pushed into the interrupt stack . Because these registers may be used in interrupt processing . chart 6-10 A simple schematic diagram of the protection interruption site is given . The program is instructed in N Position is interrupted , The contents in the program counter are N +1, The contents of all registers are kept on the stack .

(3) Go to the corresponding device handler

The processor tests each interrupt source , To determine the cause of this interruption I / O equipment , And send a confirmation signal to the equipment providing the interrupt signal . After the device receives the confirmation signal , Immediately cancel the interrupt request signal it sends . then , Load the entry address of the corresponding device interrupt handler into the program counter . such , When the processor is running , You can automatically turn to the interrupt handler .

(4) Interrupt handling

For different devices , There are different interrupt handlers . The program first reads the device status from the device controller , To judge whether this interrupt is a normal completion interrupt or an abnormal end interrupt . If the former , Interrupt the program and do the end processing . If this is the reading operation of the character device , The interrupt from the input device indicates that the device has read a character ( word ) The data of , And has been put into the data register . At this time, the interrupt processing shall transmit the data to CPU , Then store it in the buffer , And modify the corresponding buffer pointer , Make it point to the next memory unit . If there are orders , New commands can be sent to the controller , Carry out a new round of data transmission . If it is an abnormal end interrupt , Then deal with it according to the cause of the abnormality .

(5) recovery CPU And exit the interrupt

When the interrupt processing is completed , Recovery required CPU The scene of , Exit interrupt . however , Whether to return to the interrupted process at this moment , It depends on two factors :

- ① Whether this interrupt adopts shielding ( prohibit ) Interrupt mode , if , Will return to the interrupted process .

- ② Interrupt nesting is adopted , If there is no higher priority interrupt request I / O , After the interrupt is complete , The interrupted process will still be returned ; conversely , The system will process higher priority interrupt requests .

If you want to return to the interrupted process , The field information of the interrupted process stored in the interrupt stack can be taken out , And load it into the corresponding register , It includes the address of the next instruction executed by the program N +1、 Processor status word PSW , And the contents of general registers and segment registers . such , When the processor executes this program again , From N +1 Start at , Finally return to the interrupted program .

The interrupt processing flow is shown in the figure 6-11 Shown .

I / O After the operation is completed , The driver must check this I / O Whether there is an error in the operation , And report to the upper software , Finally, report this to the caller I/O Implementation of . In addition to the above paragraph 4 Out of step , Other steps are for all I / O The equipment is the same , So for some operating system , for example UNIX System , Is to put these common parts together , Form interrupt master control program . Whenever interrupt processing is required , You must first enter the interrupt master program . And for the first 4 Step , Then different equipment interrupt processing procedures must be used for different equipment to continue execution .

边栏推荐

- [cloud native topic -48]:kubesphere cloud Governance - operation - overview of multi tenant concept

- I would like to ask how the top ten securities firms open accounts? Is it safe to open an account online?

- Yyds dry goods inventory three JS source code interpretation - getobjectbyproperty method

- Test the influence of influent swacth on the electromagnetic coil of quartz meter

- system. Exit (0) and system exit(1)

- 【leetcode】300. Longest increasing subsequence (dynamic programming, dichotomy)

- Gossip about redis source code 82

- It is forbidden to splice SQL in code

- ISBN number

- No qualifying bean of type ‘com. netflix. discovery. AbstractDiscoveryClientOptionalArgs<?>‘ available

猜你喜欢

A dichotomy of Valentine's Day

Bodong medical sprint Hong Kong stocks: a 9-month loss of 200million Hillhouse and Philips are shareholders

![[C language] break and continue in switch statement](/img/ae/5967fefcf3262c9d3096e5c7d644fd.jpg)

[C language] break and continue in switch statement

![[2021]NeRF in the Wild: Neural Radiance Fields for Unconstrained Photo Collections](/img/c6/3dc7d01600f6713afdbb4cf3df5238.jpg)

[2021]NeRF in the Wild: Neural Radiance Fields for Unconstrained Photo Collections

From functional testing to automated testing, how did I successfully transform my salary to 15K +?

What does redis do? Redis often practices grammar every day

Sorry, Tencent I also refused

ESP Arduino playing with peripherals (V) basic concept of interrupt and timer interrupt

Ningde times and BYD have refuted rumors one after another. Why does someone always want to harm domestic brands?

Tencent interview: can you find the number of 1 in binary?

随机推荐

STM32 GPIO CSDN creative punch in

Severity code description the project file line prohibits the display of status error c4996 fopen ('fscanf ', StrCmp): this function or variable may be unsafe The most comprehensive solution

Suggestions for improving code quality

China standard gas market prospect investment and development feasibility study report 2022-2028

Correlation analysis summary

Report on the construction and development mode and investment mode of sponge cities in China 2022-2028

Recommendation of knowledge base management system

For loop

Makefile judge custom variables

It is worthy of "Alibaba internal software test interview notes" from beginning to end, all of which are essence

How to be a professional software testing engineer? Listen to the byte five year old test

[Mongodb] 2. Use mongodb --------- use compass

2022 system integration project management engineer examination knowledge points: software development model

Ningde times and BYD have refuted rumors one after another. Why does someone always want to harm domestic brands?

Detailed explanation of the relationship between Zhongtai, wechat and DDD

Sorry, Tencent I also refused

Qtcharts notes (V) scatter diagram qscatterseries

STM32 key light

[2021]NeRF in the Wild: Neural Radiance Fields for Unconstrained Photo Collections

Gossip about redis source code 83