当前位置:网站首页>易灵思T35 FPGA驱动LVDS显示屏

易灵思T35 FPGA驱动LVDS显示屏

2022-07-27 00:49:00 【ltqshs】

易灵思FPGA,天生适合MIPI/LVDS等相关应用,加上硬核DDR3控制器,简直就是完美。

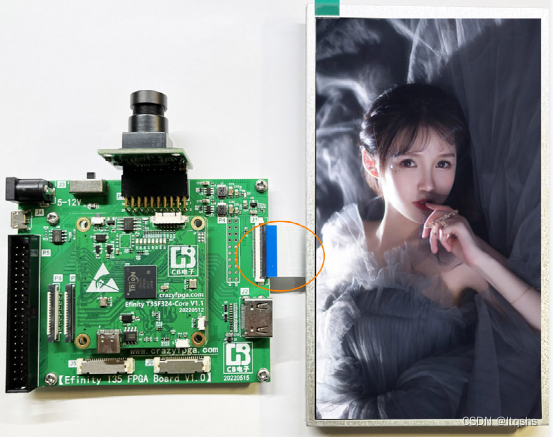

T35F324开发板支持LVDS LCD显示与HDMI显示,具体框图如下。这里,我将就花一定的篇幅,讲讲Trion系列FPGA T35的LVDS TX Hard IP如何使用,并且实战驱动我设计的1024*600的7寸 LVDS屏幕。

1.硬件介绍

如下图所示,为1024*600 LVDS LCD接口,这里直接与FPGA的LVDS IO对接驱动,其中相关Bank使用了3.3V电平。由于我在LCD驱动板侧已经处理好了所有的电源驱动,因此用户接口驱动,只需要给PWM与LVDS数据即可。

其中LVDS为1对差分时钟,4对差分数据线,查阅LCD手册(群创),相关的驱动协议如下所示(8bit DE模式,其中时钟采用了3:4占空比)

另外,1024*600的驱动时序,如下所示。这里时钟范围为 40.8~67.2MHz,并且时序与VGA Timing完全一样。我曾详细的介绍过如何驱动VGA显示器,这里在LVDS之前的RGB时序,是完全一样的。

所以我们的整体的Pipeline应该是这样的:lcd_driver <–> lcd_display --> LVDS Interface

2.Trion FPGA LVDS原理

打开Efinity软件,点击Help-Document,在Interface Designer中找到LVDS Interface,查询Trion系列FPGA的LVDS Interface,如下图所示:

可见LVDS是硬核心,并且支持800MHz LVDS速率,兼容2:1 ~ 8:1,并且FPGA片上已经集成了100R终端电阻,如下所示:

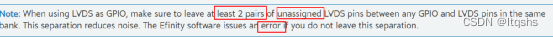

另外,如果LVDS bank用于GPIO,要求必须相邻2对unassigned LVDS pins,否则软件会报错

接着,以LVDS TX为例,我们打开相关的小节,可见文档给出的框图:

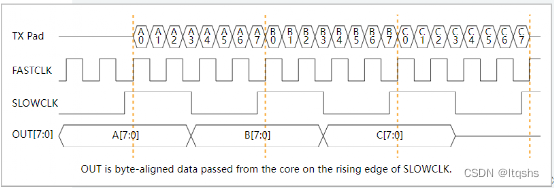

这里,由PLL产生fastclk与slowclk,供给Serializer,随后进行串行数据的输出。以n=7为例,help给出了如下时序图,即按照3:4,输出7bit的数据。

另外,需要注意的是在Using the Trion LVDS Block中,可见fastclk0与slowclk的关系。首先fastclk就是serial clock, slowclk就是parallel cock;其次,在Trion系列FPGA中,fastclk=slowclkn/2,那么当n=7时,fastclk=3.5slowclk。

3.LVDS TX设计流程

分析完Trion FPGA的LVDS TX特性,我们有米可炊,直接上刀,如下:

1)首先,File→Create Project,创建工程,选择对应的器件

2)接着加入已有的代码(99.9%的人都是移植,不会在国产上初学吧)

3)然后,打开Interface,配置时钟、引脚、PLL,以及锁相环等

a.Create Block创建IO,包括clk、lcd_pwm控制信号

这如果是GPIO,选择输入或者输出;如果是clk,则还得哪一类时钟,如下所示:

这里我们定义pll_clkin,硬件上已经连接到PLL_CLKIN引脚,不可当作其他用途,如下:

b.然后配置引脚,对着原理图操作,这里会显示Resource,如下所示:

c.接着设置PLL,在PLL处Create Block,创建tx_pll如下。这里需要选择PLL_BR0,对应clk输入的引脚,硬件固定是GPIOR_138。

d.打开Automated Clock Calculation,配置时钟输入为24MHz,输出慢时钟48MHz,快时钟=慢时钟*3.5=168MHz(lvds=7bit),并且快时钟需要90度phase,以及txpll_locked,GUI配置如下(与前面分析一致):

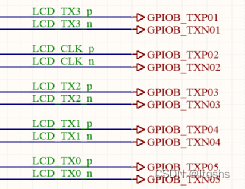

e.最后,配置LVDS IO,如下所示,其中要注意LVDS Resource的选择,以及Serialization Width=7,并且选择tx_fastclk的名字,软件会自动根据该Name进行wire:

这里的LVDS TX或者CLK,与硬件原理图中的分配必须一致,如下:

图片

f.最后,Generate Efinity约束文件,如果有错误此时会报出,比如没有90°,或者倍率不对,IO分配不对等。这一步完成后生成了工程的约束文件,包括顶层空壳等。

生成的文件,可在Result中的Interface查看,如下,其中特别关注sdc与template.v

4)LCD_LVDS_Test_1024600.v顶层代码的修改

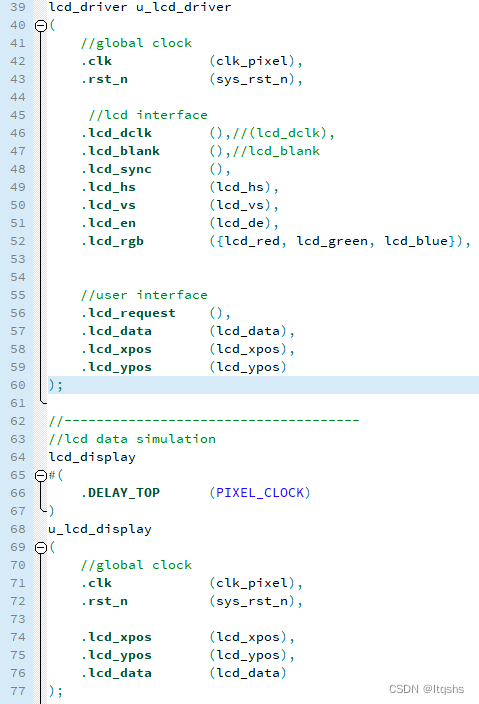

上一步中,软件帮我们生成了顶层的template.v,如下所示:

可见PLL的输出时钟,直接作为我们逻辑的输入时钟使用;另外,LVDS我们只需要输处配置好的7bit串行化的时钟与数据,此外我们并不需要例化PLL、LVDS IP等。这个初次见面,真的就非常奇特了。

a.于是乎,我们顶层的接口就变成了这样。这里像素时钟自然是慢时钟,clk和fast时钟不需要用我们注释掉即可:

b.正常例化rgb lcd驱动代码,如下:

c.将rgb及de数据送给lvds port,这里就有点坑了,一开始没有研究时序,如下:

这里7bit并转串传输时,先发送的是lsb,然后才是msb,因此rgb驱动的代码还需要转一下,操作如下(最初的时候想当然以为是msb,浪费了好多宝贵的时间):

5)最后,在dashboard中双击图标,进行一系列的编译、综合、布局布线,并最终生成目标bit文件。

关于设计占用的资源,可以在左侧的Result中查看,如下所示,占用了一个PLL,5个LVDS:

6)上板验证,打开Programmer,选择bit文件,下载到FPGA后,终于点亮了LVDS屏幕,万事开头难就,如下:

4.Trion FPGA LVDS总结

最终总结一下,易灵思Trion FPGA的LVDS TX IP相关注意事项:

1)首先fastclk = n/2 * slowclk;

2)其次一定要记得fastclk 有90deg的相位

3)再者串行数据是先发LSB,再发MSB的。

4)最后LVDS TX Hard IP配置好后,直接在代码顶层使用,无需再例化。

版权声明,本文来自于网络:《易灵思T35 FPGA驱动LVDS显示屏》。

边栏推荐

- Scheduling of processes

- ZJCTF_login

- 2649: 段位计算

- Use the most primitive method to manually implement the common 20 array methods

- Ansible series: do not collect host information gather_ facts: False

- HCIP第十四天笔记

- day6

- 身家破亿!86版「红孩儿」拒绝出道成学霸,已是中科院博士,名下52家公司

- Alibaba cloud technology expert Yang Zeqiang: Construction of observability on elastic computing cloud

- Common questions and answers of software testing interview (divergent thinking, interface, performance, concept,)

猜你喜欢

QT编译出来的exe以管理员权限启动

5、 MFC view windows and documents

Cloud development sleeping alarm clock wechat applet source code

关于url编解码应该选用的函数

1.28亿美元!芬兰量子计算公司IQM获世界基金支持

数模1232

What is a process?

Cuteone: a onedrive multi network disk mounting program / with member / synchronization and other functions

Static keyword

LabVIEW中编程更改进程的优先级

随机推荐

身家破亿!86版「红孩儿」拒绝出道成学霸,已是中科院博士,名下52家公司

小玩一个并行多线程MCU—MC3172

如何使用DevExpress WPF在WinUI中创建第一个MVVM应用程序?

调用JShaman的Web API接口,实现JS代码加密。

基于.NetCore开发博客项目 StarBlog - (16) 一些新功能 (监控/统计/配置/初始化)

MarqueeView实现滑动展示效果

Integrated water conservancy video monitoring station telemetry terminal video image water level water quality water quantity flow velocity monitoring

Portraiture5全新升级版磨皮滤镜插件神器

OpenTelemetry 在服务网格架构下的最佳实践

Baidu cloud face recognition

Plato Farm通过LaaS协议Elephant Swap,为社区用户带来全新体验

My crawler notes (VII) blog traffic +1 through Crawlers

五、MFC视图窗口和文档

Analysis of [paper] pointlanenet papers

Debezium系列之:基于debezium offset拉取历史数据,确保数据没有丢失

196. 删除重复的电子邮箱

Complete source code of mall applet project (wechat applet)

Leetcode- > binary search clock in

Kubernetes Dashboard 部署应用以及访问

1.28亿美元!芬兰量子计算公司IQM获世界基金支持