当前位置:网站首页>CPU design practice - Chapter 4 practical tasks - simple CPU reference design and debugging

CPU design practice - Chapter 4 practical tasks - simple CPU reference design and debugging

2022-07-01 08:13:00 【서리가 가장 아름답다.】

Simple CPU Refer to the design and commissioning DeBug—MyCPU part

Make a note of it :

Run All Options are only available after entering the simulation page , And the process of its operation is prompted in the lower right corner .

1. Signal transmission Bug

Add five paragraphs respectively PC The signal value is not difficult to find ,IF_PC => ID_PC Fail to pass EXE_PC, That is, the execution stage does not receive the... From the decoding stage PC value . The inspection found that :

if Send the data to id, however id_stage There is no fs_to_ds_bus_r <= fs_to_ds_bus. Go to id modular , Find out ds_valid Not assigned .

Before the change :

After modification :

always @(posedge clk) begin // Bug 1

if(reset) begin

ds_valid <= 1'b0;

end

else if(ds_allowin) begin

ds_valid <= fs_to_ds_valid;

end

if (fs_to_ds_valid && ds_allowin) begin

fs_to_ds_bus_r <= fs_to_ds_bus;

end

end

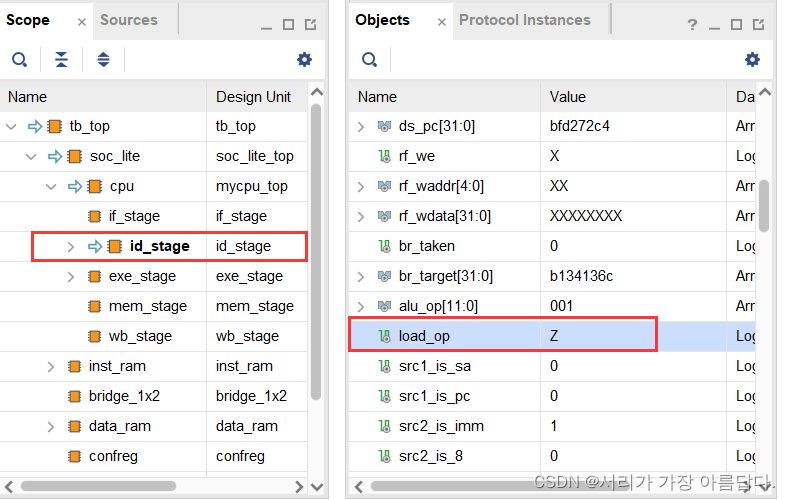

2. A typical "Z" The signal Bug

This situation is often caused by the fact that variables are not assigned values . find id_stage Module discovery :

load_op There is no relevant assignment statement . Add it at the right place :

load_op It means load Of operate Part this part should be related to lw Instructions are connected .

Simulation Bug episode

Complete the above logic Bug, Re simulate , The following episode appears :

Most of this prompt is due to the wrong typing of some variables when typing the code , So don't panic . Click on ok You can view the file path where the problem is accurately located :

Open it in Notepad and you can see the precise error location .

my Bug It is positioned as :ID.stage Of the 128 Line and line three

Use new tools - be based on Trace Debugging of comparison

3.Addiu The instruction instance passes parameters Bug

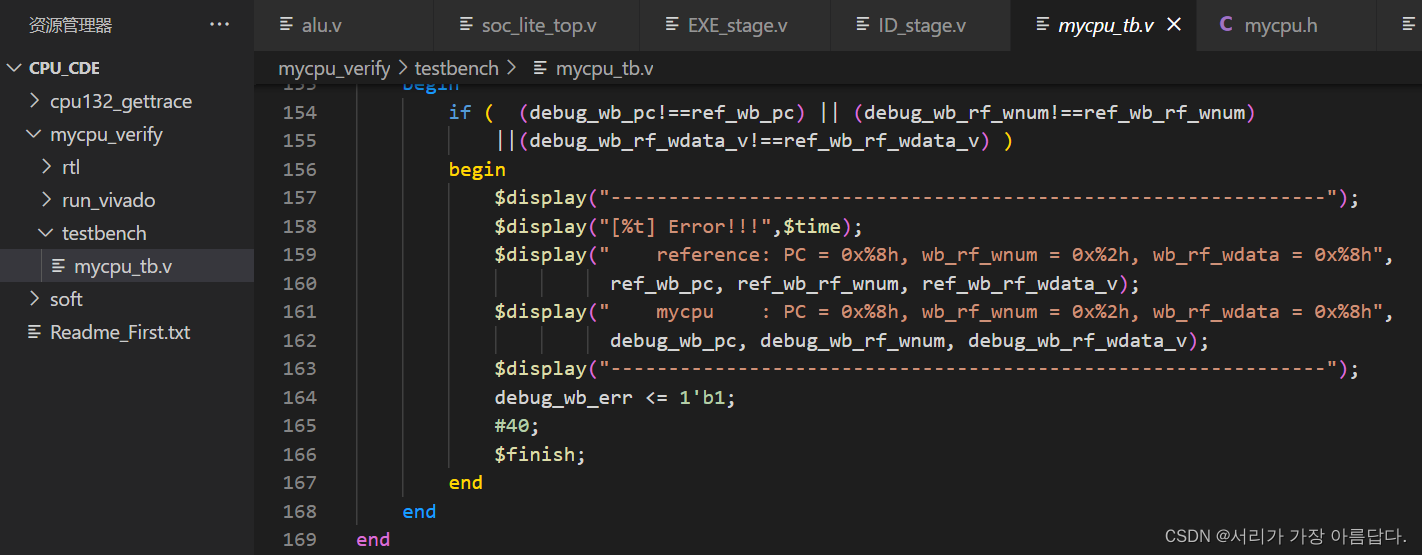

Run All Then the first trace Comparison error , The comparison error message prompt comes from the following related codes :

It can be seen that the relevant information of the comparison is :PC value 、 Write back destination register 、 Destination data written back

analysis :PC The value is 0x bfc00000, Which instruction does it represent ?

stay lab3\CPU_CDE\soft\func_lab3\obj\test.s Mid search bfc00000 You can see the corresponding instruction :

by 0x2408 ffff Its corresponding instruction 001001 00000 01000 1111111111111111

Look up the table , The corresponding instruction format is addiu Instructions , And the error position is on the written data , So we need to check alu Module and EXE_stage modular , Find out :

EXE_stage Module parameter instantiation error

Change to :

alu u_alu(

.alu_op (es_alu_op ),

.alu_src1 (es_alu_src1 ),

.alu_src2 (es_alu_src2 ),

.alu_result (es_alu_result)

);

4.Bug

You can see PC Something went wrong , It must be looking for branch instructions or jump instructions , Let's take a look at some instructions nearby (test.s file ).

/media/sf_func_lab3/start.S:19

bfc00004: 2408ffff li t0,-1

/media/sf_func_lab3/start.S:20

bfc00008: 100000e0 b bfc0038c <locate>

/media/sf_func_lab3/start.S:21

bfc0000c: 00000000 nop

/media/sf_func_lab3/start.S:24

bfc00010: 3c088000 lui t0,0x8000

/media/sf_func_lab3/start.S:25

bfc00014: 25290001 addiu t1,t1,1

It is obvious that bfc00008 This instruction is a branch instruction , and mycpu No jump .

First of all, let's explain nop Instructions , It is kind to set the delay slot instruction to nop, Same as above ,nop Instructions do not need to be specifically implemented .

The control flow first flows into the prefetch stage , Then prefetching refers to phase update PC And visit RAM Get instruction ,PC and RAM Finally, it flows into the decoding stage at the same time , In the decoding stage, the prefetching stage is controlled by combinatorial logic to complete the jump .

We Expected execution sequence

You can see , In our expectation , The pre judgment of branch instruction is completed by the decoding stage .

This article B Instructions from r0 Constant for the 0 and BEQ Command to get .

We can find that in this delay slot instruction , It should have been assign br_bus = {br_taken,br_target};, But the two signals at the bottom are the same , So you can find the problem .

The problem occurred in the file path :\lab3\CPU_CDE\mycpu_verify\rtl\myCPU\mycpu.h

Change the bit width :

`define BR_BUS_WD 33

5.Bug

Global error

This mistake is still alu modular ( Before and after bit width mismatch assignment ):

change :

assign sr_result = sr64_result[31:0];

6.Bug

This situation is caused by RTL There is a combined circuit in the code , Hard to find , If you happen to see this line , Its mistakes are still obvious .

alu.v Module error :

change :

assign or_result = alu_src1 | alu_src2;

PC-Bug episode

After solving the above problems in turn , Re run and find this phenomenon ...

Observation found that : Every time an error is reported, it is written back to the level PC And trace.txt atypism , But the destination register number and data are correct . What causes it ?

7. the last one Bug

Bad file path :mycpu_verify => rtl => myCPU => tools.v

If you are more careful, you will find decoder_6_64 The decoding of the module is not enough 64 position , That is, only 【62:0】, So it should be changed to :

generate for (i=0; i<64; i=i+1) begin:gen_for_dec_6_64 //Bug 7

Successful board video presentation :

It is recommended to turn on all dialing switches during board test , At this time, the counting speed is the slowest , It is convenient to observe experimental phenomena . Then you can dial oneortwo , Moderate speed .

Video link : Simple CPU Design reference practice task

Reference resources :

Learn from relevant blog links :CPU Design practice lab3

边栏推荐

- Li Kou daily question - day 31 -1502 Judge whether an arithmetic sequence can be formed

- 【网站架构】一招搞定90%的分布式事务,实打实介绍数据库事务、分布式事务的工作原理应用场景

- 谈谈数字化转型的几个关键问题

- Access report realizes subtotal function

- [untitled]

- SharePoint - how to quickly check whether SharePoint is standard or enterprise edition?

- Transaction method call @transactional

- Differential: definition of total differential, partial derivative, gradient

- Deep learning systematic learning

- Office365 - how to use stream app to watch offline files at any time

猜你喜欢

web254

![[batch DOS CMD summary] extension variables - delay variables CMD /v:on, CMD /v:off, SETLOCAL enabledelayedexpansion, disabledelayedexpansion](/img/ce/6c9e4f2c54710610e8b1f68d6d8088.png)

[batch DOS CMD summary] extension variables - delay variables CMD /v:on, CMD /v:off, SETLOCAL enabledelayedexpansion, disabledelayedexpansion

使用beef劫持用户浏览器

7-26 word length (input and output in the loop)

Utiliser Beef pour détourner le navigateur utilisateur

【入门】截取字符串

window c盘满了

![[staff] key number (key number identification position | key number marking list | a major key identification principle | F, C, G position marking ascending | F major key identification principle | B](/img/48/e98d01830867baa742574e1b6e1096.jpg)

[staff] key number (key number identification position | key number marking list | a major key identification principle | F, C, G position marking ascending | F major key identification principle | B

SharePoint - modify web application authentication using PowerShell

如何使用layui将数据库中的数据以表格的形式展现出来

随机推荐

Rumtime 1200 upgrade: London upgrade support, pledge function update and more

Anddroid text to speech TTS implementation

slice扩容机制分析

5大组合拳,解决校园6大难题,护航教育信息化建设

Li Kou daily question - day 31 -202 Happy number

Connect timed out of database connection

Gdip - hatchbrush pattern table

go通用动态重试机制解决方案的实现与封装

Vhost kick & call principle

Airsim radar camera fusion to generate color point cloud

Transaction method call @transactional

源代码加密的意义和措施

【入门】截取字符串

postgresql源码学习(26)—— Windows vscode远程调试Linux上的postgresql

Android screen adaptation (using constraintlayout), kotlin array sorting

Gdip - hatchBrush图案表

Scala语言学习-07-构造器

Uni hot update

Rk3399 platform development series explanation (network debugging) 7.30. What will affect the sending process of TCP packets?

php laravel微信支付