当前位置:网站首页>Understand chisel language. 26. Chisel advanced input signal processing (II) -- majority voter filtering, function abstraction and asynchronous reset

Understand chisel language. 26. Chisel advanced input signal processing (II) -- majority voter filtering, function abstraction and asynchronous reset

2022-07-27 09:41:00 【github-3rr0r】

Chisel Advanced input signal processing ( Two )—— Majority voter filtering 、 Function abstraction and asynchronous reset

In the last article, we used a few lines of code to realize the synchronization and de jitter of asynchronous input signals , Enough to cope with the asynchronous jitter input of buttons and switches . In this article, we continue with input signal processing , Further solve the possible noise problem , Try adding a noise filter to the input signal , And use functions to abstract and integrate these processing methods , Finally, we will briefly discuss the synchronization of reset signals .

Input signal filtering

Sometimes our input signal may have noise , There may be some burrs , These are what we don't want to get through input synchronizer and de jitter unit sampling . One option is to use Majority voting circuit To filter these burrs , The simplest case is to accept three samples and then perform a majority vote . This Majority function (Majority Function) Is and median function (Median Function) dependent , The return value is most of the values . On this occasion , We use sampling to shake , Then perform majority voting on the sampled signal . Majority voting can ensure that the signal stability time can be longer than the sampling period .

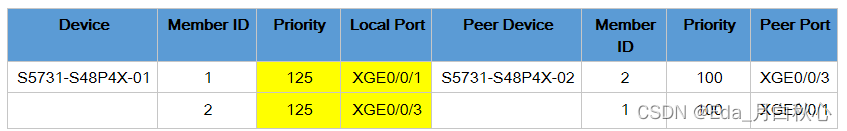

The following figure shows the circuit of the majority voter :

This voter contains a three bit shift register , The shift register is composed of tick Signal driven . The output of the three registers is input to the majority voter , Then the majority voting function will filter out any signal changes shorter than the sampling period .

Below Chisel The code is the implementation of a three bit shift register , from tick Signal driven , The three bit value of the register is input to the majority voter and a signal is obtained btnClean:

val shiftReg = RegInit(0.U(3.W))

when (tick) {

// Shift left and enter the least significant bit

shiftReg := shiftReg(1, 0) ## btnDebReg

}

// A majority vote

val btnClean = (shiftReg(2) & shiftReg(1)) | (shiftReg(2) | shiftReg(1)) | (shiftReg(1) | shiftReg(0))

In order to use the output of this carefully processed input signal , We first need to use a RegNext Delay the unit to detect the rising edge , That is, compare the signal with the current btnClean value , If it is on the rising edge , Then the counter value is increased by one :

val risingEdge = btnClean & !RegNext(btnClean)

// Use to shake 、 The filtered button signal drives the counter to increase automatically

val reg = RegInit(0.U(8.W))

when (risingEdge) {

reg := reg + 1.U

}

The input signal processing process is abstracted as a function !

In this part, we summarize the input signal processing . For now , The previous input signal processing related Chisel The code is not long , But they are all reusable blocks , So we can consider putting them all into the function . As mentioned earlier, how to abstract small modules into lightweight Chisel Function , These functions create hardware instances , such as sync Function will create two triggers to connect input and other circuits , Function will return the output of the second trigger . If it works , These functions can also be used as objects of some tool classes .

The input signal processing process is abstracted as the function code as follows :

// Input signal synchronization

def sync(v: Bool) = RegNext(RegNext(v))

// Rising edge detection

def rising(v: Bool) = v & !RegNext(v)

// tick Generate

def tickGen(fac: Int) = {

val reg = RegInit(0.U(log2Up(fac).W))

val tick = reg === (fac - 1).U

reg := Mux(tick, 0.U, reg + 1.U)

tick

}

// filter

def filter(v: Bool, t: Bool) = {

val reg = RegInit(0.U(3.W))

when (t) {

reg := reg(1, 0) ## v

}

(reg(2) & reg(1)) | (reg(2) & reg(0)) | (reg(1) & reg(0))

}

Now we can easily use these signal processing functions :

// Use of signal processing functions

val FAC = 100000000 / 1000

// Synchronization

val btnSync = sync(io.btnU)

// Sampling de dithering

val tick = tickGen(FAC)

val btnDeb = Reg(Bool())

when (tick) {

btnDeb := btnSync

}

// wave filtering

val btnClean = filter(btnDeb, tick)

// Detect the rising edge

val risingEdge = rising(btnClean)

// Use the rising edge of the processed signal to drive the counter

val reg = RegInit(0.U(8.W))

when (risingEdge) {

reg := reg + 1.U

}

Synchronization of reset signal

All digital circuits need a reset signal to reset the register to the defined state , stay Chisel The reset state of the register in passes RegInit Constructor settings . The reset signal is usually an asynchronous signal input to the circuit , This means that directly connecting the reset input to the reset control of the circuit may lead to the violation of timing constraints . In the case of asynchronous reset , It may violate the establishment and holding time of triggers , Therefore, in the case of asynchronous reset , Still need to synchronize with the clock . say concretely , The release of the reset signal needs to be synchronized with the clock . Then another problem of asynchronous reset is that different parts of the circuit may be reset in two different clock cycles , To cause inconsistency .

The solution is to process the reset signal with two triggers like other asynchronous input signals .

Chisel Reset signal and clock signal are usually hidden in the design , But we can access and set them . Each module has an implicit reset Field . The solution is a whole top-level module , This top-level module performs synchronization of external reset signals , And connect the synchronous reset signal with all modules that need reset signals , For example, the following code is as follows :

class SyncReset extends Module {

val io = IO(new Bundle {

val value = Output(UInt())

})

val syncReset = RegNext(RegNext(reset))

val cnt = Module(new WhenCounter(5))

cnt.reset := syncReset

io.value := cnt.io.cnt

}

SyncReset It's a counter WhenCounter The top module of . The reset signal of the top-level module is called reset, It is connected to the input synchronizer RegNext(RegNext(reset)) On . Then input the output of synchronizer syncReset And connected to the reset input of the counter (cnt.reset := syncReset).

Conclusion

That's all for the input signal processing , In addition to understanding the process of input signal processing , We also have a deeper understanding of the timing of asynchronous signals . At the end of this part , We also use the method of function abstraction to encapsulate simple small modules into functions for convenient invocation , If used a lot , We can also put these functions into similar utils In the class of . In the next part, let's continue Chisel Advanced content of , This paper discusses the finite state machine which is very important in digital design , And lay the foundation for the communication of the later state machine .

边栏推荐

- 2022软件测试面试题 200道大厂面试真题 刷完拿到10k职位

- Talk about 10 scenarios of index failure. It's too stupid

- How to use tdengine sink connector?

- wordpress禁止指定用户名登录或注册插件【v1.0】

- 七月集训(第10天) —— 位运算

- 【武汉理工大学】考研初试复试资料分享

- swagger-editor

- 七月集训(第23天) —— 字典树

- July training (day 21) - heap (priority queue)

- Google Earth Engine APP——利用S2影像进行最大值影像合成分析

猜你喜欢

![[untitled]](/img/03/dcea9137dc9948e3121333c684ec8f.png)

[untitled]

Sentinel 万字教程 | 文末送书

ArcGIS pro2.8 deep learning environment configuration based on rtx30 graphics card

一骑入秦川——浅聊Beego AutoRouter是如何工作

S交换机堆叠方案配置指南

35 spark streaming backpressure mechanism, spark data skew solution and kylin's brief introduction

1344. Included angle of clock pointer

vscode使用remote-ssh连接以及连接失败的解决方法

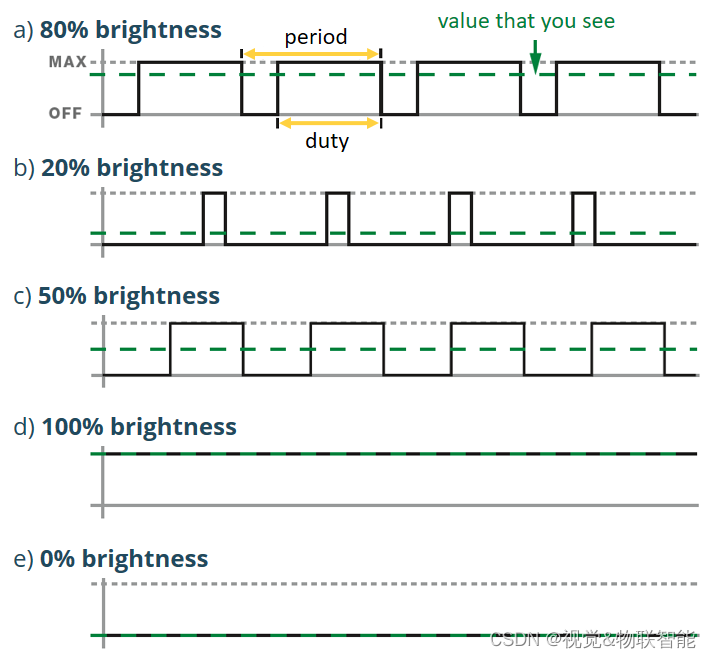

Esp8266 Arduino programming example PWM

C# 给Word每一页设置不同文字水印

随机推荐

July training (day 21) - heap (priority queue)

【CTF】ciscn_2019_es_2

七月集训(第24天) —— 线段树

七月集训(第06天) —— 滑动窗口

July training (day 15) - depth first search

基于 FPGA 按键控制呼吸灯原理、仿真及验证全过程

关于getter/setter方法问题

July training (day 10) - bit operation

七月集训(第18天) —— 树

The whole process of principle, simulation and verification of breath lamp controlled by FPGA keys

快应用JS自定义月相变化效果

七月集训(第23天) —— 字典树

Run uni app project in hbuilder wechat applet

为什么微服务一定要有API网关?

BGP federal experiment

vscode使用remote-ssh连接以及连接失败的解决方法

Google Earth Engine APP——打印点的坐标到控制台上和map上,设置样式并更新

ESP8266-Arduino编程实例-ADC

Esp8266 Arduino programming example - interrupt

[untitled]