当前位置:网站首页>[Verilog quick start of Niuke question series] ~ use functions to realize data size conversion

[Verilog quick start of Niuke question series] ~ use functions to realize data size conversion

2022-07-01 14:25:00 【AI is very good】

0. Preface

0.1 Knowledge point investigation

The investigation is :

- function function Knowledge points of ;

- Understand big end and small end . Portal

0.2 Knowledge development

function and task The definition and difference of ?

This problem has been summarized before , Direct old rules , Poke an eye , Portal

1. VL10 Use function to realize data size conversion

1.1 Title Description

In digital chip design , Modules that implement specific functions are often written as function , Call again in the middle note module when needed. , In order to improve the reusability of code and improve the level of design , Subsequent modifications are made separately .

Please implement a function 4bit Function of data size conversion . Realize the conversion and output of two different inputs respectively .

1.1.1 Signal schematic diagram

1.1.2 Waveform diagram

This question is not officially given .

1.1.3 Input description

clk: The system clock

rst_n: Asynchronous reset signal , Low level active

a,b:4bit Unsigned number of bits wide

( Pay attention to is : The official code does not state clk and rst_n, Pay attention to add it by yourself when submitting !!!)

1.1.4 Output description

c,d:4bit Unsigned number of bits wide

( This should be an official clerical error , Four is right )

1.2 Their thinking

The main thing is to investigate function Details of , The subject itself is not difficult , That is, the big end and the small end are converted . These knowledge points have been explained in the preface of this article , To view the .

1.3 Code implementation

`timescale 1ns/1ns

module function_mod(

input clk,

input rst_n,

input [3:0]a,

input [3:0]b,

output [3:0]c,

output [3:0]d

);

function [3:0] big22small;

input [3:0] big_small;

begin

big22small[0] = big_small[3];

big22small[1] = big_small[2];

big22small[2] = big_small[1];

big22small[3] = big_small[0];

end

endfunction

assign c = big22small(a);

assign d = big22small(b);

endmodule

1.4 The test file

To be changed ...

1.5 Simulation waveform

To be changed ...

边栏推荐

- Provincial election + noi Part VIII fraction theory

- Provincial election + noi Part IX game theory

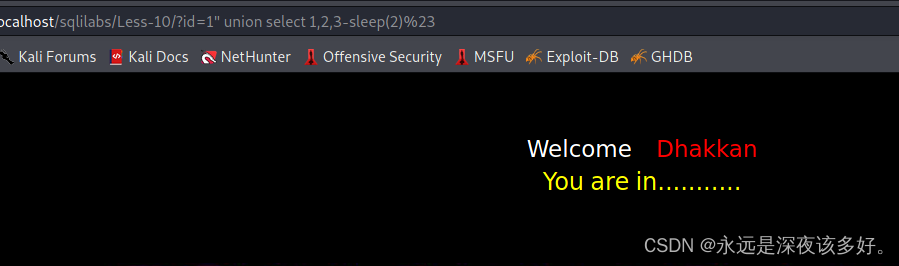

- sqlilabs less10

- [repair version] imitating the template of I love watching movies website / template of ocean CMS film and television system

- Research Report on the development trend and competitive strategy of the global powder filling machine industry

- 深度合作 | 涛思数据携手长虹佳华为中国区客户提供 TDengine 强大企业级产品与完善服务保障

- Sqlachemy common operations

- 使用 Lambda 函数URL + CloudFront 实现S3镜像回源

- Play with grpc - communication between different programming languages

- sqlilabs less9

猜你喜欢

sqlilabs less13

Leetcode(69)——x 的平方根

![[dynamic programming] p1004 grid access (four-dimensional DP template question)](/img/3a/3b82a4d9dcc25a3c9bf26b6089022f.jpg)

[dynamic programming] p1004 grid access (four-dimensional DP template question)

sqlilabs less-11~12

TDengine 连接器上线 Google Data Studio 应用商店

玩转MongoDB—搭建MongoDB集群

sqlilabs less10

【牛客网刷题系列 之 Verilog快速入门】~ 多功能数据处理器、求两个数的差值、使用generate…for语句简化代码、使用子模块实现三输入数的大小比较

佩服,阿里女程序卧底 500 多个黑产群……

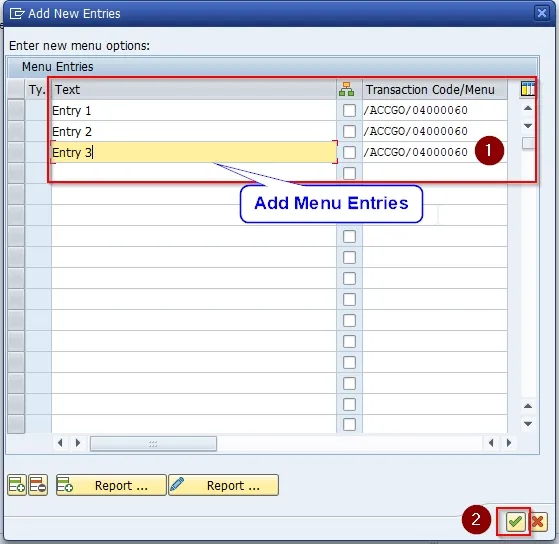

This paper introduces an implementation scheme to enhance the favorite transaction code management tool in SAP GUI

随机推荐

This paper introduces an implementation scheme to enhance the favorite transaction code management tool in SAP GUI

sqlilabs less13

C language course design topic

Admire, Ali female program undercover more than 500 black production groups

Tdengine connector goes online Google Data Studio app store

Research Report on the development trend and competitive strategy of the global traditional computer industry

sqlilabs less9

Opencv interpolation mode

How to pass array parameters in get request

Research Report on the development trend and competitive strategy of the global axis measurement system industry

[commercial terminal simulation solution] Shanghai daoning brings you Georgia introduction, trial and tutorial

Research Report on the development trend and competitive strategy of the global high temperature label industry

How to view the state-owned enterprises have unloaded Microsoft office and switched to Kingsoft WPS?

佩服,阿里女程序卧底 500 多个黑产群……

Why did you win the first Taosi culture award of 20000 RMB if you are neither a top R & D expert nor a sales Daniel?

QT community management system

QT learning management system

Research Report on the development trend and competitive strategy of the global display filter industry

【R语言数据科学】:机器学习常见评估指标

Basic concepts of programming