当前位置:网站首页>SystemVerilog join and copy operators

SystemVerilog join and copy operators

2022-07-29 01:01:00 【Broken thoughts】

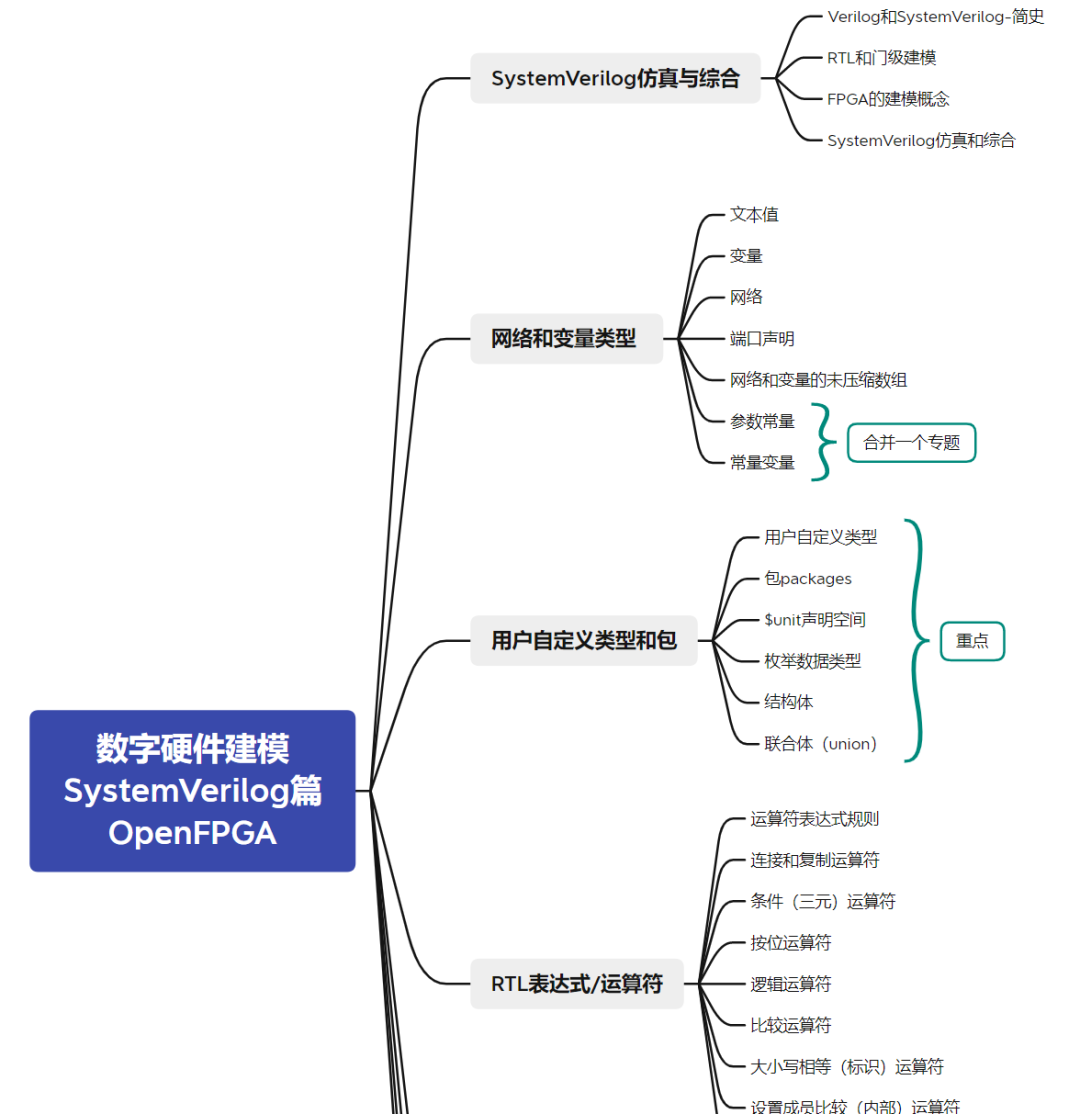

Digital hardware modeling SystemVerilog- Join and copy operators

After several weeks of updates ,SV The core user-defined types and package contents have been updated , The next step is RTL Expressions and operators .

immediately HDLBits-SystemVerilog The version is also ready , After the basic part is completed, it will be updated ~

Introduce

Join and copy operators join multiple expressions , Form a vector expression . The total number of bits in the result vector is the sum of all bits in each sub expression . There are two forms of connection , Simple connection and replication connection . A simple join joins any number of expressions together . Copy join joins expressions together , Then copy the result of the specified number of times . surface 5-3 Shows the general syntax and usage of join and copy operators :

surface 5-1:RTL Modeled join and copy operators

The following variables and values are used to display the results of these operators .

{a,b} The result is 101100010001( Binary system ), One 12 The value of a .

{4’hF,a} The result is 1111_1011( Binary system ), One 8 The value of a .

{8{2’bl0}} The result is 1010101010101010( Binary system ), One 16 The value of a ,2’b01 repeat 8 Time .

{ {4{a[3]}},a} The result is 11111011( Binary system ) One 8 The value of a , a The significand of is repeated 4 Time , Then connect to a.

Join and copy operators are integrable . Operators do not directly represent any logical functions in hardware . They just mean using multiple signals at the same time , Attach a text value to a signal or text value .

Example 5-1 and 5-2 It shows that the connection operator is in RTL Two common applications in modeling :

Connect multiple signals to the right or left of the assignment statement . After each example , chart 5-1 and 5-2 It shows how the connection operator generates gate level functions in synthesis . However , stay RTL In the model , The join operator is a useful construct , Used to express hardware functions in a concise way .

Example 5-1: Use join operators : Multi input status register//`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords

module status_reg

(input logic clk, // register clk

input logic rstN, // active-low reset

input logic int_en, // 1-bit interrupt enable

input logic zero, // 1-bit result = 0 flag

input logic carry, // 1-bit result overflow flag

input logic neg, // 1-bit negative result flag

input logic [1:0] parity, // 2-bit parity bits

output logic [7:0] status // 8-bit status register output

);

timeunit 1ns; timeprecision 1ns;

always_ff @(posedge clk or negedge rstN) // async reset

if (!rstN) // active-low reset

status <= {1'b0,2'b11,5'b0}; // reset

else

status <= {int_en,2'b11,zero,carry,neg,parity}; // load

endmodule: status_reg

//`end_keywords

chart 5-1: Example 5-l Comprehensive results of : concatenation operator ( Status register )

| note |

|---|

| The way the synthesis compiler implements operators is affected by many factors , Including target devices 、 Other operators or programming statements used with operators 、 Integrated compiler used , as well as ” Specified comprehensive options and constraints . |

Example 5-1 The status register in has two unused bits , Their constant value is 1, Used to generate graphs 5-1 The synthesis compiler implemented by the status register shown in maps these two unused bits to 8 Bit pull-up output up . Other integrated compilers , Or specify different comprehensive constraints , The same... May be mapped in different ways RTL function , For example, by using the preset 1 Trigger of value

Example 5-2: Use join operators : Adder with carry//`begin_keywords "1800-2012"

module rtl_adder

(input logic a, b, ci,

output logic sum, co

);

timeunit 1ns; timeprecision 1ns;

assign {co,sum} = a + b + ci;

endmodule: rtl_adder

//`end_keywords

chart 5-2: Example 5-2 Comprehensive results of : The addition operator ( Carry / Output adder )

Used to generate graphs 5-2 The integrated compiler shown in the implementation will RTL The adder function maps to the general adder block —— The next step of integration will be specific ASIC or FPGA equipment , The general adder will be mapped to a specific adder implementation in this step .

Join and copy operators are often used to create expressions that are used as operands of other operators . Examples of this will be found later in this chapter and later chapters .

When using connections , There are some important rules to note :

You can connect any number of expressions together , Include only one expression ,

The expression in the connection must have a fixed size . Text values without size are not allowed , For example, digital 5 and ’1, It's not allowed .

The result of the connection is always unsigned , No matter what the symbol of the expression in the connection is .

Don't confuse connections with assignment lists .SystemVerilog One is contained in ’{and}( Assignment list ) Assignment list operators between tags . Although the assignment list operator looks similar to the join operator , But its functions are quite different . The assignment list operator concatenates multiple values , To create a new single value . The assignment list operator begins with an apostrophe (’), And it is used to assign a set of single values to a single element of an array or a single member of a structure .

SystemVerilog- Operator / Expression rules

边栏推荐

- Consumer unit 消费单元

- JWT token related configuration (global configuration identity authentication rewrites authenticate method)

- Inftnews | yuanuniverse shopping experience will become a powerful tool to attract consumers

- 【unity】将unity编辑c#配置为vscode

- 大页内存原理及使用设置

- Have you seen the management area decoupling architecture? Can help customers solve big problems

- [notes for question brushing] binary linked list to integer

- DRF - web development mode, API interface, API interface testing tool, restful specification, serialization and deserialization, DRF installation and use

- 追踪伦敦银实时行情的方法

- [Commons lang3 topic] 004- numberutils topic

猜你喜欢

如何给女友讲明白JS的bind模拟实现

🧐 table1 | 一秒搞定你的三线表

用CDO进行nc数据的不规则裁剪

In the second round, 1000 okaleido tiger were sold out in one hour after logging in to binance NFT again

浅谈一下跨端技术方案

DRF -- authentication, authority, frequency source code analysis, global exception handling, automatic generation of interface documents, RBAC introduction

Five interesting magic commands in jupyter notebook

B-tree~

进程和线程知识点总结1

Error reporting: Rong Lianyun sends SMS verification code message 500

随机推荐

ActiveMQ基本详解

[Commons lang3 topic] 004- numberutils topic

Have you seen the management area decoupling architecture? Can help customers solve big problems

主线程与守护线程

消费行业数字化升级成“刚需”,weiit新零售SaaS为企业赋能!

JWT token related configuration (global configuration identity authentication rewrites authenticate method)

将行内元素转换为块元素的方法

Educational Codeforces Round 132 (Rated for Div. 2)【A~C】

Error reporting: when the browser clicks the modify add button, there is no response and no error reporting. Solution

I don't recommend you use Select*

进程和线程知识点总结1

自制 | 纯手工自制一个16位RISC架构CPU

Seven marketing strategies of NFT project

如何在WordPress中创建一个自定义404错误页面

Day2:三种语言暴刷牛客130题

【刷题笔记】二进制链表转整数

[raspberry pie] how does the windows computer connect with raspberry pie

Return the member function of *this

Kwai focuses on regulating the number maintenance behavior in the ways of handling and manuscript washing, and how to purify the content ecology on the we media platform

[untitled]