当前位置:网站首页>【Verilog】HDLBits题解——Verification: Reading Simulations

【Verilog】HDLBits题解——Verification: Reading Simulations

2022-08-03 12:03:00 【wjh776a68】

Finding bugs in code

Mux

题目链接

module top_module (

input sel,

input [7:0] a,

input [7:0] b,

output [7:0] out );

assign out = ({

8{

sel}} & a) | ({

8{

~sel}} & b);

endmodule

NAND

题目链接

module top_module (input a, input b, input c, output out);//

wire out_reverse;

andgate inst1 (out_reverse, a, b, c, 1, 1);

assign out = ~out_reverse;

endmodule

Mux

题目链接

module top_module (

input [1:0] sel,

input [7:0] a,

input [7:0] b,

input [7:0] c,

input [7:0] d,

output [7:0] out ); //

wire [7:0] mux0, mux1;

mux2 mux2_0 ( sel[0], a, b, mux0 );

mux2 mux2_1 ( sel[0], c, d, mux1 );

mux2 mux2_2 ( sel[1], mux0, mux1, out );

endmodule

Add/Sub

题目链接

// synthesis verilog_input_version verilog_2001

module top_module (

input do_sub,

input [7:0] a,

input [7:0] b,

output reg [7:0] out,

output reg result_is_zero

);//

always @(*) begin

case (do_sub)

0: out = a+b;

1: out = a-b;

endcase

if (&(~out))

result_is_zero = 1;

else

result_is_zero = 0;

end

endmodule

Case Statement

题目链接

module top_module (

input [7:0] code,

output reg [3:0] out,

output reg valid=1 );//

always @(*)

case (code)

8'h45: begin out <= 0; valid <= 1; end

8'h16: begin out <= 1; valid <= 1; end

8'h1e: begin out <= 2; valid <= 1; end

8'h26: begin out <= 3; valid <= 1; end

8'h25: begin out <= 4; valid <= 1; end

8'h2e: begin out <= 5; valid <= 1; end

8'h36: begin out <= 6; valid <= 1; end

8'h3d: begin out <= 7; valid <= 1; end

8'h3e: begin out <= 8; valid <= 1; end

8'h46: begin out <= 9; valid <= 1; end

default: begin out <= 0; valid <= 0; end

endcase

endmodule

Build a circuit from a simulation waveform

Combinational circuit 1

题目链接

module top_module (

input a,

input b,

output q );//

assign q = a & b; // Fix me

endmodule

Combinational circuit 2

题目链接

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = ~(a ^ b ^ c ^ d); // Fix me

endmodule

Combinational circuit 3

题目链接

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = (c | d) & (a | b); // Fix me

endmodule

Combinational circuit 4

题目链接

module top_module (

input a,

input b,

input c,

input d,

output q );//

assign q = c | b; // Fix me

endmodule

Combinational circuit 5

题目链接

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output [3:0] q );

reg [3:0] q_reg;

assign q = q_reg;

always @ (*) begin

case(c)

0: q_reg = b;

1: q_reg = e;

2: q_reg = a;

3: q_reg = d;

default: q_reg = 'hf;

endcase

end

endmodule

Combinational circuit 6

题目链接

module top_module (

input [2:0] a,

output [15:0] q );

reg [15:0] q_reg;

assign q = q_reg;

always @ (*) begin

case(a)

0: q_reg = 'h1232;

1: q_reg = 'haee0;

2: q_reg = 'h27d4;

3: q_reg = 'h5a0e;

4: q_reg = 'h2066;

5: q_reg = 'h64ce;

6: q_reg = 'hc526;

7: q_reg = 'h2f19;

endcase

end

endmodule

Sequential circuit 7

题目链接

module top_module (

input clk,

input a,

output q );

always @ (posedge clk) begin

q <= ~a;

end

endmodule

Sequential circuit 8

题目链接

module top_module (

input clock,

input a,

output p,

output q );

reg q_reg = 0;

reg p_reg = 0;

assign p = p_reg;

assign q = q_reg;

always @ (*) begin

if(clock)

p_reg <= a;

end

always @ (negedge clock) begin

q_reg <= a;

end

endmodule

Sequential circuit 9

题目链接

module top_module (

input clk,

input a,

output [3:0] q );

reg [3:0] q_reg;

assign q = q_reg;

always @ (posedge clk) begin

if (a) begin

q_reg <= 4;

end

else begin

q_reg <= (q_reg + 1) % 7;

end

end

endmodule

Sequential circuit 10

题目链接

module top_module (

input clk,

input a,

input b,

output q,

output state );

reg state_reg;

assign state = state_reg;

assign q = a ^ b ^ state;

always @ (posedge clk) begin

state_reg <= (a & b) | (a & state_reg) | (b & state_reg);

end

endmodule

边栏推荐

猜你喜欢

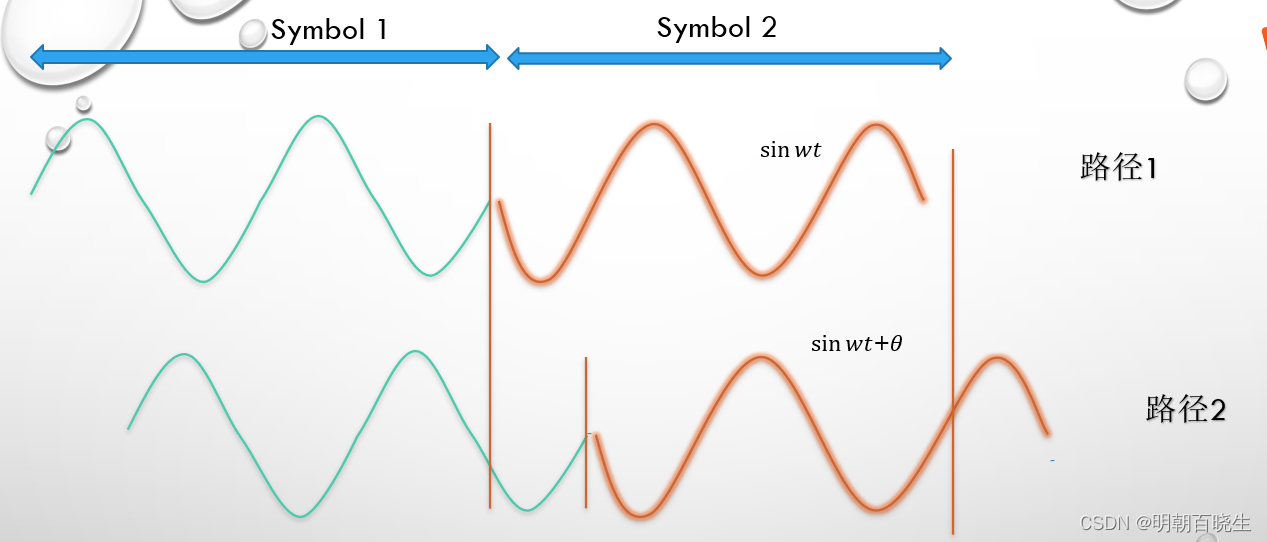

OFDM 十六讲 4 -What is a Cyclic Prefix in OFDM

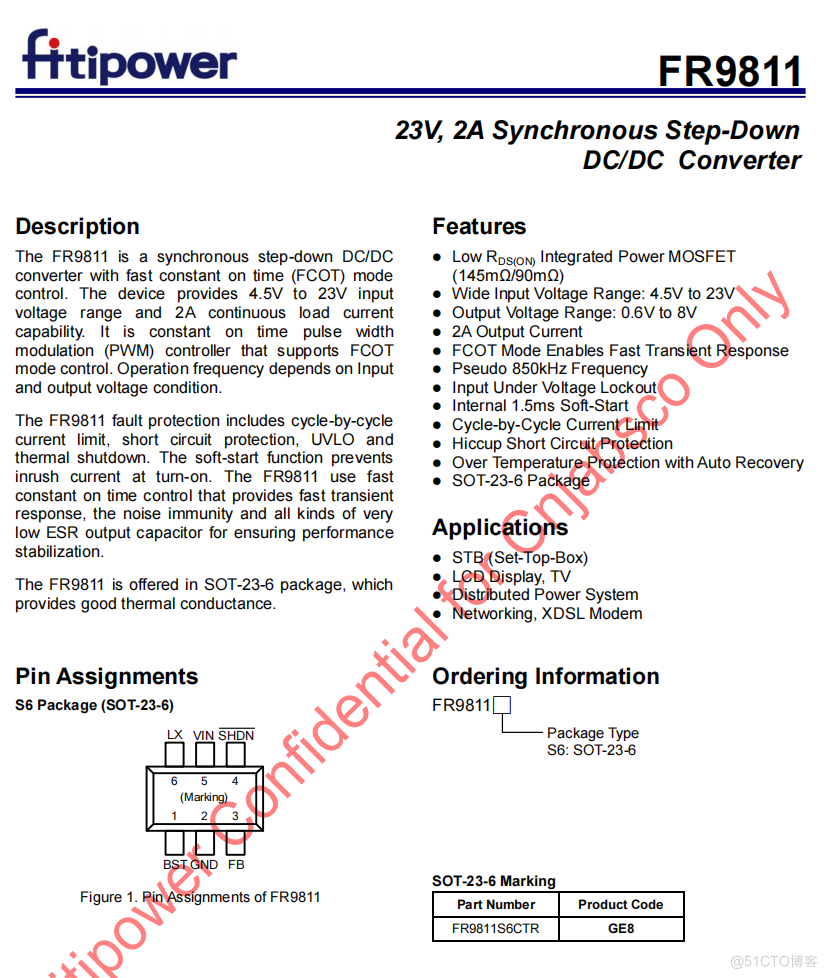

FR9811S6 SOT-23-6 23V, 2A Synchronous Step-Down DC/DC Converter

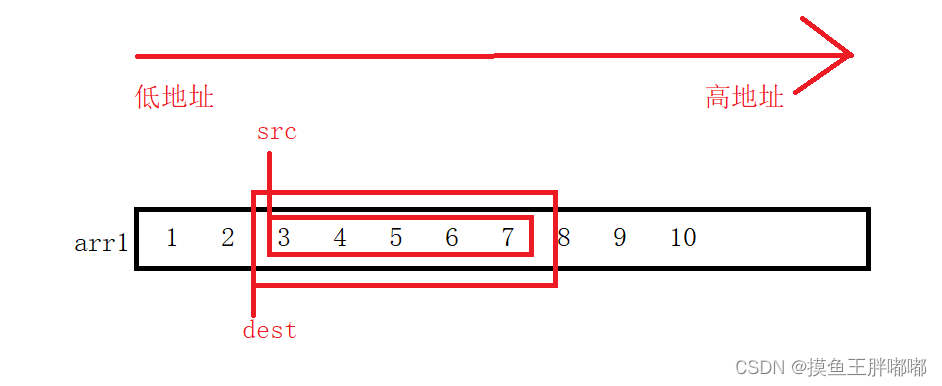

C language advanced article: memory function

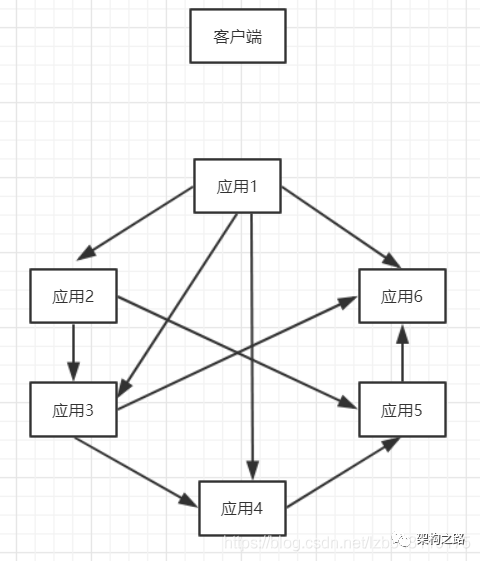

面试官:SOA 和微服务的区别?这回终于搞清楚了!

码率vs.分辨率,哪一个更重要?

微信为什么使用 SQLite 保存聊天记录?

性能优化|从ping延时看CPU电源管理

深度学习中数据到底要不要归一化?实测数据来说明!

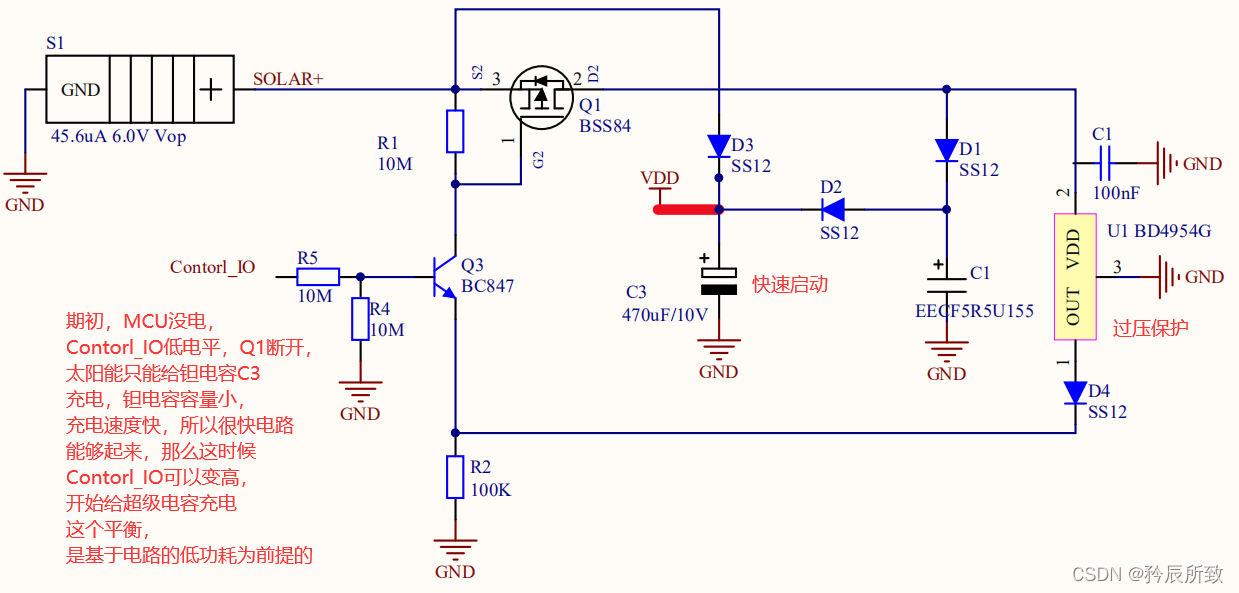

分享一款实用的太阳能充电电路(室内光照可用)

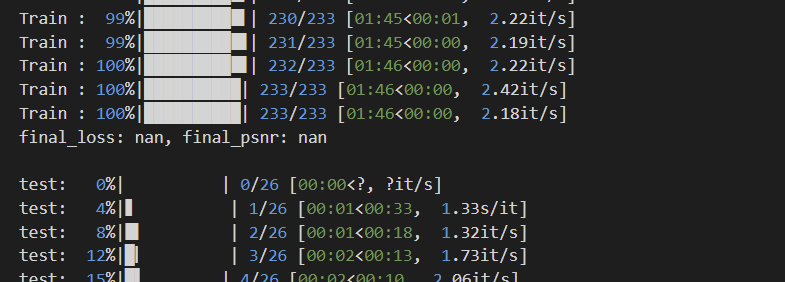

深度学习跟踪DLT (deep learning tracker)

随机推荐

Explain the virtual machine in detail!JD.com produced HotSpot VM source code analysis notes (with complete source code)

awk入门教程

一文带你弄懂 CDN 技术的原理

899. 有序队列 : 最小表示法模板题

Vs 快捷键---探索不一样的编程

[论文阅读] (23)恶意代码作者溯源(去匿名化)经典论文阅读:二进制和源代码对比

面试官:SOA 和微服务的区别?这回终于搞清楚了!

【一起学Rust】Rust学习前准备——注释和格式化输出

87.(cesium之家)cesium热力图(贴地形)

第四课 标识符、关键字、变量、变量的分类和作用域、常量

本周四晚19:00知识赋能第4期直播丨OpenHarmony智能家居项目之设备控制实现

Matlab学习11-图像处理之图像变换

微信小程序获取手机号

SmobilerService 推送实现

《数字经济全景白皮书》金融数字用户篇 重磅发布!

深度学习中数据到底要不要归一化?实测数据来说明!

622. 设计循环队列

ssh 免密登录了解下

一次内存泄露排查小结

Blazor Server(6) from scratch--policy-based permission verification