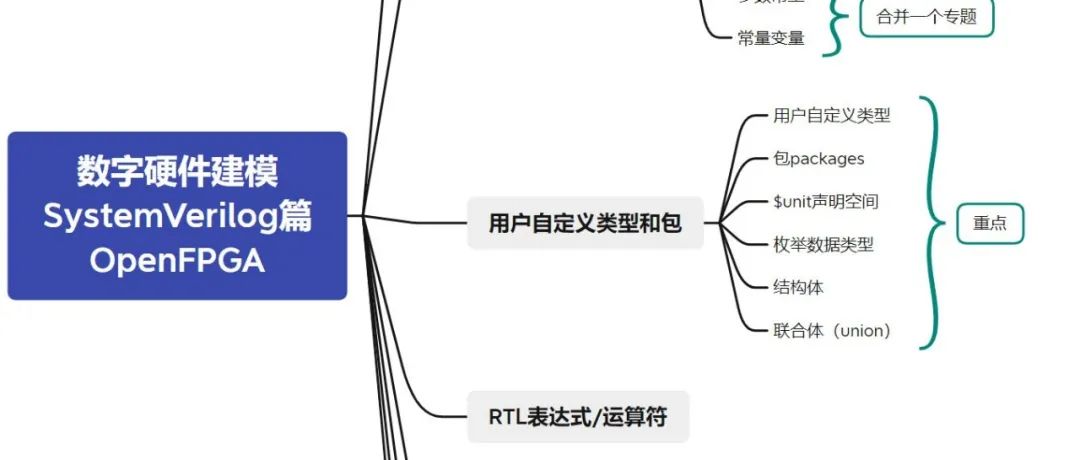

当前位置:网站首页>SystemVerilog structure (II)

SystemVerilog structure (II)

2022-07-01 16:49:00 【Broken thoughts】

Digital hardware modeling SystemVerilog- Structure ( Two )

Structure

Structs are used to combine multiple variables under a common name . Designs usually have logical signal groups , For example, the control signal of the bus protocol , Or signals used in the state controller . The struct provides a way to bundle these related variables together . All variables in the structure can be assigned a single value , Or each variable can be assigned a value separately . A structure package can be copied to another structure with the same definition , And through the module port 、 Task or function in and out .

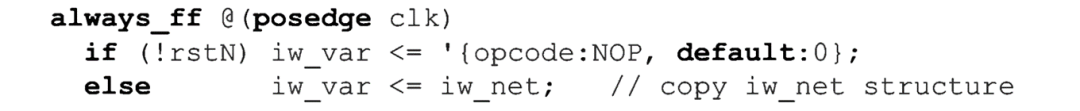

Structure replication

One custom structure can be copied to another , As long as these two structures are declared from the same custom structure definition . The following example uses the structure definitions and declarations shown in the previous section .

Anonymous structures cannot be copied as a whole , But you can copy one member at a time :

Compressed and uncompressed structures

By default , The structure will be uncompressed . This means that members of the structure are treated as independent variables or constants , And grouped together under a common name .SystemVerilog It does not specify how software tools should store members of uncompressed structures . Different software tools have different storage distribution for structures .

By using keywords packed, Explicitly declare the structure as a compressed structure .

The compressed structure stores all members of the structure as continuous bits in the same form as the vector . The first member of the structure is the leftmost field of the vector . The rightmost bit of the last member in the structure is the least significant bit of the vector , The number is bit 0. Pictured 4-2 Shown .

chart 4-2: Compressed structure stored as vector

chart 4-2: Compressed structure stored as vector All members of a compressed structure must be integer values . Integer values are values that can be expressed as vectors , for example byte、int And use bit or logic Vector created by type . If any member of the structure cannot be expressed as a vector , Then the structure cannot be compressed . This means that compressed structures cannot contain real or short real variables 、 Incompressible structure 、 An uncompressed union or an uncompressed array .

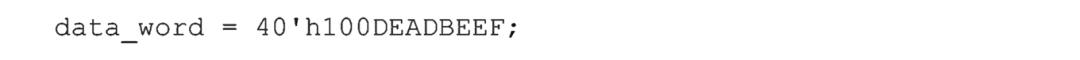

Reference compressed structure and structure members . Compressed structures can be copied , Or assign a list of structural expression values , The method is the same as that of an uncompressed structure . Members of compressed structures can be referenced by member names , The method is the same as that of an uncompressed structure .

The compressed structure can also be regarded as a vector . therefore , In addition to structure allocation , Vector values can also be assigned to compressed structures

Vector assignment is legal , Because the structure members on the left of the assignment have been compressed together , Form a continuous set of bits , In the same way as vectors . Because the compressed structure is stored as a continuous set of bits , Therefore, it is also legal to perform vector operations on compressed structures , Including bit selection and partial selection . The following two assignments will be assigned to data_word Of tag member :

Mathematical operations that can be performed on vectors 、 Logical operations and any other operations can also be performed on compressed structures .

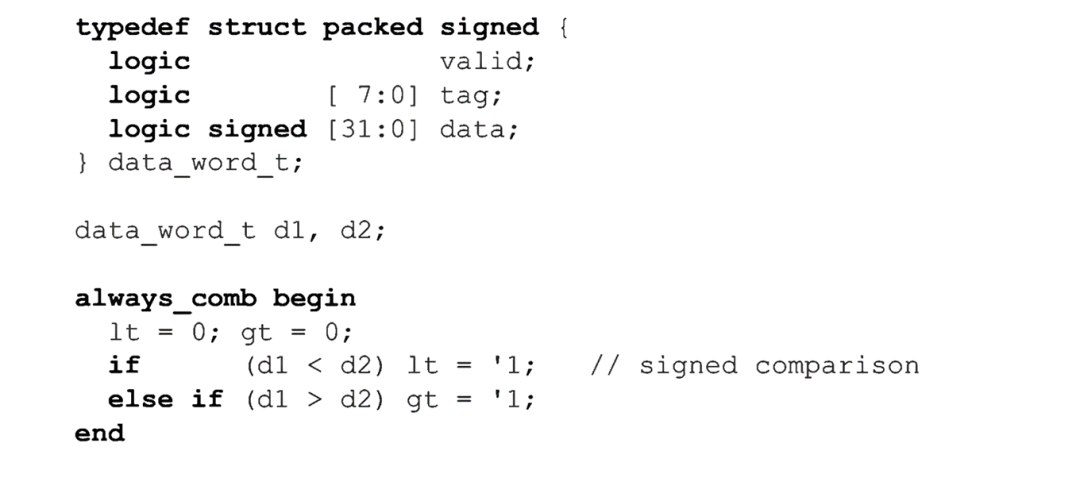

Signed compressed structure . Compressed structure can be used signed and unsigned Keyword declaration . When used as a vector in operations or relational operations , These modifiers will affect the recognition method of the whole structure . They will not affect the way the structure members are identified . Each member of the structure is considered to be signed or unsigned , It depends on the type declaration of the member . The partial selection of compressed structure is unsigned , Same as partial selection of vector .

Pass the structure through the port

Custom structures can be passed through the ports of modules and interfaces , The structure must first use typedef Define user-defined data types , Then it is allowed to declare the port of the module or interface as the structure type .

Uncompressed structures must be custom structures , Can the structure be passed through the port . The connection with the port must be a structure exactly the same as the port type . in other words , The port and the connections on both sides of the port must be from the same typedef Definition statement . This limitation applies only to uncompressed structures . The compressed structure through the module port is regarded as a vector . The external connection of the port can be the same type of compressed structure , It can also be any type of vector .

By declaring task or function parameters as struct types , Custom structures can also be passed to tasks or functions as parameters .

When calling a task or function , If the task or function has an uncompressed structure as a formal parameter menu , Then a structure of exactly the same type must be passed to the task or function . The formal parameters of compressed structure are regarded as vectors , Can be passed to any type of vector .

Conventional Verilog And the structure

The original Verilog Language does not have a convenient mechanism to collect common signals into a group . In traditional Verilog Style model , Engineers must use a special grouping method , For example, naming conventions , Each signal in one group starts or ends with a set of common characters . The original Verilog Language also cannot pass signal sets through module ports or tasks and functions , Each signal must be transmitted through a separate port or parameter .

In primitive Verilog Adding structures to a language is a powerful RTL Modeling construction , vice versa . It provides a more concise 、 More intuitive 、 More reusable complex model function modeling method . The custom structure defined in the package can be reused in multiple modules , It can also be used for verification RTL The model is reused in the validation test bench .

Comprehensive guidance

Both uncompressed and compressed structures can be integrated . The integrated tool supports the structure to pass through the module port , It also supports passing to tasks and functions as input or output , It also supports assigning values to structures using a list of member names and values .

Synthetic compilers may optimize uncompressed structures better than compressed structures . Uncompressed structures allow software tools to determine the best way to store or implement each structure member , The compressed structure determines how to organize each member .

SystemVerilog- Structure ( One )

边栏推荐

- Research and investment strategy report of China's sodium sulfate industry (2022 Edition)

- Golang爬虫框架初探

- 求求你们,别再刷 Star 了!这跟“爱国”没关系!

- 想做软件测试的女孩子看这里

- FPN网络详解

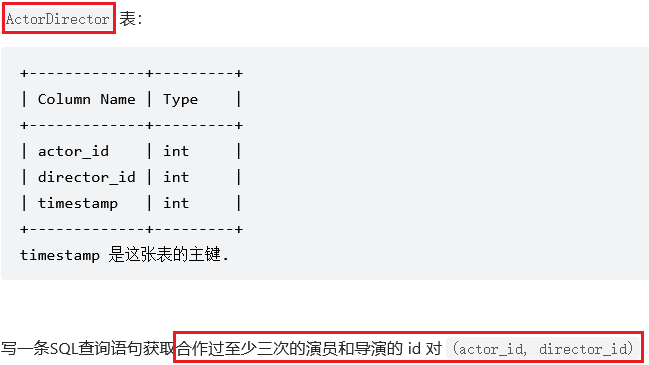

- sql刷题1050. 合作过至少三次的演员和导演

- China nylon 11 industry research and future forecast report (2022 Edition)

- 独家消息:阿里云悄然推出RPA云电脑,已与多家RPA厂商开放合作

- AI college entrance examination volunteer filling: the gods of Dachang fight, and candidates pay to watch

- Stonedb is building blocks for domestic databases, and the integrated real-time HTAP database based on MySQL is officially open source!

猜你喜欢

Tutorial on principles and applications of database system (006) -- compiling and installing MySQL 5.7 (Linux Environment)

你还在用收费的文档管理工具?我这有更牛逼的选择!完全免费

Stegano in the world of attack and defense

![[nodemon] app crashed - waiting for file changes before starting... resolvent](/img/ee/9830afd86e092851a2a906cb994949.png)

[nodemon] app crashed - waiting for file changes before starting... resolvent

What is the effect of choosing game shield safely in the game industry?

数据库系统原理与应用教程(006)—— 编译安装 MySQL5.7(Linux 环境)

sql刷题1050. 合作过至少三次的演员和导演

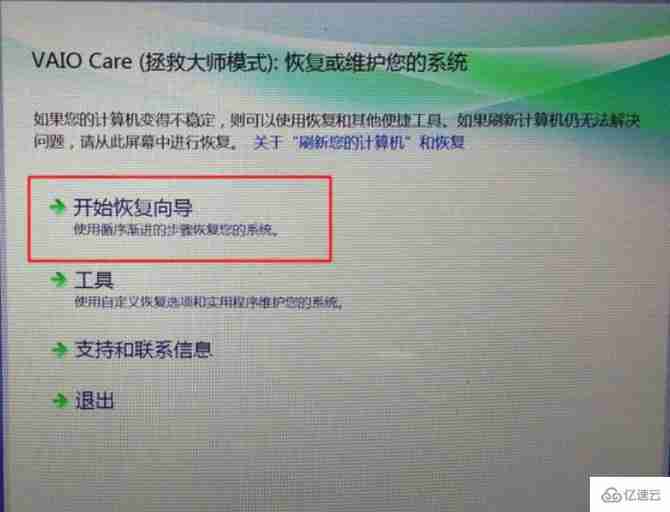

How to restore the system of Sony laptop

Apple's self-developed baseband chip failed again, which shows Huawei Hisilicon's technological leadership

VMware 虚拟机启动时出现故障:VMware Workstation 与 Hyper-v 不兼容...

随机推荐

Graduation season | Huawei experts teach the interview secret: how to get a high paying offer from a large factory?

The sharp drop in electricity consumption in Guangdong shows that the substitution of high-tech industries for high-energy consumption industries has achieved preliminary results

【PyG】文档总结以及项目经验(持续更新

Endeavouros mobile hard disk installation

嗨 FUN 一夏,与 StarRocks 一起玩转 SQL Planner!

Alibaba cloud, Zhuoyi technology beach grabbing dialogue AI

红队第8篇:盲猜包体对上传漏洞的艰难利用过程

阿里云、追一科技抢滩对话式AI

C语言输入/输出流和文件操作

判断链表是否是回文链表

sql刷题586. 订单最多的客户

数据库系统原理与应用教程(003)—— MySQL 安装与配置:手工配置 MySQL(windows 环境)

Example of vim user automatic command

Rhcsa Road

Germany if was crowned with many awards. How strong is this pair of headphones? In depth evaluation of yinpo GTW 270 hybrid

P2592 [zjoi2008] birthday party (DP)

Origin2018安装与使用(整理中)

EndeavourOS移动硬盘安装

How to cancel automatic search and install device drivers for laptops

你还在用收费的文档管理工具?我这有更牛逼的选择!完全免费