当前位置:网站首页>Continuous assignment of Verilog procedure

Continuous assignment of Verilog procedure

2022-07-02 03:09:00 【Da Xi】

Verilog Processes are continuously assigned values

key word :deassign,force,release

Process continuous assignment is a kind of process assignment . This assignment statement can replace all other wire or reg Assignment , Rewrite the wire or reg Current value of type variable .

Unlike process assignment , The expression of process continuous assignment can be continuously driven to wire or reg In type variable , That is, when the continuous assignment of the process takes effect , The change of any operand in the right-hand expression will cause the re execution of the continuous assignment statement of the procedure .

Process continuity assignment mainly includes 2 Kind of ,assign-deassign and force-release.

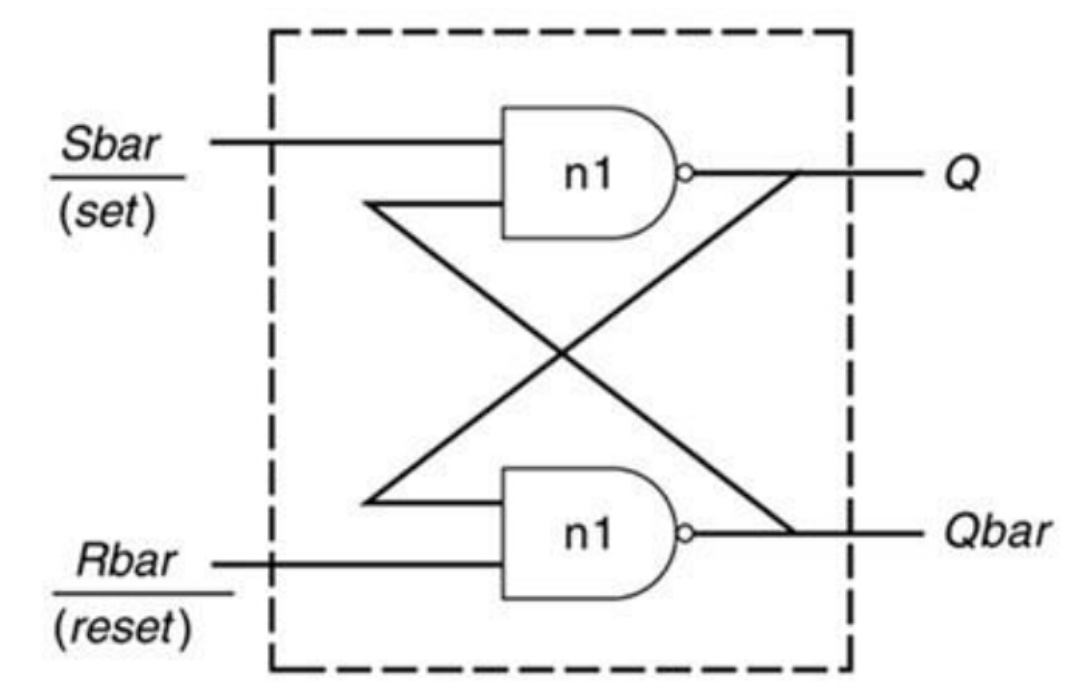

assign, deassign

assign( Procedure assignment operation ) And deassign ( Cancel process assignment ) Represents the continuous assignment statement of the first kind of procedure . Assignment objects can only be registers or register groups , And can't be wire Type variable .

Continuous assignment of registers during assignment , The value in the register is retained until it is reassigned .

for example , One with reset end D Triggers can be described with the following code :

example

module dff_normal(

input rstn,

input clk,

input D,

output reg Q

);

always @(posedge clk or negedge rstn) begin

if(!rstn) begin //Q = 0 after reset effective

Q <= 1'b0 ;

end

else begin

Q <= D ; //Q = D at posedge of clock

end

end

endmodule

below , use assign And deassign rewrite , Do the same thing .

That is, when the reset signal is 0 when ,Q End quilt assign Statement assignment , Always output as 0.

Reset signal is 1 when ,Q End quilt deassign Statement unassign , It is reassigned on the rising edge of the clock .

example

module dff_assign(

input rstn,

input clk,

input D,

output reg Q

);

always @(posedge clk) begin

Q <= D ; //Q = D at posedge of clock

end

always @(negedge rstn) begin

if(!rstn) begin

assign Q = 1'b0 ; //change Q value when reset effective

end

else begin //cancel the Q value overlay,

deassign Q ; //and Q remains 0-value until the coming of clock posedge

end

end

endmodule

force, release

force ( Force assignment ) And release( Cancel forced assignment ) Represents the continuous assignment statement of the second kind of procedure .

Application method and effect , and assign And deassign similar , But the assignment object can be reg Type variable , It can also be wire Type variable .

Because it is unconditionally mandatory assignment , It is generally used for interactive debugging process , Do not use in the design module .

When force When acting on a register , The current value of the register is overwritten ;release The register value will continue to retain the value at the time of forced assignment . after , The value of this register can be changed by the original procedure assignment statement .

When force When online , The network value will also be forcibly assigned . however , once release The network type variable , Its value immediately becomes the original driving value .

For intuitive observation of the difference between the forced assignment of two types of variables , Use the counters in Section 1 counter10 As a design module ,testbench The design is as follows .

example

`timescale 1ns/1ns

module test ;

reg rstn ;

reg clk ;

reg [3:0] cnt ;

wire cout ;

counter10 u_counter (

.rstn (rstn),

.clk (clk),

.cnt (cnt),

.cout (cout));

initial begin

clk = 0 ;

rstn = 0 ;

#10 ;

rstn = 1'b1 ;

wait (test.u_counter.cnt_temp == 4'd4) ;

@(negedge clk) ;

force test.u_counter.cnt_temp = 4'd6 ;

force test.u_counter.cout = 1'b1 ;

#40 ;

@(negedge clk) ;

release test.u_counter.cnt_temp ;

release test.u_counter.cout ;

end

initial begin

clk = 0 ;

forever #10 clk = ~ clk ;

end

//finish the simulation

always begin

#1000;

if ($time >= 1000) $finish ;

end

endmodule // test

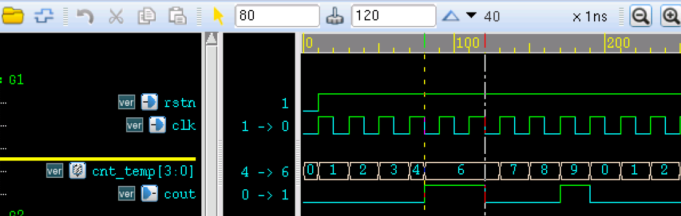

The simulation results are as follows .

It can be seen from the picture that , stay cnt_temp be equal to 4 when (80ns), cnt_temp Is forcibly assigned to 6,cout Is forcibly assigned to 1.

release when (120ns), cnt_temp Register type , Keep the original value unchanged , Until the rising edge of the clock is added and assigned , Value becomes 7 .

and 120ns when , because cout Is the wire network variable , Its value cannot be saved . Original code counter10 There are driver statements in the model : assign cout = (cnt_temp==4'd9) , therefore cout Value to 0 .

边栏推荐

- [staff] restore mark (Introduction to the use of restore mark | example analysis of Metaphone mark and restore mark)

- West digital decided to raise the price of flash memory products immediately after the factory was polluted by materials

- Verilog wire type

- 小米青年工程师,本来只是去打个酱油

- Share the basic knowledge of a common Hongmeng application

- C shallow copy and deep copy

- /silicosis/geo/GSE184854_ scRNA-seq_ mouse_ lung_ ccr2/GSE184854_ RAW/GSM5598265_ matrix_ inflection_ demult

- Intersection of Venn graph

- Apple added the first iPad with lightning interface to the list of retro products

- 3124. Word list

猜你喜欢

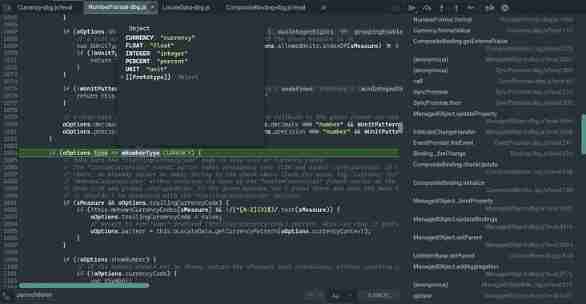

Formatting logic of SAP ui5 currency amount display

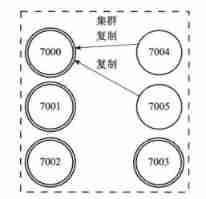

Redis cluster

Verilog avoid latch

Cache processing scheme in high concurrency scenario

Xiaomi, a young engineer, was just going to make soy sauce

批量检测url是否存在cdn—高准确率

2022-2028 global aluminum beverage can coating industry research and trend analysis report

STM32__05—PWM控制直流电机

Baohong industry | 6 financial management models at different stages of life

Batch detect whether there is CDN in URL - high accuracy

随机推荐

结婚后

[JSON] gson use and step on the pit

結婚後

Face++ realizes face detection in the way of flow

2022-2028 global manual dental cleaning equipment industry research and trend analysis report

2022 hoisting machinery command examination paper and summary of hoisting machinery command examination

Remote connection to MySQL under windows and Linux system

跟着CTF-wiki学pwn——ret2shellcode

流线线使用阻塞还是非阻塞

PHP notes - use Smarty to set public pages (include, if, else, variable settings)

Golang configure export goprivate to pull private library code

图扑软件通过 CMMI5 级认证!| 国际软件领域高权威高等级认证

Pychart creates new projects & loads faster & fonts larger & changes appearance

Qualcomm platform wifi-- WPA_ supplicant issue

QT implementation interface jump

2022 hoisting machinery command examination paper and summary of hoisting machinery command examination

STM32__ 05 - PWM controlled DC motor

Verilog 时序控制

Connected block template and variants (4 questions in total)

【JVM】创建对象的流程详解